飛騰愛好者技術交流群碼公眾號“烏拉大喵喵” 本文已錄製講解視頻發佈到B站,可以搜索UP主“烏拉大喵喵” 或者掃二維碼進入B站專輯進行查看: 一、啥是自主可控 國產CPU現在廠家細算起來其實有很多,現在華為、小米也在做自己的CPU,瑞芯微、全志等的SoC現在也是廣泛應用。但是真正能叫做自主可控的CPU ...

飛騰愛好者技術交流群碼 公眾號“烏拉大喵喵”

公眾號“烏拉大喵喵”

本文已錄製講解視頻發佈到B站,可以搜索UP主“烏拉大喵喵”

或者掃二維碼進入B站專輯進行查看:

一、啥是自主可控

國產CPU現在廠家細算起來其實有很多,現在華為、小米也在做自己的CPU,瑞芯微、全志等的SoC現在也是廣泛應用。但是真正能叫做自主可控的CPU廠商,只有6家。那啥是自主可控?首先來不嚴謹的講下現在數字晶元是怎麼做的設計。FPGA大家都知道,可以通過Verilog或者VHDL等硬體編程語言實現硬體功能。比如,我要實現一個SPI控制8個LED燈的功能,可能從市面上找這種功能的晶元是沒有的,那麼我就可以自己指定控制LED的指令,通過使用FPGA自己編成,解析SPI傳下來的指令,控制LED的亮滅。如果測試驗證沒有問題,那麼就可以把FPGA的RTL拿出來,經過處理拿去流片,流片完成給晶元起個名字,比如YKS2D8001,這就成為了市面上能夠實現SPI介面控制8個LED的ASIC晶元了。同時,咱們FPGA的實現代碼,也可以拿出來當成一個IP,以後誰要想使用FPGA來實現這個功能的時候,就可以拿來用而不用再單獨購買咱們流片完成的ASIC晶元YKS2D8001。

那麼,咱們在做複雜功能FPGA的時候,比如xilinx的,咱們會調用xilinx提供的現成的IP,比如它的DDR控制器IP、PCIe IP或者更簡單些的串口IP、IIC IP。這些IP咱們在程式實現時,是可以直接調用,根據xilinx提供的操作手冊把這個IP給用起來的,但是這個IP核的實現代碼,咱們是看不到的,如果咱們想改IP核內的代碼,那肯定是沒辦法的。這就是非自主可控。自主可控,就是能夠掌握IP的所有代碼,自己想改就改。

飛騰就是國內自主可控6家之一。也就是可以簡單的理解為飛騰晶元內的每行代碼,每一個功能實現,都是自己實現的。這裡有人會說,飛騰不是arm64的麽,那是arm的呀。是的,飛騰是arm64的,但是飛騰是購買的arm的指令集授權。指令集授權大家可以通俗的認為就是購買了函數名,但是函數實現是自己做的。所以即使是arm64,也是自主可控的。

二、基於飛騰晶元的設計

2.1 最小系統硬體設計

要想讓飛騰CPU加電後跑起來,硬體設計上有幾個部分是必須有的。時鐘、供電、記憶體、調試串口、QSPI Flash介面、存儲。下麵就針對每個部分詳細說一下。

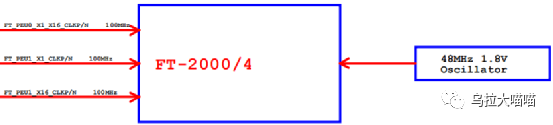

2.1.1 時鐘

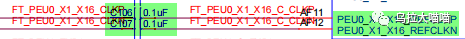

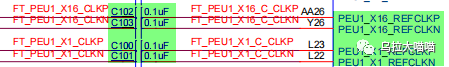

時鐘不用多說,所有的晶元都需要時鐘。飛騰晶元需求的時鐘主要就是兩種,1是晶元的主時鐘48MHz,2就是晶元的PCIe控制器PEU的時鐘100MHz。這個100MHz時鐘要求PEU和外設同源,也就是從同一個時鐘發生器產生,HSCL電平標準,AC耦合。並且設計時,即使PEU不用,PCIe時鐘也是要接的。

圖 CPU總的時鐘框圖

圖 PEU0的時鐘

圖 PEU1的時鐘

2.1.2 供電和電源管理

飛騰的電源種類並不多,需要0.8V(核電)、1.2V(VDDQ)、1.8V(IO)三種。其他電源域基本都可以直連或者通過磁珠連接到這三個電源中,這裡就參考demo設計就可以了。

這裡需要提示的是:

1.就近放置在晶元電源管腳下的電容為4.7uF,這裡儘量不要修改。

2.CPU有一個3.3V的電源管腳,這裡給供一個3.3V過來即可。

3.各個電的最大電流一定要查手冊,設計電源時一定要保證滿足。

4.各個電的紋波不能超5%。註意,這裡說的是整個運行狀態下,就是BIOS階段、OS系統啟動和運行階段,是都不能超的。這裡特別強調,非常重要!

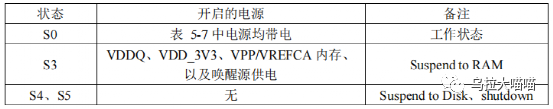

說到電源,就不得不說電源管理。借鑒x86的電源管理狀態,飛騰CPU也有電源管理的幾個狀態。

圖 飛騰CPU電源狀態

S0就是正常工作的狀態,S3就是類似window的睡眠,即待機狀態壓到記憶體中,所以要求記憶體一直帶電。S4/S5就是類似window的休眠和關機,即待機狀態壓到硬碟,或者就是直接關機了,這個時候整板都會掉電。

那麼有人問了,S4/S5是倆狀態呀?一個是休眠系統狀態壓到硬碟,一個是關機,這倆放一起咋區分呢?其實不用區分,系統狀態壓到硬碟了,就已經是被固定保存了,即使掉電也不會有數據丟失,這裡應該沒錯吧。所以對於電源管理來說,S4/S5狀態時都是要掉電的。那麼S4、S5的區別,主要在下一次開機時。如果去看系統下去執行休眠和關機時的log信息,可以看出,休眠和關機系統處理是不同的,他們會置不同的標誌。那麼在下次開機的時候,這個置的標誌,就能夠告知系統要從哪種狀態啟動。

到這裡,供電和電源管理的幾個狀態應該就說清了,那麼現在實際問題來了,供電我能明白,就是使用電源晶元供電嘛。那麼這個電源管理,我咋做?

那麼下麵,我們就一個一個的來說。

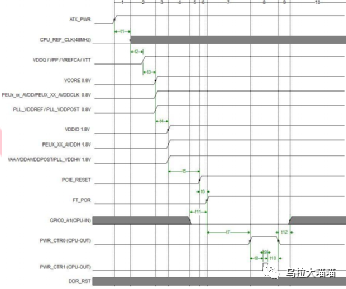

首先,我們一個板子肯定是從未加電狀態轉為加電狀態,讓CPU跑起來。那麼對應上面的狀態,那就是S4/S5狀態到S0狀態,也就是斷電關機狀態到上電工作狀態。這個狀態的控制,其實就是對CPU各個電源域上電時序的控制。所以,做硬體不用想太多,從未加電到加電讓CPU跑起來,換句話說就是從S4/S5狀態到S0狀態的實現,就是你想辦法把你給CPU的各個電按下麵時序跑完就好了。在保證電路設計的情況下哈,只要你按時序跑完,CPU肯定就啟動了,也就到了S0階段。

圖 S4/S5到S0開機時序圖

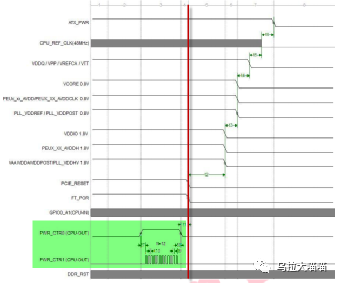

那麼,你能猜到了吧,S0到S4/S5是咋弄,其實也一樣,也是跑電時序。但是……硬體工程師又問了,板子系統正好好的跑著呢,我咋知道要去跑掉電時序呢?這個問題問的很好。去執行掉電時序,總是要收到信號的,那麼這個信號在時序圖中是能夠看出來的,就是圖中標綠的部分。PWR_CTR0、PWR_CTR1這兩個是CPU晶元上的兩個管腳,當我們在OS系統下點了休眠或者關機命令時,系統肯定是要先去保存自己的狀態到硬碟,當保存完了,OS會通過PWR_CTR0、PWR_CTR1這兩個管腳,發送脈衝出來(應該是4脈衝代表重啟,8脈衝代表轉S3狀態,12脈衝代表轉S4/S5狀態),告訴外邊可以去跑掉電時序了。外邊收到這個脈衝後,自己根據掉電時序去跑就可以了。

圖 S0到S4/S5關機時序圖

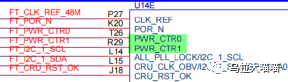

圖 PWR_CTR0、PWR_CTR1兩管腳

前面提到了PWR_CTR0、PWR_CTR1這兩個管腳把脈衝發給外邊,那麼這個外邊是啥呢?這裡外邊其實就是個控制器,單片機也好,CPLD也好,只要能夠數脈衝,能夠控電時序就好了。Demo圖一般用的都是CPLD。

圖 demo圖一般都是用CPLD做電源管理

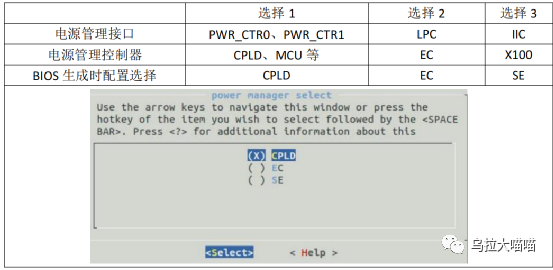

那麼又有人問了,我做筆記本難道還需要上一個CPLD控制電源麽,一般筆記本都有EC呀,EC能用麽?答案當然是肯定的。所以這裡又要說明一個事情,電源管理介面不只有上面PWR_CTR0、PWR_CTR1這兩管腳,也可以通過LPC,也可以通過IIC。要是外邊電源管理控制器使用CPLD或者MCU等,那麼建議就接到CPU PWR_CTR0、PWR_CTR1這兩管腳,通過數脈衝去判斷要執行的狀態跳轉。要是使用EC的話,就要求把EC接到CPU的LPC介面上,通過LPC去通信狀態跳轉。要是用飛騰的套片X100做電源管理,就要求把CPU的IIC1接到X100的IIC上。那麼OS系統在發送狀態跳轉的時候是怎麼知道外邊接的是什麼,要從哪個介面去傳輸命令呢,這個就是在BIOS生成的時候,有個配置選項,來告訴OS系統我外邊接的什麼。

表 不同電源管理控制器使用的通訊介面和配置方式

涉及S3狀態,有個管腳要特別說明一下:GPIO0_A1,這個腳的使用一定要好好看下手冊說明。當主機從S3恢復到S0狀態時,板上的CPLD控制單位會通過信號引腳 K17(信號名 UART_0_CTS_N/GPIO0_A1)向CPU發送主板當前的是否滿足S3→S0狀態的S3_OK信號。S3_OK 信號為高電平時候,表示可以正常恢復到S0。S3_OK信號為低時,通知CPU主板出現異常狀態(記憶體掉電等情況),系統將重新啟動,而不是從 S3 恢復。如果設計上沒有S3的需求,那麼這個GPIO0_A1要做拉低處理,不能不管,要不會出錯的。

2.1.3 記憶體

飛騰CPU的記憶體控制器做的還是比較好的,如果設計沒有硬傷,走線沒有太差,不管使用記憶體條還是DDR顆粒,都會得到一個很好的訓練參數支撐系統的運行。

首先要說的是,飛騰桌面CPU,FT-2000/4是支持DDR3和DDR4的,到D2000晶元是只支持DDR4的。這些內容在晶元手冊中都有說明,這裡特別拿出來提醒大家一下。

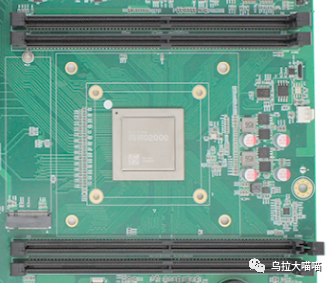

晶元是有兩個DDR控制器的,我們可以稱為兩個通道。每個控制器有4個片選信號,我們可以叫做4rank。所以,我們一個CPU最大的設計是這樣的:2個通道×4rank。像下圖一樣的設計,就可以插4條雙rank的記憶體條。

圖 雙通道×4rank的D2000板卡

記憶體控制器若按照 8bit 劃分為一個 slice,一個通道 72bit 可劃分為 9 個 slice(第9個,即slice[8]為ECC)。

DQ交換:在進行X8相容記憶體的設計時,slice內部的8個DQ可以自由互換。

Slice交換:slice[0:7]可以進行slice之間交換。Slice[8]為ECC用途,不能與其它slice交換。若用戶需要使用ECC的記憶體條,slice[8]必須與DIMM條上的slice [8]進行連接。若確認無需ECC功能,將slice [8]信號浮空即可。

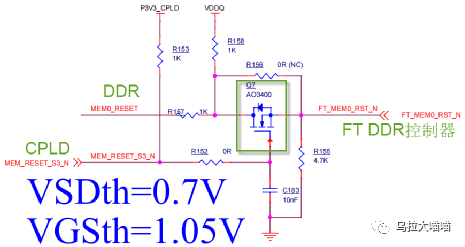

這裡還有個特別說明的地方,就是DDR控制器有個MEMRESET,這個是輸出到DDR上給DDR做複位的。前面在供電和電源管理章節里提到過,S3狀態是需要將待機狀態壓到記憶體的,那麼待機時就要求DDR不能掉電,當然更不能被覆位。因為S3狀態下除了DDR,包括CPU在內的其他無用的電都是需要被關閉的,那麼CPU這個MEMRESET一定是個無效的狀態。所以,如果我們的板卡應用會有S3,也就是睡眠狀態的,這個MEMRESET就需要控制一下。

這個就是demo圖中的這個電路。可以看到,CPU輸出的MEM_RST是過了一個MOS的,這個MOS的控制端是接到了CPLD上,因為是不是從S0跳轉到S3狀態,CPLD是可以通過PWR_CTR0、PWR_CTR1這兩個腳數脈衝來知道的,那麼它也就知道是否需要控制MOS將CPU輸出的MEM_RST傳遞給DDR。

圖 demo圖中S3狀態對於MEMRESET的處理

2.1.4 調試串口

調試飛騰,要是不把調試串口引出來,那基本就等死就完了。

UART 介面電平為 1.8V CMOS 電平標準,若使用的外設不兼 容 1.8V CMOS 電平,需進行電平轉換;預設UART_1為系統調試串口,用於輸出系統列印信息,波特率115200bps。記住,這玩意兒預設就是串口1,不能改。你要非得改,要動的代碼千千萬,還不是你自己能改的了的,何必動它呢。你就用串口1就行了。

是用TTL還是RS232,根據硬體需求自己設計就好。

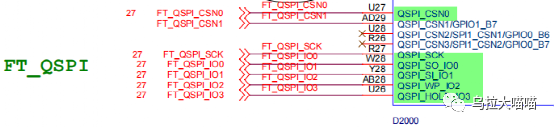

2.1.5 QSPI介面

前面提到好幾次CPU的BIOS,那麼BIOS存放在哪?CPU啟動的時候從哪裡讀呢?

都是從QSPI介面。QSPI 介面相容 SPI,且作為啟動載入片外固件的唯一介面。CPU 啟動後,最先通過 QSPI 介面的 QSPI_CSN0 片選的 Flash 晶元載入固件,來執行相關指令。固件正常執行完成,才能在後面引導OS系統啟動。

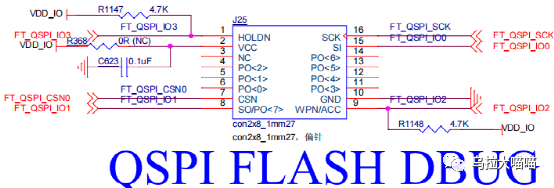

圖 QSPI flash介面電路

QSPI Flash有16pin的、8pin的,1.8V的、3.3V的。設計時選取根據要自身的需求。並且最好選取大家常用的,飛騰相容適配過的型號,同時建議flash最好16MB以上,8MB有的用起來還是小,會有問題。

2.1.6 存儲

這裡存儲是個廣義的概念,也就是所有能存放OS的都可以叫做存儲,SD卡、NVME、SATA、NOR Flash都可以。他們作為OS存儲的要求很簡單,只要能放得下OS,能被固件讀寫就可。

一般咱們PC機都是用SATA硬碟作為存儲介質,飛騰CPU上沒有sata介面,如果要用sata硬碟做存儲,那就需要通過PCIe外擴sata。如果不想外擴,那就用NVME SSD。如果系統比較小,比如一些實時系統Vxworks啥的,那麼把系統生成bin文件,放到啟動用QSPI Flash剩餘的空間也是可以的,當然放到SD卡裡也是可以的。要求前面也說過了,只要放的下,固件能看到這個存儲,能操作它就可以。

2.2 如何讓CPU開始工作?

2.2.1 上電時序

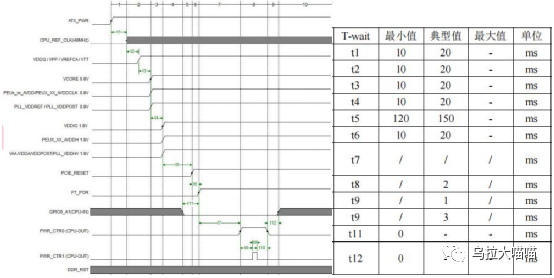

在前面2.1.2供電和電源管理章節講過,要讓CPU從未加電狀態到加電後工作狀態,就是使CPU從S4/S5狀態轉到S0狀態。這個狀態跳轉其實就是通過外邊的電源管理控制器(CPLD或EC或X100)跑一下CPU的上電時序。

圖 CPU上電時序

這裡提示一點,手冊里給出了上電時序的各個時序之間的延時t值,就是上面圖中的t1~t12,那就嚴格按照手冊來做就好了。不要去問不這麼做會怎麼樣。可能你設計的好,不這麼做也能用,但是這個可沒法保證每次這麼做都可以,手冊都給參數了,就按手冊做不就好了麽。

上電時序跑完,CPU就會啟動了,它下一步就會去QSPI CS0介面去讀數據了,所以你如果不知道自己時序是不是好了,那就可以用示波器去量QSPI CS0是否有讀數據的動作,同時測量一下QSPI的時鐘,在固件載入前應該是380KHz。也就是CS0是否有拉低的狀態。要是有拉低,那就說明CPU在嘗試去讀外置FLASH了,那麼也就說明CPU上電正常了,已經開始工作了。

2.2.2 固件

固件這個名字其實應該不陌生,很多網卡,很多PCIe橋片都要燒EEPROM,那裡面的Bin文件我們就叫固件。這裡CPU啟動用的程式,我們也叫固件,借鑒X86的叫法,那就叫BIOS。只是個名字,不要糾結,在飛騰這裡基本都叫固件。

固件這裡的情況彙總到下表:

表 飛騰CPU固件情況說明

|

固件提供方 |

廠家 |

費用 |

固件形式 |

對應OS |

聯繫方式 |

|

飛騰 |

飛騰 |

免費 |

Uboot |

實時系統(Vx+國內實時系統) 桌面系統(能用設備樹引導的開源linux) |

聯繫飛騰FAE |

|

UEFI |

桌面系統(麒麟+開源linux) |

||||

|

第三方 |

昆侖 |

收費 |

聯繫廠商 |

聯繫廠商 |

http://www.kunluntech.com.cn/lxwm |

|

百敖 |

收費 |

http://www.byosoft.com.cn/rhgm/index.jhtml |

|||

|

國科銀河 |

收費 |

http://hngkyh.com/index.php?c=about&a=detail&id=14 |

通過上面的表我們可以發現,要是使用免費的,那麼就用飛騰提供的固件。飛騰固件有兩種形式,uboot或者UEFI。Uboot能引導實時系統,比如vx類的,也能引導桌面系統,但是桌面系統只能引導開源linux,換句話說就是只能引導能提供設備樹的桌面系統。UEFI只能引導桌面系統,比如麒麟、ubuntu這類的。

那麼有人問了,我想UEFI引導vx不可以麽?可以,那麼就用第三方收費的,這裡只是飛騰的UEFI不支持。飛騰免費提供的就是解決大家調試用,比如你板子都來了,總不能等第三方定製的固件到了才能去引導系統去測試板子吧,這會兒你就可以用飛騰提供的固件先進行測試,保證你的測試周期。同時這裡也說明一點,飛騰的UEFI不是商用的交付用的固件,只是用於測試的,所以它有很多功能還是可以提升的,但是這裡要是有定製功能,就需要自己去改了,飛騰只提供基礎版本夠你用,要是有定製功能,要麼自己改,要麼去找第三方固件廠商去購買。

飛騰固件我們拿uboot固件舉例,它是由uboot部分和PBF部分組成的。其中uboot是提供源碼的,PBF是閉源的bin文件。飛騰提供固件編譯環境、編譯方法指導等。這個可以查看網上的文章:

https://blog.csdn.net/yorkworlddream/article/details/125482429?spm=1001.2014.3001.5501

B站視頻:

https://www.bilibili.com/video/BV1h94y197ry/

https://www.bilibili.com/video/BV1ce4y197ze/

https://www.bilibili.com/video/BV1Fg411Z761/

裡面將固件編譯配置方法講的很清楚了,我這裡就不展開講了。總而言之一句話,就是飛騰提供的固件配置環境和操作方法,能讓一個沒有搞過配置的硬體工程師都能很容易的把CPU的核心數、記憶體、PCIe等進行配置。

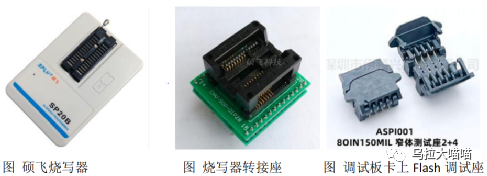

固件編譯完是一個bin文件,這個文件我們要通過燒片機寫器把它燒到我們QSPI FLASH,這個flash燒好後,放到CPU QSPI CS0介面上,CPU開機後就會去讀flash里的內容了。所以為了調試方便,我們需要兩個東西,一個是燒片機寫器,一個就是儘量在CPU QSPI CS0介面上接一個調試座。

下麵展示的就是燒寫器、燒寫器轉晶元座,和焊接到PCB板上的調試座。

燒寫器產品很多,這裡示例的是碩飛的燒寫器和它對應的16pin的轉接座,當然你要是用8pin的flash,那就用8pin的轉接座。(碩飛公司看到可以聯繫我打錢哈,●ˇ∀ˇ●)

焊接到PCB上調試座主要就是方便flash的取換,因為調試中固件可能經常要改參數,要是沒有這個調試座,flash就要來來回回的拆下來燒寫再焊上這樣。

碩飛公司各燒寫器支持器件列表:

https://www.sflytech.com/devlist.asp?model=SP20P/SP20X/SP20F/SP20B

2.2.3 系統

固件調完,就要到系統了。我們後面都是基於飛騰固件來講的,使用第三方固件的不在我們討論範圍里。

系統的引導我們下麵也要分幾種不同的情況進行說明。表的形式列出:

表 不同固件下的系統引導

|

系統 |

採用固件 |

系統說明 |

|

桌面系統 |

Uboot |

系統只能是在其他地方,將硬碟分好區,在指定位置放好設備樹、系統鏡像、文件系統後,拔下來放到我們最終的板卡上,使用uboot通過設備引導系統啟動 |

|

UEFI |

可以在最終板卡上,使用類似x86+windows的那種方法,把系統iso放到U盤裡,在UEFI下通過U盤來安裝系統。系統引導時,是採用grub啟動系統。 |

|

|

實時系統 |

Uboot |

把系統鏡像bin文件放到存儲器中,使用uboot命令找到bin,引導啟動。 |

2.3 設計資料獲取

|

資源類型 |

獲取渠道 |

|

|

硬體 |

晶元手冊,設計demo等 |

聯繫飛騰FAE |

|

PCIe外設、QSPI Flash等硬體相容外設列表 |

通過飛騰官網→技術支持→硬體服務 https://phytium.com.cn/class/137 |

|

|

軟體 |

Uboot、UEFI源碼和固件編譯環境等 |

聯繫飛騰FAE |

|

飛騰linux內核 |

聯繫飛騰FAE |

|

|

Vx BSP、裸跑、Yocto、Android、openHarmony等其他資源 |

通過gitee代碼倉庫 https://gitee.com/phytium_embedded |

|

|

技術支持 |

飛騰有自己的技術支持平臺,是網頁版的,有基於飛騰的項目要做,通過銷售渠道或者技術渠道,找到飛騰的FAE。在技術支持平臺註冊賬號,建立項目,從項目獲取資料開始,所有的技術問題,包括設計中有問題,都可以從技術支持平臺上提工單要到支持,很方便。 (主要提示:一定要找飛騰技術支持部的FAE) |

註冊和登錄網址: https://serviceplus.phytium.com.cn/ 註冊完賬號,要找飛騰FAE給審核賬號。

|

三、基於飛騰晶元的調試步驟

3.1 環境準備

|

序號 |

設備名稱 |

用途 |

要求 |

|

1 |

串口線 |

用於連接飛騰CPU調試串口 |

根據硬體設計,要是TTL串口就用TTL串口線,要是RS232電平,就用RS232串口線 |

|

2 |

PC機 |

用於運行串口調試軟體 |

建議有兩種,一種就是SecureCRT,另外一種就是純字元型串口助手,比如sscom。因為SecureCRT它會解析終端命令比如退格、清屏啥的,導致log存的有的時候不全。所以要用sscom這類不執行終端命令的串口調試助手把所有的串口信息都存下來。 |

|

3 |

萬用表 |

用來測量CPU各個電阻抗,保證沒有焊接短路 |

沒啥要求,不是十幾二十塊錢那種的就行 |

|

4 |

示波器 |

必要時用來測量QSPI 介面波形。必要時用來測量電源紋波。 |

沒啥要求,有表筆就行。要是測紋波,可是得有接地彈簧,能靠測。

|

3.2 靜態測量

3.2.1 測量靜態阻抗

將萬用表打到電阻檔位,然後分別測量 Vcore、VDDQ、VDDQ、VTT 的靜態阻抗。這裡要提示一點,核電阻抗很低,很多都在1Ω、2Ω、3Ω都是正常的,換句話說,只要不是0Ω就行!很多人用二極體檔測阻抗,有的表一測核電阻抗就響了,不要光看響不響,要看看值。

3.2.2 測量電壓

在確保電路沒有存在短路的情況下,對電路板進行上電,查看電路板上的核電壓、記憶體電壓、IO 口電壓、3.3V 電壓、5V 電壓等是否正確。

這裡電壓就自己去看手冊去對就好了。此時要是為了穩妥,可以把紋波也量一量。但此時量到的只是靜態的電壓紋波,固件和系統跑起來,這個紋波和此時可能是不一致的。

3.3 加電前準備

前面靜態做完,加電前的準備工作基本就沒啥了,主要就是不管你是用CPLD還是EC還是X100,加電前一定要把上電時序保證了,至少你編程是照著時序去實現的。千萬不要連上電時序控都沒控,著急的就上電。

其次,就是固件要編好了,燒到了flash中,並且flash已經放到了調試座上,也就是CPU可以通過QSPI CS0介面去讀flash里的固件了。

3.4 加電

3.4.1 調試串口有列印

3.4.1.1 能進shell

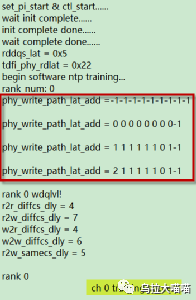

調試串口有列印,並且能進shell,這個真的是要恭喜你,板子調試太順利了。不過這麼順利了,我們也要看看log,尤其是看看ddr訓練部分訓練的是否順利。因為即使我們DDR部分設計如果有問題,要是不是很致命的話,控制器會嘗試多次參數訓練,最終找到能用的參數。我們要關心的是訓練次數,正常來說我們從log上,參數訓練是很短的。要是我們看到log上有很多次的參數嘗試,那麼說明咱們這個ddr還是有些問題。

下麵是訓練成功的log截圖,如果我們在達到success之前,反覆出現過很多次紅框框出的那種信息,那麼說明DDR控制器嘗試了很多參數,最終才找到了一個合適。見過一些板子需要訓練大概20s多,可以從log上看到很多很多個紅框的信息。這種說明DDR設計上不是很好,需要再仔細查一查。

圖 log中記憶體訓練部分截圖

進了shell,我們就可以敲命令了。

uboot飛騰是在公版的上面改的,所有命令都是相容的,我們可以搜uboot命令就可以了。環境變數的:Printenv、setenv、saveenv。寄存器讀寫:md、mw。PCIe外設掃描:pci e。

UEFI也是相容公版UEFI的。寄存器讀寫:mm。PCIe外設掃描:pci。網路:ifconfig、ping。

這個我們後面也單獨出一個文檔,這裡也是簡要說明一下。

3.4.1.2不能進shell

串口有列印,但是卡半截,不能跑到shell,這裡絕大多數都是硬體問題。我們要根據列印來判斷可能的故障點。

這個問題點很多,我們後面也是單獨出文章來說明。這裡單獨提示一點,串口卡了這時候要用示波器測紋波了。因為固件已經開始跑了,如果紋波很大,可能會出現卡在很多位置,這個就沒法判斷了,所以固件咋調都過不去,紋波是必須要量的,尤其是核電的,不能超5%。

3.4.2 串口無列印

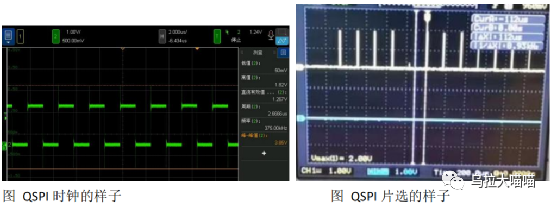

加電後串口都沒有列印,那麼我們首先就是要用示波器量下QSPI的時鐘和片選。

QSPI 介面作為啟動載入片外固件的唯一介面。CPU上電後後,通過QSPI介面的QSPI_CSN0片選的Flash晶元載入固件,來執行相關指令。因此需要查看 QSPI 的時鐘信號(QSPI讀固件之前時鐘以及讀完之後固件配置的時鐘),QSPI讀固件之前時鐘頻率應為380KHz左右,網安版的應該是4.6MHz。

表 串口無列印各種可能性分析

|

QSPI時鐘和片選 |

故障可能性 |

解決方法 |

|

無 |

看上電時序,測量系統時鐘 |

測量上電時序,保證與手冊一致。測量系統時鐘,保證滿足晶元要求。 |

|

有 |

Flash是否適配過 |

查飛騰官網適配型號,看是否進行過相容適配 |

|

Flash電平與CPU電平是否一致,因為有的設計可能採用了3.3V flash,接到CPU上時往了過電平轉換晶元了 |

要是真是電壓不一致,儘量就是換電平一致的flash晶元再試試了 |

|

|

Flash有沒有虛焊。 |

Flash各個腳都測測,都量量的吧 |

|

|

測量CPU晶元調試串口的管腳處,看看是否有波形,有可能是串口通路上串口晶元或者調試串口線或者串口軟體啥的有問題呢 |

這個就讓硬體工程師來測吧,這個要不會他也做不了飛騰的板子 |

3.5 系統引導

使用uefi去安裝引導系統,請看文章:

https://blog.csdn.net/yorkworlddream/article/details/124866224

使用uboot去製作系統,引導系統,請參考倉庫說明:

https://gitee.com/phytium_embedded/phytium-linux-buildroot

附錄:文中涉及到的外部文章彙總:

|

內容 |

鏈接 |

|

飛騰技術支持平臺 |

https://serviceplus.phytium.com.cn/ |

|

飛騰固件編譯指導 |

https://blog.csdn.net/yorkworlddream/article/details/125482429?spm=1001.2014.3001.5501 |

|

https://www.bilibili.com/video/BV1h94y197ry/ |

|

|

https://www.bilibili.com/video/BV1ce4y197ze/ |

|

|

https://www.bilibili.com/video/BV1Fg411Z761/ |

|

|

飛騰外設相容列表 |

https://phytium.com.cn/class/137 |

|

飛騰gitee代碼倉庫 |

https://gitee.com/phytium_embedded |

|

uefi去安裝引導系統 |

https://blog.csdn.net/yorkworlddream/article/details/124866224

|

|

uboot去製作系統,引導系統 |

https://gitee.com/phytium_embedded/phytium-linux-buildroot

|

|

碩飛燒寫器支持列表 |

https://www.sflytech.com/devlist.asp?model=SP20P/SP20X/SP20F/SP20B

|

|

昆侖固件 |

http://www.kunluntech.com.cn/lxwm |

|

百敖固件 |

http://www.byosoft.com.cn/rhgm/index.jhtml |

|

科華固件 |

http://hngkyh.com/index.php?c=about&a=detail&id=14 |

飛騰愛好者技術交流群碼 公眾號“烏拉大喵喵”

公眾號“烏拉大喵喵”