SRAM大多是由CMOS管組成的揮發性靜態存儲器。在掉電後存儲器中所存數據就會丟失。隨機靜態存儲器可以對任何地址進行讀寫操作,通過鎖存器的原理對數據進行保存,在無操作狀況下,鎖存器處於穩態,保持數據穩定,不用進行周期性的電荷刷新。SRAM由基本單元構成的陣列以及外圍電路構成,其中陣列的劃分和外圍電路 ...

SRAM大多是由CMOS管組成的揮發性靜態存儲器。在掉電後存儲器中所存數據就會丟失。隨機靜態存儲器可以對任何地址進行讀寫操作,通過鎖存器的原理對數據進行保存,在無操作狀況下,鎖存器處於穩態,保持數據穩定,不用進行周期性的電荷刷新。SRAM由基本單元構成的陣列以及外圍電路構成,其中陣列的劃分和外圍電路的優劣對整個SRAM的性能有很大的影響。

SRAM是隨機存儲器的一種,它由靜態揮發性存儲單元組成的存儲陣列(或者叫內核,core) 組成,其地址解碼集成在片內。SRAM 速度很快而且不用刷新就能保存數據不丟失。它以雙穩態電路形式存儲數據,結構複雜,內部需要使用更多的晶體管構成寄存器.以保存數據。SRAM由於靠連續的供電來維持所存數據的完整性,故屬於易揮發性存儲器。

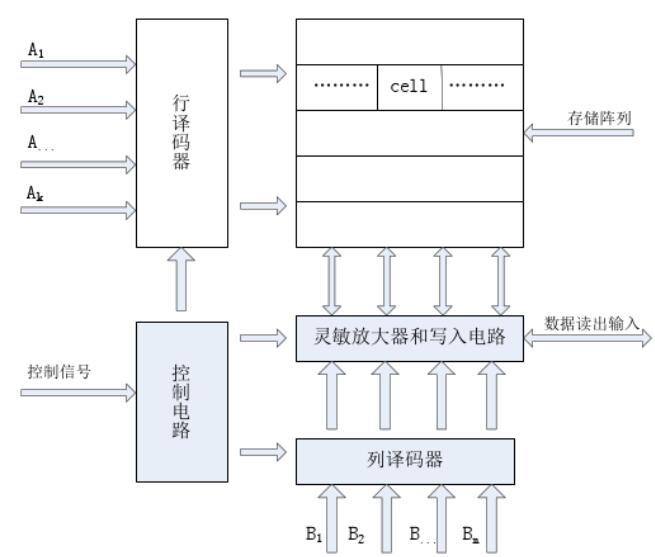

SRAM電路結構與操作和一般的RAM類似,由存儲陣列、靈敏放大器、解碼器、輸入輸出電路和時序控制電路五大部分組成。存儲單元按行和列排列起來就組成了sram晶元的陣列結構,行和列分別稱為“字線”和“位線”。每個存儲單元對應於一個唯一的地址,或者說行和列的交叉就定義出了地址,而且每一個地址和某一特定的數據輸入輸出埠是相連的。一個存儲晶元上的陣列(或者自陣列)數目是由整個存儲器的大小、數據輸入輸出埠數目、存儲速度要求、整個晶元的版圖佈局和測試要求所決定的。

圖1 SRAM 的整體結構圖

如圖1所示存儲陣列是由存儲單元(cell)構成的矩形陣列。每一個單元都有自己獨特的地址,通過外圍的解碼電路選中相應的單元進行讀寫操作。解碼電路包括行解碼電路和列解碼電路,其中行解碼電路用來從2* 行中選中一行,列解碼是從2* 中列中選出一-列。這樣通過行解碼列解碼的共同作用來從陣列中選出相應的單元進行讀寫操作。靈敏放大器和寫入電路用來對數據進行讀寫操作。

在數據讀出過程中,由於位線過長使得從單元中讀出的信號很弱,需要用靈敏放大器來放大信號,加快數據的讀出過程。寫入電路用來進行數據的輸入。控制電路主要用來控制數據的讀寫以及解碼過程。通過相應的控制信號如讀使能信號寫使能信號等來控制數據的讀寫操作。