隨著SOC 技術的發展,CMOS 工藝尺寸不斷縮小,晶元集成度越來越高,使得單位面積晶元的功耗不斷提高。近年來,攜帶型電子產品如智能手機、平板電腦、數位相機、智能手環發展迅猛,而對於使用電池的攜帶型電子產品,晶元的功耗會直接影響到電池的使用時間、使用壽命,功耗逐漸成為大規模集成電路設計中最關心的問題 ...

隨著SOC 技術的發展,CMOS 工藝尺寸不斷縮小,晶元集成度越來越高,使得單位面積晶元的功耗不斷提高。近年來,攜帶型電子產品如智能手機、平板電腦、數位相機、智能手環發展迅猛,而對於使用電池的攜帶型電子產品,晶元的功耗會直接影響到電池的使用時間、使用壽命,功耗逐漸成為大規模集成電路設計中最關心的問題。

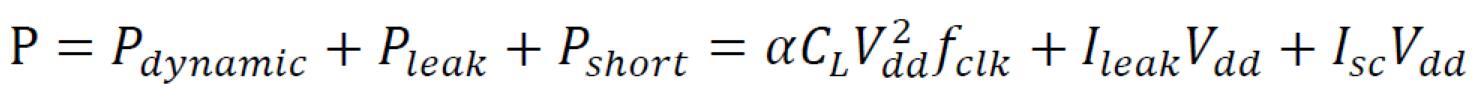

CMOS 集成電路中的功耗由動態功耗、靜態功耗和短路功耗組成。各個功耗表達式如公式所示:

其中,Pdynamic是電路電容充放電產生的動態功耗,與電源電壓成平方關係;Pleak是靜態功耗,即漏電流產生的功耗,與電源電壓成一次方關係;Pshort是電路的短路功耗,產生於NMOS、PMOS 同時導通的瞬間,同樣與電源電壓成一次方關係。由此可見降低電源電壓能夠直接有效地降低電路的功耗。

SRAM的功耗包括動態功耗和靜態功耗,動態功耗和靜態功耗所占總功耗的比例不是一成不變的,其比例隨集成電路工藝的發展而變化。工藝每前進一個節點,MOSFET 漏電流大約增加5 倍。器件特征尺寸的減少,使得靜態功耗在電路總功耗中所占比例越來越大,同時也必然引起靜態泄漏電流的增加。據統計,在90nm 工藝下,IC 漏電流功耗大約占整個功耗的1/3,在65nm 工藝下,IC 漏電流功耗已經占總功耗的一半以上。由於動態功耗與電源電壓是平方的關係,靜態功耗與電源電壓是一次方關係,降低電源電壓能夠使得動態功耗和靜態功耗都得到大幅降低。