SRAM 即靜態RAM.它也由晶體管組成,SRAM的高速和靜態特性使它們通常被用來作為Cache存儲器。電腦的主板上都有Cache插座。 下圖所示的是一個SRAM的結構框圖。 由上圖看出SRAM一般由五大部分組成,即存儲單元陣列、地址解碼器(包括行解碼器和列解碼器)、靈敏放火器、控制電路和緩衝/驅 ...

SRAM 即靜態RAM.它也由晶體管組成,SRAM的高速和靜態特性使它們通常被用來作為Cache存儲器。電腦的主板上都有Cache插座。

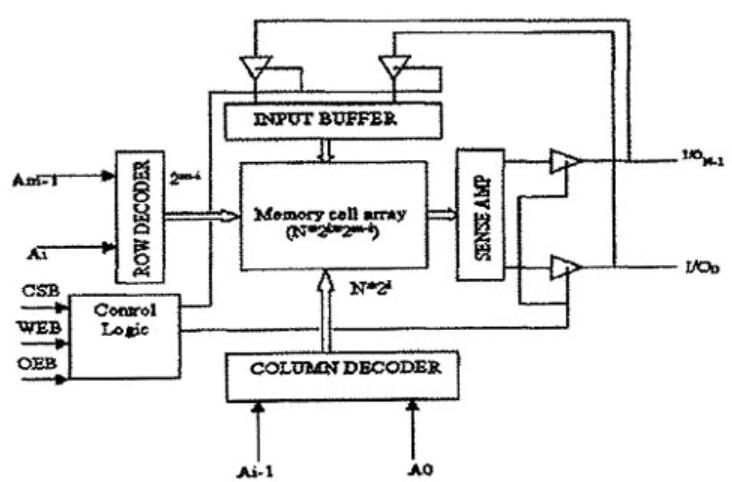

下圖所示的是一個SRAM的結構框圖。

由上圖看出SRAM一般由五大部分組成,即存儲單元陣列、地址解碼器(包括行解碼器和列解碼器)、靈敏放火器、控制電路和緩衝/驅動電路。在圖中A0-Am-1為地址輸入端,CSB. WEB和OEB為控制端,控制讀寫操作,為低電平有效1100-11ON-1為數據輸入輸出端。存儲陣列中的每個存儲單元都與其它單元在行和列上共用電學連接,其中水平方向的連線稱為“字線”,而垂直方向的數據流入和流出存儲單元的連線稱為“位線”。

通過輸入的地址可選擇特定的字線和位線,字線和位線的交叉處就是被選中的存儲單元,每一個存儲單元都是按這種方法被唯一選中,然後再對其進行讀寫操作。有的存儲器設計成多位數據如4位或8位等同時輸入和輸出,這樣的話就會同時有4個或8個存儲單元按上述方法被選中進行讀寫操作。

在SRAM 中,排成矩陣形式的存儲單元陣列的周圍是解碼器和與外部信號的介面電路。存儲單元陣列通常採用正方形或矩陣的形式,以減少整個晶元面積並有利於數據的存取。以一個存儲容量為4K位的SRAM為例,共需12條地址線來保證每一個存儲單元都能被選中(212 =-4096)。如果存儲單元陣列被排列成只包含一列的長條形,則需要一個12/4K位的解碼器,但如果排列成包含64行和64列的正方形,這時則只需一個6/64位的行解碼器和一個6/64位的列解碼器,行、列解碼器可分別排列在存儲單元陣列的兩邊,64行和64列共有4096個交叉點,每一個點就對應一個存儲位。

因此將存儲單元排列成正方形比排列成一列的長條形要大大地減少整個晶元地面積。存儲單元排列成長條形除了形狀奇異和麵積大以外,還有一個缺點就是排在列的上部的存儲單元與數據輸入/輸出端的連線就會變得很長,特別是對於容量比較大得存儲器來說,情況就更為嚴重,而連線的延遲至少是與它的長度成線性關係,連線越長,線上的延遲就越大,所以就會導致讀寫速度的降低和不同存儲單元連線延遲的不一致性,這些都是在設計中需要避免的。