Everspin在磁存儲器設計,製造和交付給相關應用方面的知識和經驗在半導體行業中是獨一無二的。在平面內和垂直磁隧道結(MTJ)STT-MRAM位單元的開發方面處於市場領先地位。包括40nm,28nm及更高工藝在內的先進技術節點上進行了全包交鑰匙的300mm大批量平面內和垂直MTJ ST-MRAM生 ...

Everspin在磁存儲器設計,製造和交付給相關應用方面的知識和經驗在半導體行業中是獨一無二的。在平面內和垂直磁隧道結(MTJ)STT-MRAM位單元的開發方面處於市場領先地位。包括40nm,28nm及更高工藝在內的先進技術節點上進行了全包交鑰匙的300mm大批量平面內和垂直MTJ ST-MRAM生產。生產基於180nm,130nm和90nm工藝技術節點的MRAM產品。下麵要介紹關於everspin公司MRAM演示軟體分析

everspin公司MRAM演示軟體分析

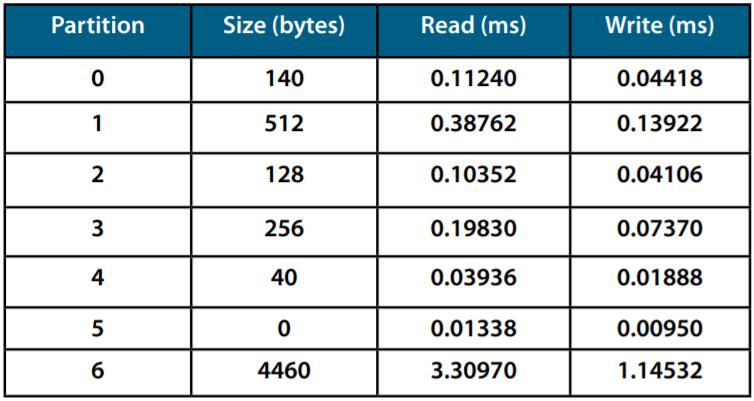

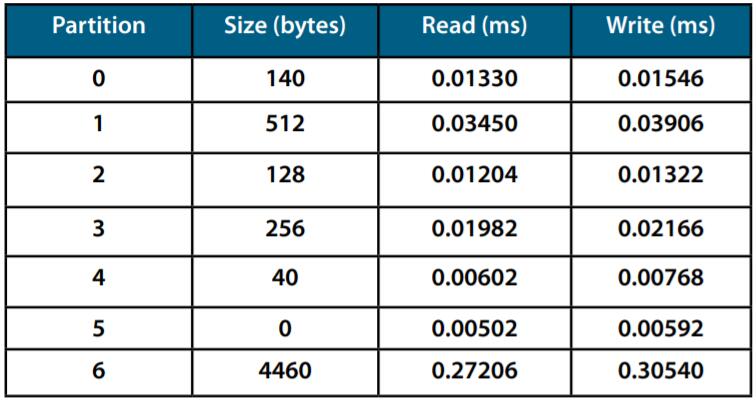

MRAM低級驅動程式通過操作系統和調度程式集成到動力總成應用程式中。讀寫周期由系統時鐘(300MHz)測量。圖1&2顯示了針對動力總成應用的具有不同非易失性存儲器介面的每個分區的讀/寫時間。這些表顯示大多數讀/寫周期小於2ms。毫不奇怪,該表確認35ns並行介面以比40MHz串口串列mram更快的速率傳輸數據。

Figure 1 SPI MRAM; CLK 40MHz

Figure 1 SPI MRAM; CLK 40MHz

使用SPI MRAM時,由於微控制器的硬體延遲(緩衝區接收/發送,設置/清除標誌,讀/寫存儲器)以及MRAM和微控制器匯流排之間的同步,因此讀周期要比寫周期花費更長的時間,與並行MRAM類似,寫入周期比讀取周期要花費更長的時間。1&2中顯示的值包括硬體收發器,硬體延遲(收發器緩衝區,讀/寫存儲器),LLD軟體延遲以及MRAM與動力總成微控制器之間的同步。

Figure 2 EBI MRAM; CLK 66.666MHz

Figure 2 EBI MRAM; CLK 66.666MHz

我們用EBI和SPI介面設備驗證了不同的動力總成工作模式。 在整個地址空間範圍內讀寫各種類型的數據。通常,MRAM的操作和時序類似於32位微控制器的規範和時序。 而且,與DLFASH相比,當今的非易失性存儲器可以接受MRAM設備的性能和吞吐量。