SPI是嵌入式中使用比較廣泛的協議之一,本文從該協議的原理入手對其進行了詳細介紹,並結合STM32F103ZET主控晶元對其進行了說明,最後給出了兩個實例代碼demo供大家做參考。 ...

1 SPI協議詳解

SPI是串列外設介面(Serial Peripheral Interface)的縮寫,是美國摩托羅拉公司(Motorola)最先推出的一種同步串列傳輸規範,也是一種單片機外設晶元串列擴展介面,是一種高速、全雙工、同步通信匯流排,所以可以在同一時間發送和接收數據,SPI沒有定義速度限制,通常能達到甚至超過10M/bps。SPI有主、從兩種模式,通常由一個主模塊和一個或多個從模塊組成(SPI不支持多主機),主模塊選擇一個從模塊進行同步通信,從而完成數據的交換。提供時鐘的為主設備(Master),接收時鐘的設備為從設備(Slave),SPI介面的讀寫操作,都是由主設備發起,當存在多個從設備時,通過各自的片選信號進行管理。

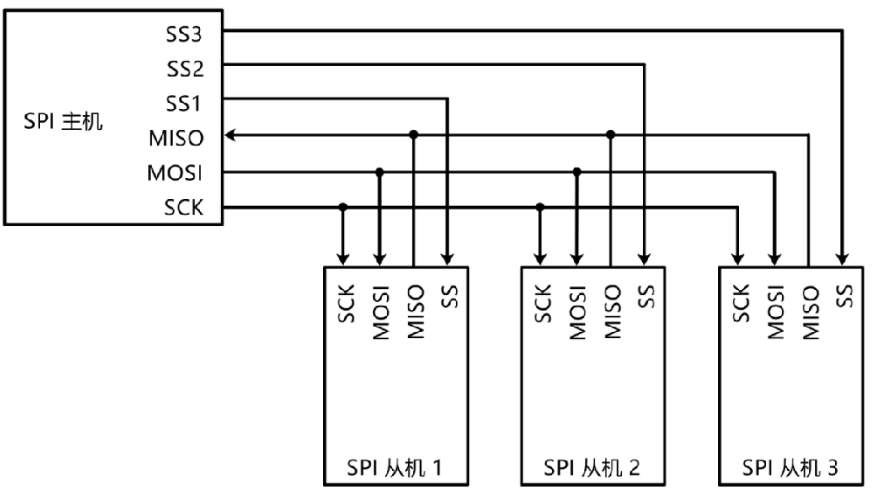

SPI通信原理很簡單,需要至少4根線,單向傳輸時3根線,它們是MISO(主設備數據輸入)、MOSI(主設備數據輸出)、SCLK(時鐘)和CS/SS(片選):

MISO(Master Input Slave Output):主設備數據輸入,從設備數據輸出;

MOSI(Master Output Slave Input):主設備數據輸出,從設備數據輸入;

SCLK(Serial Clock):時鐘信號,由主設備產生;

CS/SS(Chip Select/Slave Select):從設備使能信號,由主設備控制,一主多從時,CS/SS是從晶元是否被主晶元選中的控制信號,只有片選信號為預先規定的使能信號時(高電位或低電位),主晶元對此從晶元的操作才有效。

圖1 一主多從

1.1 通信原理

SPI主設備和從設備都有一個串列移位寄存器,主設備通過向它的SPI串列寄存器寫入一個位元組來發起一次傳輸。

圖2 數據移位交換

SPI數據通信的流程可以分為以下幾步:

1、主設備發起信號,將CS/SS拉低,啟動通信。

2、主設備通過發送時鐘信號,來告訴從設備進行寫數據或者讀數據操作(採集時機可能是時鐘信號的上升沿(從低到高)或下降沿(從高到低),因為SPI有四種模式,後面會講到),它將立即讀取數據線上的信號,這樣就得到了一位數據(1bit)。

3、主機(Master)將要發送的數據寫到發送數據緩存區(Memory),緩存區經過移位寄存器(緩存長度不一定,看單片機配置),串列移位寄存器通過MOSI信號線將位元組一位一位的移出去傳送給從機,同時MISO介面接收到的數據經過移位寄存器一位一位的移到接收緩存區。

4、從機(Slave)也將自己的串列移位寄存器(緩存長度不一定,看單片機配置)中的內容通過MISO信號線返回給主機。同時通過MOSI信號線接收主機發送的數據,這樣,兩個移位寄存器中的內容就被交換。

其實SPI只有主模式和從模式之分,沒有讀和寫的說法,外設的寫操作和讀操作是同步完成的。若只進行寫操作,主機只需忽略接收到的位元組(虛擬數據/dummy data);反之,若主機要讀取從機的一個位元組,就必鬚髮送一個空位元組來引發從機的傳輸。也就是說,你發一個數據必然會收到一個數據;你要收一個數據必須也要先發一個數據。

1.2 通信特性

1.2.1 設備選擇

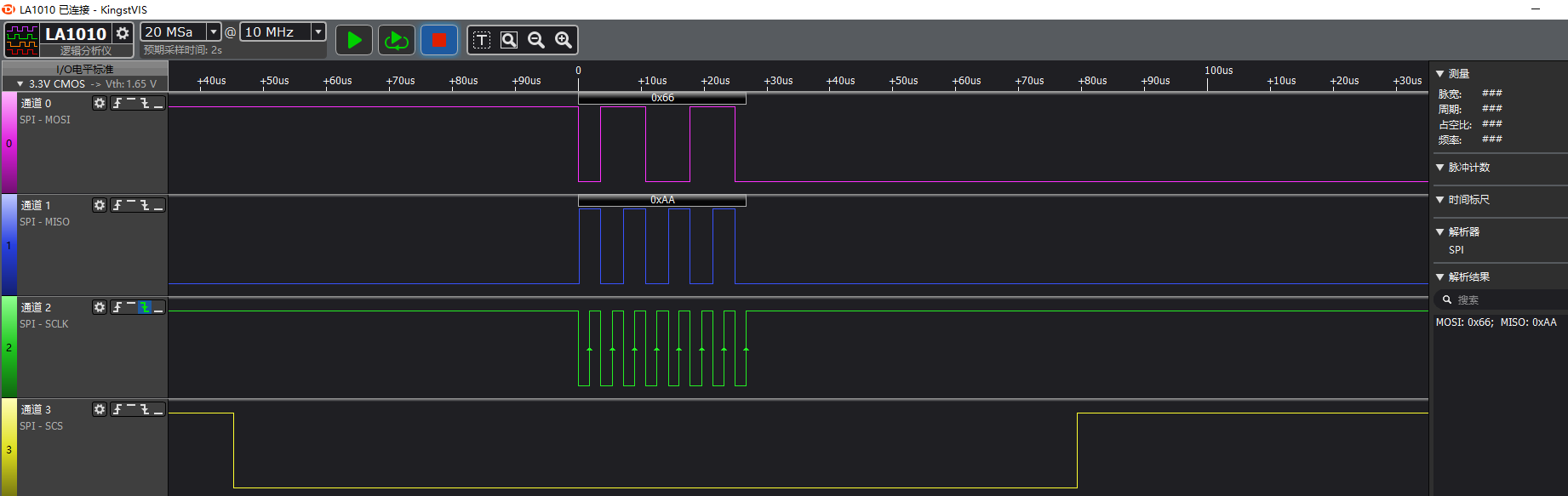

SPI是單主設備(Single Master)通信協議,只有一支主設備能發起通信,當SPI主設備想讀/寫從設備時,它首先拉低從設備對應的SS線(SS是低電平有效)。接著開始發送工作脈衝到時鐘線上,在相應的脈衝時間上,主設備把信號發到MOSI實現“寫”,同時可對MISO採樣而實現“讀”。如下圖所示:

圖3 邏輯分析儀數據抓取示例

低電平選擇只是標準模式,也可以選擇高電平有效,即IDLE時CLK為低電平,Master在要選擇Slave時將CLK信號拉高。需要說明的是無論哪種方式,Master和Slave需要對選擇模式配置一致。

1.2.2 設備時鐘

SPI時鐘特點主要包括:時鐘速率、時鐘極性和時鐘相位三方面。

時鐘速率

SPI匯流排上的主設備必須在通信開始時候配置並生成相應的時鐘信號。從理論上講,只要實際可行,時鐘速率就可以是你想要的任何速率,當然這個速率受限於每個系統能提供多大的系統時鐘頻率,以及最大的SPI傳輸速率。

時鐘極性

根據硬體製造商的命名規則不同,時鐘極性通常寫為CKP或CPOL。時鐘極性和相位共同決定讀取數據的方式,比如信號上升沿讀取數據還是信號下降沿讀取數據。

CKP可以配置為1或0,這意味著可根據需要將時鐘的預設狀態(IDLE)設置為高或低。極性反轉可以通過簡單的邏輯逆變器實現。須參考設備的數據手冊才能正確設置CKP和CKE。

CKP = 0:時鐘空閑IDLE為低電平0;

CKP = 1:時鐘空閑IDLE為高電平1。

時鐘相位

根據硬體製造商的不同,時鐘相位通常寫為CKE或CPHA。顧名思義,時鐘相位/邊沿,也就是採集數據時是在時鐘信號的具體相位或者邊沿;

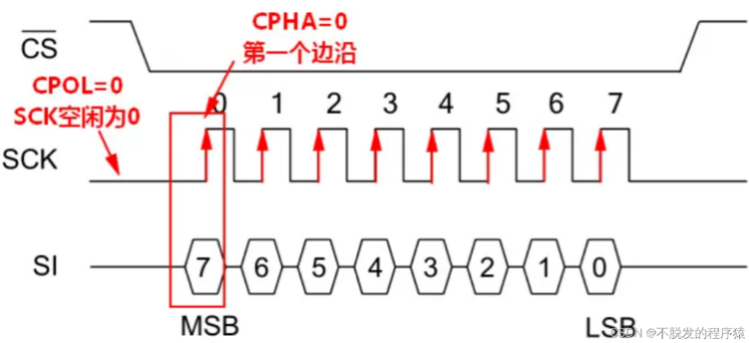

CKE = 0:在時鐘信號SCK的第一個跳變沿採樣;

CKE = 1:在時鐘信號SCK的第二個跳變沿採樣。

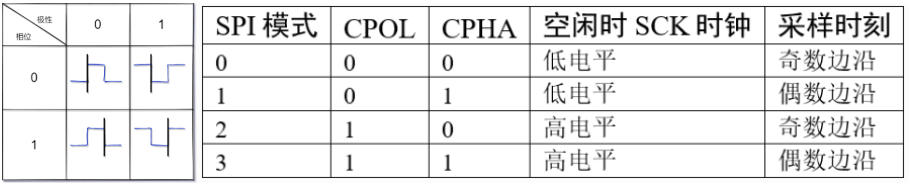

1.2.3 四種模式

根據SPI的時鐘極性和時鐘相位特性可以設置4種不同的SPI通信操作模式,它們的區別是定義了在時鐘脈衝的哪條邊沿轉換(toggles)輸出信號,哪條邊沿採樣輸入信號,還有時鐘脈衝的穩定電平值(就是時鐘信號無效時是高還是低),詳情如下所示:

Mode0:CKP=0,CKE=0:當空閑態時,SCK處於低電平,數據採樣是在第1個邊沿,也就是SCK由低電平到高電平的跳變,所以數據採樣是在上升沿(準備數據),(發送數據)數據發送是在下降沿。

Mode1:CKP=0,CKE=1:當空閑態時,SCK處於低電平,數據發送是在第2個邊沿,也就是SCK由低電平到高電平的跳變,所以數據採樣是在下降沿,數據發送是在上升沿。

Mode2:CKP=1,CKE=0:當空閑態時,SCK處於高電平,數據採集是在第1個邊沿,也就是SCK由高電平到低電平的跳變,所以數據採集是在下降沿,數據發送是在上升沿。

Mode3:CKP=1,CKE=1:當空閑態時,SCK處於高電平,數據發送是在第2個邊沿,也就是SCK由高電平到低電平的跳變,所以數據採集是在上升沿,數據發送是在下降沿。

圖4 四種模式

圖中黑線為採樣數據的時刻,藍線為SCK時鐘信號。

舉個例子,下圖是SPI Mode0讀/寫時序,可以看出SCK空閑狀態為低電平,主機輸出數據在第一個跳變沿被從機採樣,主機輸入數據同理。

圖5 Mode0數據採樣實例

圖5是SPI Mode3讀/寫時序,SCK空閑狀態為高電平,主機輸出數據在第二個跳變沿被從機採樣(對應圖中綠色箭頭),主機輸入數據同理。

1.2.4 優缺點

優點

無起始位和停止位,因此數據位可以連續傳輸而不會被中斷;

沒有像I2C這樣複雜的從設備定址系統;

數據傳輸速率比I2C更高(幾乎快兩倍);

分離的MISO和MOSI信號線,因此可以同時發送和接收數據;

極其靈活的數據傳輸,不限於8位,它可以是任意大小的字;

非常簡單的硬體結構。從站不需要唯一地址(與I2C不同)。從機使用主機時鐘,不需要精密時鐘振蕩器/晶振(與UART不同)。不需要收發器(與CAN不同)。

缺點

使用四根信號線(I2C和UART使用兩根信號線);

無法確認是否已成功接收數據(I2C擁有此功能);

沒有任何形式的錯誤檢查,如UART中的奇偶校驗位;

只允許一個主設備;

沒有硬體從機應答信號(主機可能在不知情的情況下無處發送);

沒有定義硬體級別的錯誤檢查協議;

與RS-232和CAN匯流排相比,只能支持非常短的距離。

2 STM32相關內容

本博客基於STM32F103ZET6控制板進行所有操作,其他STM32F1型號控制板可以參考。

2.1 SPI外設簡介及架構剖析

STM32的SPI外設可用作通訊的主機及從機, 支持最高的SCK時鐘頻率為fpclk/2 (STM32F103型號的晶元預設fpclk1為36MHz, fpclk2為72MHz),完全支持SPI協議的4種模式,數據幀長度可設置為8位或16位, 可設置數據MSB先行或LSB先行。它還支持雙線全雙工、雙線單向以及單線模式。 其中雙線單向模式可以同時使用MOSI及MISO數據線向一個方向傳輸數據,可以加快一倍的傳輸速度。而單線模式則可以減少硬體接線, 當然這樣速率會受到影響。我們只講解雙線全雙工模式。

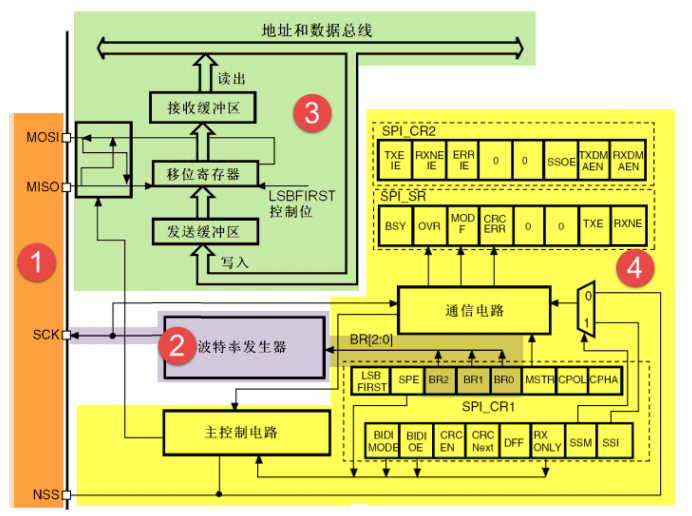

圖6 SPI架構

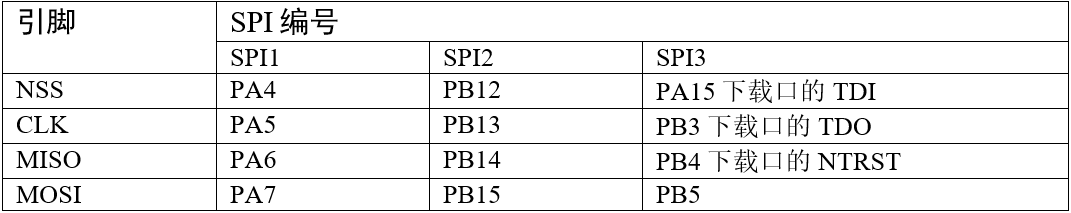

2.1.1 通信引腳

SPI的所有硬體架構都從圖6 SPI架構圖中左側MOSI、MISO、SCK及NSS線展開的。STM32晶元有多個SPI外設, 它們的SPI通訊信號引出到不同的GPIO引腳上,使用時必須配置到這些指定的引腳,見表 STM32F10x的SPI引腳。 關於GPIO引腳的復用功能,可查閱《STM32F10x規格書》,以它為準。

圖7 SPI引腳

其中SPI1是APB2上的設備,最高通信速率達36Mbtis/s,SPI2、SPI3是APB1上的設備,最高通信速率為18Mbits/s。除了通訊速率, 在其它功能上沒有差異。其中SPI3用到了下載介面的引腳,這幾個引腳預設功能是下載,第二功能才是IO口,如果想使用SPI3介面, 則程式上必須先禁用掉這幾個IO口的下載功能。一般在資源不是十分緊張的情況下,這幾個IO口是專門用於下載和調試程式,不會復用為SPI3。

2.1.2 時鐘控制邏輯

SCK線的時鐘信號,由波特率發生器根據“控制寄存器CR1”中的BR[0:2]位控制,該位是對fpclk時鐘的分頻因數, 對fpclk的分頻結果就是SCK引腳的輸出時鐘頻率,計算方法見表 BR位對fpclk的分頻。

圖8 分頻配置

其中的fpclk頻率是指SPI所在的APB匯流排頻率, APB1為fpclk1,APB2為fpckl2。

通過配置“控制寄存器CR”的“CPOL位”及“CPHA”位可以把SPI設置成前面分析的4種SPI模式。

2.1.3 數據控制邏輯

SPI的MOSI及MISO都連接到數據移位寄存器上,數據移位寄存器的數據來源及目標接收、發送緩衝區以及MISO、MOSI線。 當向外發送數據的時候,數據移位寄存器以“發送緩衝區”為數據源,把數據一位一位地通過數據線發送出去;當從外部接收數據的時候, 數據移位寄存器把數據線採樣到的數據一位一位地存儲到“接收緩衝區”中。通過寫SPI的“數據寄存器DR”把數據填充到發送緩衝區中, 通訊讀“數據寄存器DR”,可以獲取接收緩衝區中的內容。其中數據幀長度可以通過“控制寄存器CR1”的“DFF位”配置成8位及16位模式; 配置“LSBFIRST位”可選擇MSB先行還是LSB先行。

2.1.4 整體控制邏輯

整體控制邏輯負責協調整個SPI外設,控制邏輯的工作模式根據我們配置的“控制寄存器(CR1/CR2)”的參數而改變, 基本的控制參數包括前面提到的SPI模式、波特率、LSB先行、主從模式、單雙向模式等等。在外設工作時, 控制邏輯會根據外設的工作狀態修改“狀態寄存器(SR)”,我們只要讀取狀態寄存器相關的寄存器位, 就可以瞭解SPI的工作狀態了。除此之外,控制邏輯還根據要求,負責控制產生SPI中斷信號、DMA請求及控制NSS信號線。

實際應用中,我們一般不使用STM32 SPI外設的標準NSS信號線,而是更簡單地使用普通的GPIO,軟體控制它的電平輸出,從而產生通訊起始和停止信號。

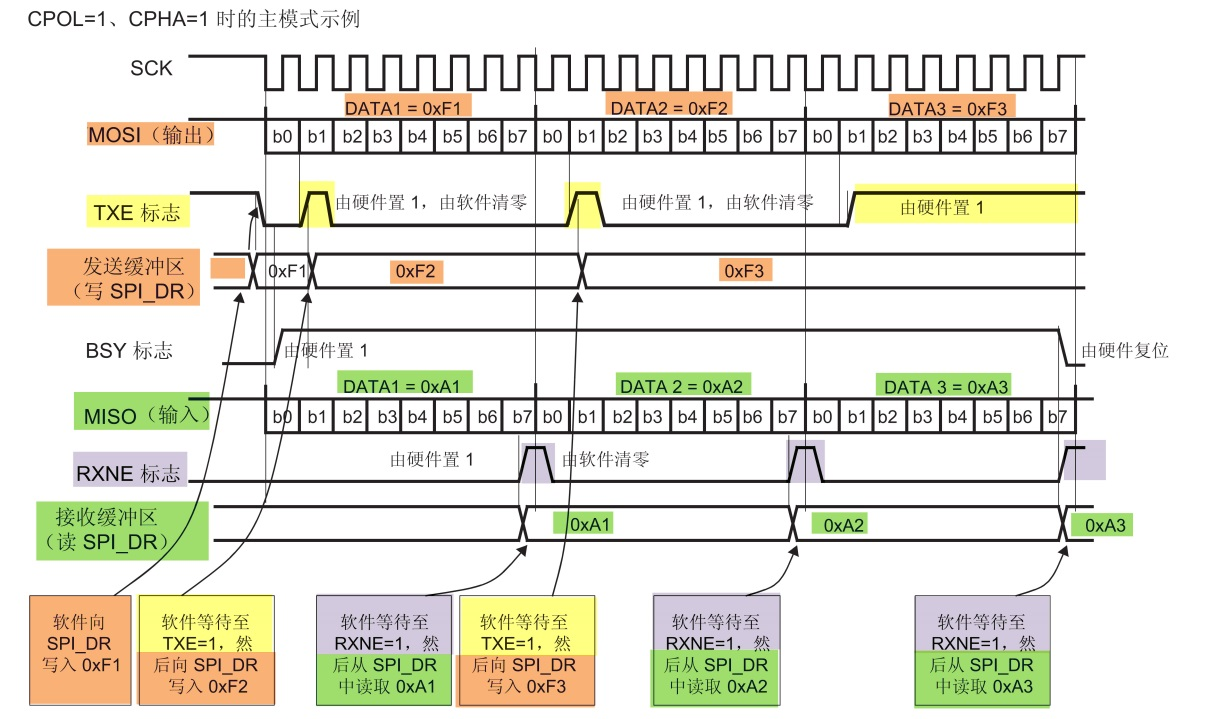

2.2 通信過程

STM32使用SPI外設通訊時,在通訊的不同階段它會對“狀態寄存器SR”的不同數據位寫入參數,我們通過讀取這些寄存器標誌來瞭解通訊狀態。圖9 主發送器通訊過程 中的是“主模式”流程,即STM32作為SPI通訊的主機端時的數據收發過程。

圖9 主模式收發流程

主模式收發流程及事件說明如下:

(1) 控制NSS信號線, 產生起始信號(圖中沒有畫出);

(2) 把要發送的數據寫入到“數據寄存器DR”中, 該數據會被存儲到發送緩衝區;

(3) 通訊開始,SCK時鐘開始運行。MOSI把發送緩衝區中的數據一位一位地傳輸出去; MISO則把數據一位一位地存儲進接收緩衝區中;

(4) 當發送完一幀數據的時候,“狀態寄存器SR”中的“TXE標誌位”會被置1,表示傳輸完一幀,發送緩衝區已空;類似地, 當接收完一幀數據的時候,“RXNE標誌位”會被置1,表示傳輸完一幀,接收緩衝區非空;

(5) 等待到“TXE標誌位”為1時,若還要繼續發送數據,則再次往“數據寄存器DR”寫入數據即可;等待到“RXNE標誌位”為1時, 通過讀取“數據寄存器DR”可以獲取接收緩衝區中的內容。

假如我們使能了TXE或RXNE中斷,TXE或RXNE置1時會產生SPI中斷信號,進入同一個中斷服務函數,到SPI中斷服務程式後, 可通過檢查寄存器位來瞭解是哪一個事件,再分別進行處理。也可以使用DMA方式來收發“數據寄存器DR”中的數據。

2.3 SPI初始化結構體詳解

跟其它外設一樣,STM32標準庫提供了SPI初始化結構體及初始化函數來配置SPI外設。 初始化結構體及函數定義在庫文件“stm32f10x_spi.h”及“stm32f10x_spi.c”中,編程時我們可以結合這兩個文件內的註釋使用或參考庫幫助文檔。 瞭解初始化結構體後我們就能對SPI外設運用自如了,見 代碼清單:SPI-1。

1 typedef struct 2 { 3 uint16_t SPI_Direction; /*設置SPI的單雙向模式 */ 4 uint16_t SPI_Mode; /*設置SPI的主/從機端模式 */ 5 uint16_t SPI_DataSize; /*設置SPI的數據幀長度,可選8/16位 */ 6 uint16_t SPI_CPOL; /*設置時鐘極性CPOL,可選高/低電平*/ 7 uint16_t SPI_CPHA; /*設置時鐘相位,可選奇/偶數邊沿採樣 */ 8 uint16_t SPI_NSS; /*設置NSS引腳由SPI硬體控制還是軟體控制*/ 9 uint16_t SPI_BaudRatePrescaler; /*設置時鐘分頻因數,fpclk/分頻數=fSCK */ 10 uint16_t SPI_FirstBit; /*設置MSB/LSB先行 */ 11 uint16_t SPI_CRCPolynomial; /*設置CRC校驗的表達式 */ 12 } SPI_InitTypeDef;

這些結構體成員說明如下,其中括弧內的文字是對應參數在STM32標準庫中定義的巨集:

-

SPI_Direction

本成員設置SPI的通訊方向,可設置為雙線全雙工(SPI_Direction_2Lines_FullDuplex),雙線只接收(SPI_Direction_2Lines_RxOnly), 單線只接收(SPI_Direction_1Line_Rx)、單線只發送模式(SPI_Direction_1Line_Tx)。

-

SPI_Mode

本成員設置SPI工作在主機模式(SPI_Mode_Master)或從機模式(SPI_Mode_Slave ), 這兩個模式的最大區別為SPI的SCK信號線的時序, SCK的時序是由通訊中的主機產生的。若被配置為從機模式,STM32的SPI外設將接受外來的SCK信號。

-

SPI_DataSize

本成員可以選擇SPI通訊的數據幀大小是為8位(SPI_DataSize_8b)還是16位(SPI_DataSize_16b)。

-

SPI_CPOL和SPI_CPHA

這兩個成員配置SPI的時鐘極性CPOL和時鐘相位CPHA,這兩個配置影響到SPI的通訊模式, 關於CPOL和CPHA的說明參考前面“通訊模式”小節。

時鐘極性CPOL成員,可設置為高電平(SPI_CPOL_High)或低電平(SPI_CPOL_Low )。

時鐘相位CPHA 則可以設置為SPI_CPHA_1Edge(在SCK的奇數邊沿採集數據) 或SPI_CPHA_2Edge(在SCK的偶數邊沿採集數據) 。

-

SPI_NSS

本成員配置NSS引腳的使用模式,可以選擇為硬體模式(SPI_NSS_Hard )與軟體模式(SPI_NSS_Soft ), 在硬體模式中的SPI片選信號由SPI硬體自動產生,而軟體模式則需要我們親自把相應的GPIO埠拉高或置低產生非片選和片選信號。實際中軟體模式應用比較多。

-

SPI_BaudRatePrescaler

本成員設置波特率分頻因數,分頻後的時鐘即為SPI的SCK信號線的時鐘頻率。這個成員參數可設置為fpclk的2、4、6、8、16、32、64、128、256分頻。

-

SPI_FirstBit

所有串列的通訊協議都會有MSB先行(高位數據在前)還是LSB先行(低位數據在前)的問題,而STM32的SPI模塊可以通過這個結構體成員,對這個特性編程式控制制。

-

SPI_CRCPolynomial

這是SPI的CRC校驗中的多項式,若我們使用CRC校驗時,就使用這個成員的參數(多項式),來計算CRC的值。

配置完這些結構體成員後,我們要調用SPI_Init函數把這些參數寫入到寄存器中,實現SPI的初始化,然後調用SPI_Cmd來使能SPI外設。

以上內容引用:https://doc.embedfire.com/mcu/stm32/f103badao/std/zh/latest/book/SPI.html

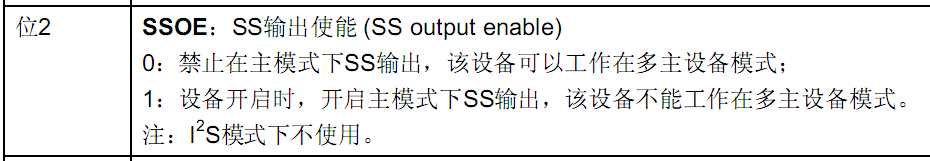

2.4 NSS片選詳解

2.4.1 輸出模式

對於每個SPI的NSS可以輸入,也可以輸出。所謂輸入,就是NSS的電平信號給自己,所謂輸出,就是將NSS的電平信號發送出去,給從機。NSS配置為輸出時只能用作主機,我們可以通過配置SPI_CR2寄存器的SSOE位為1。當SSOE為1時,使能SPI時,NSS就輸出低電平,也就是拉低,因此當其他SPI設備的NSS引腳與它相連,必然接收到低電平,則片選成功,都成為從設備了。對應寄存器定義如下圖

圖10 SSOE

但是,綜合實踐及網上的說法,這種模式下有bug,即:

主機NSS無上拉電阻情況

使能SPI外設後,主機的NSS持續拉低,不會變高,就算關閉SPI外設也沒作用。

主機NSS加上拉電阻情況

使能SPI外設後,主機的NSS拉低,關閉SPI外設後,NSS拉高。

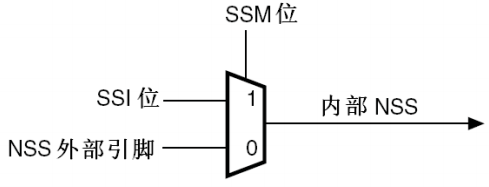

2.4.2 輸入模式

NSS輸入又分為硬體輸入和軟體控制輸入兩種模式。

軟體模式

1 對於SPI主機

需要設置SPI_CR1寄存器的SSM為1和SSI位為1,SSM為1是為了使能軟體從設備管理。NSS有內部和外部引腳,這時候,外部引腳留作他用(可以用來作為GPIO驅動從設備的片選信號)。內部NSS引腳電平則通過SPI_CR1寄存器的SSI位來驅動。SSI位為1可使NSS內電平為高電平。STM32手冊上說,要保持MSTR和SPE位為1,也就是說要保持主機模式,只有NSS接到高電平信號時,這兩位才能保持置1。也就是說對於STM32的SPI,要保持為主機狀態,內部輸入的NSS電平必須為高。當然這裡在硬體模式下也是如此。

圖11 相關引腳關係圖

#define SPI_Mode_Master ((uint16_t)0x0104)

主機模式下,會將MSTR和SSI置1,軟體模式下SSM也為1,外部引腳完全被釋放,可用作他用。

2 對於SPI從機

如果從機選擇STM32的一個SPI,譬如主機選為SPI1,從機選為SPI2,則要按照操作手冊,NSS引腳在完成位元組傳輸之前必須連接到一個低電平信號。在軟體模式下,則需要設置SPI_CR1寄存器的SSM為1(軟體從設備管理使能)和SSI位為0,也就是SPI2的片選為低,則片選成功。

若從機為一個其他的SPI晶元,那麼,我們可以有兩種方法:一種方法,是把晶元的CS接到GND上,另一種方法是,用一個GPIO口去輸出低電平來控制CS片選成功。這個GPIO可以是任何一個GPIO口,當然我們上面提到當SPI的主機配置為軟體模式,外部NSS引腳留作他用了,它就是一個GPIO了,我們也可以用它。這時候,我們可以設置它推輓輸出為低電平,然後用線跟從機的CS相連,那麼就可以片選從晶元了。

硬體模式

對於主機,我們的NSS可以直接接到高電平,對於從機,NSS接低就可以。當然我們上面提過當一個主機的SSOE為1時,主機工作在輸出模式,而且NSS拉低了,我們要讓從機片選,只要將CS接到主機的NSS上,CS自動拉低。

3 實例介紹

3.1 從機

這裡使用淘寶買的USB轉SPI工具進行測試,為了避免廣告嫌疑如需要該工具請自己在淘寶上進行搜索。

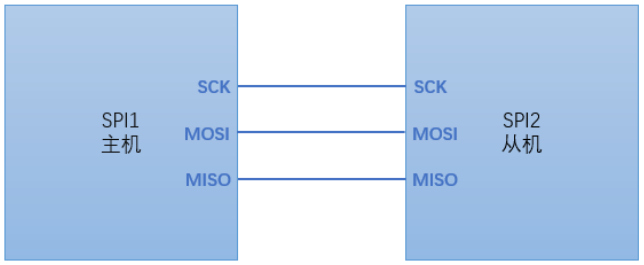

3.2 主從互發

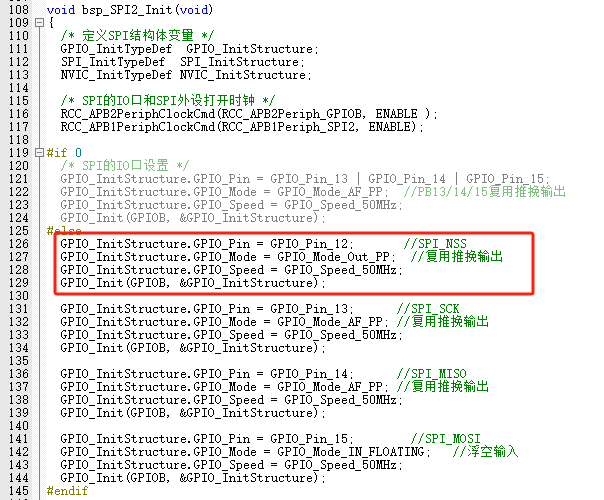

這裡選則SPI1作為主機,SPI2作為從機,

此外,在我這邊進行測試時,把從機部分NSS Pin腳的配置設置為推輓輸出更為穩定,暫時不清楚原理。

3.3 flash讀寫

該實例的例子網上比較多,就不再單獨進行上傳了!