目錄一、微處理器與匯流排1.微處理器的概述1.1 運算器1.2 控制器1.2.1 指令控制1.2.2 時序控制1.2.3 操作控制二、8086/8088微處理器1.8086/8088CPU的指令特點1.1 指令流水線1.2 記憶體的分段管理技術1.3 支持多處理器系統2.8088/8086的外部引腳及其 ...

目錄

一、微處理器與匯流排

1.微處理器的概述

首先要記得微處理器(CPU)是由下麵三個部件組成的:

運算器、控制器、寄存器組,其中,寄存器組可以看成是運算器部件中的一個部分。

微處理器(CPU)是電腦系統的核心部件,控制和協調著電腦系統的工作。

1.1 運算器

運算器由算術邏輯單元ALU、通用或專用寄存器組及內部匯流排3個部分組成。

運算器核心功能是:實現數據的算術運算和邏輯運算。

其中算術邏輯單元ALU的內部包括負責加、減、乘、除運算的加法器以及實現與、或、非、異或運算的邏輯功能部件。

運算器可分為單匯流排結構、雙匯流排結構和三匯流排結構。

1.2 控制器

控制器主要的功能是控製程序的執行,是整個系統的指揮中心。

它有如下的幾個功能:

1.2.1 指令控制

根據指令所在的地址按順序或在遇到轉移指令時按照轉移地址取出指令,分析指令(指令解碼),傳送必要的操作數,併在指令結束後存放運算結果。

1.2.2 時序控制

指令的執行是在時鐘信號的嚴格控制下進行的,一條指令的執行時間稱為指令周期,不同的指令的指令周期是不一樣的,而機器周期中包含多少個節拍也是不一樣的,這些時序信號用於電腦的工作基準。

1.2.3 操作控制

操作控制是根據指令,確定在指令周期的各個節拍中要產生的微操作控制信號,以便完成各條指令的操作過程。

控制器內部主要由下麵幾個部分組成:

1.程式計數器PC

用來存放下一條要執行的指令在存儲器中的地址

2.指令寄存器IR

存放待執行的指令

3.指令解碼器ID

將指令進行翻譯

4.時序控制部件

產生電腦工作所需的各種時序信號

5.微操作控制部件

二、8086/8088微處理器

其中重點說的是8086CPU。

8086和8088是同時代的微處理器,都屬於第三代CPU,具有完全系統的指令系統,但是8088的外部匯流排寬度為8位,8086的數據匯流排的寬度為16為。但是它們內部的匯流排寬度都是為16位的。

1.8086/8088CPU的指令特點

1.1 指令流水線

在程式的執行過程中,CPU都是按照下麵的順序來執行的:

1.取出下一條指令

2.分析指令(解碼)

3.讀操作數(根據需要)

4.執行指令(包括算術邏輯運算、I/O操作、數據傳送、控制轉移)

5.寫結果(根據需要)

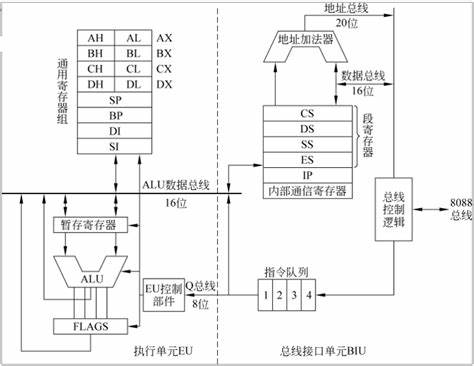

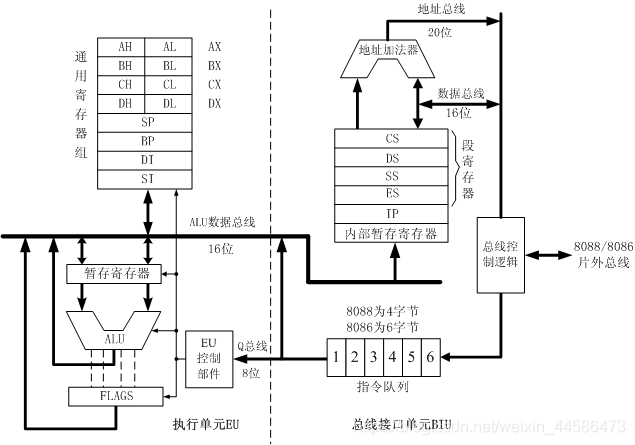

8088/8086的內部電路大致分為兩大部件:執行單元(EU)和匯流排介面單元(BIU)。

執行單元EU負責分析指令和執行指令。

匯流排介面單元BIU負責取指令、取數據和寫結果。

兩個單元能夠獨立地完成各自相應的工作,在大多數情況下,取指令操作和執行指令操作可以重疊進行。重疊進行就是一個並行流水線。

1.2 記憶體的分段管理技術

將8086/8088內部分為多個邏輯段,每個邏輯段最大為64K,為每個段設置段地址和偏移地址。

1.3 支持多處理器系統

在8086/8088中有一個引腳可以控制工作模式為最小或者最大方式。

最小模式:單處理器模式,所有信號又8086直接產生,不支持DMA。

最大方式:多處理器模式,能支持系統中的多個處理器,由匯流排控制器輔助提供控制信號。

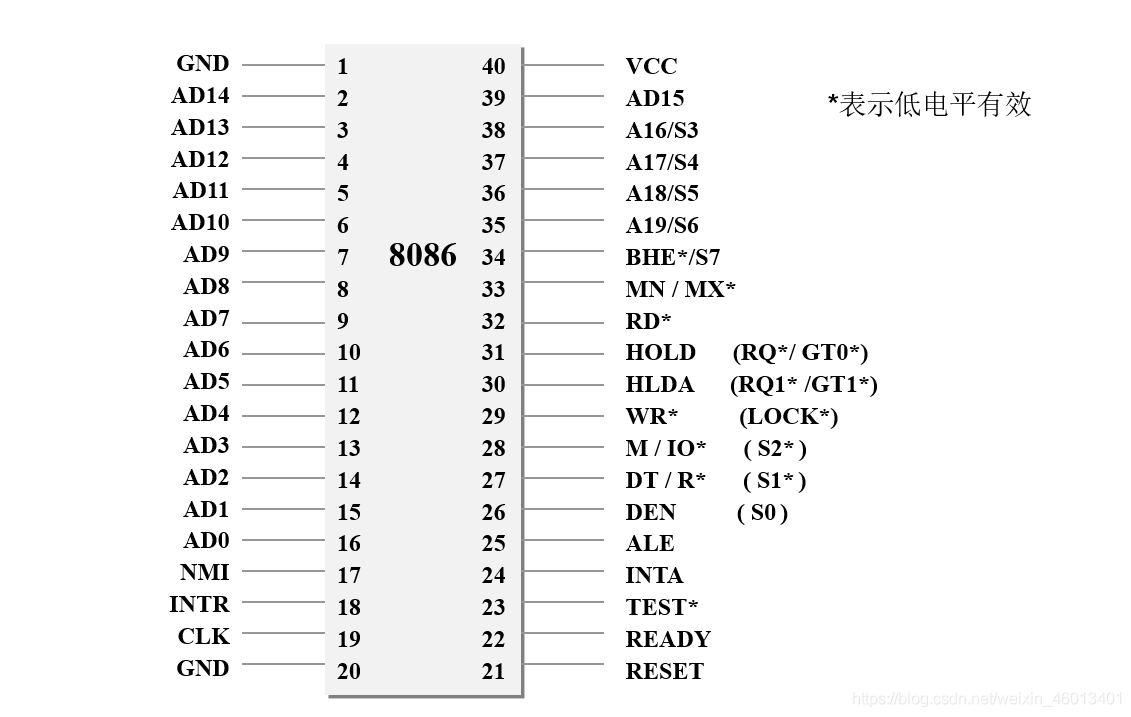

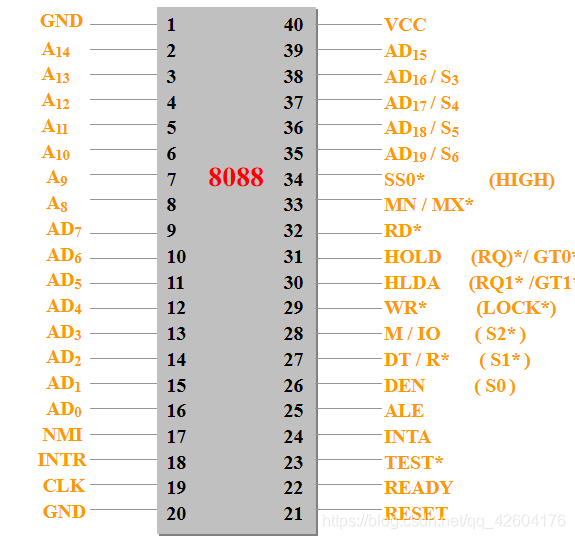

2.8088/8086的外部引腳及其功能

兩個CPU的外部引腳都差不多一樣,但是還是一些地方有所不同,比如34號引腳,28號引腳

34號引腳。86是BHE#/S7,而88是SS0#,對於86來說,34號引腳主要是控制AD0~AD15的使用情況的,但是單考這個引腳是不可以的,還要結合A0引腳

| BHE# | A0 | 描述 | 啟動引腳 |

|---|---|---|---|

| 0 | 0 | 兩個位元組 | AD15~AD0 |

| 0 | 1 | 奇地址高位 | AD15~AD8 |

| 1 | 0 | 偶地址低位 | AD7~AD0 |

而88的SS0引腳與IO/M#和DT/R#信號決定了最小模式下當前匯流排周期的狀態:

| IO/M# | DT/R# | SS0# | 操作 |

|---|---|---|---|

| 1 | 0 | 0 | 發中斷響應信號 |

| 1 | 0 | 1 | 讀IO埠 |

| 1 | 1 | 0 | 寫IO埠 |

| 1 | 1 | 1 | 暫停 |

| 0 | 0 | 0 | 取指令 |

| 0 | 0 | 1 | 讀記憶體 |

| 0 | 1 | 0 | 寫記憶體 |

| 0 | 1 | 1 | 無作用 |

可以發現,如果是讀的操作,那SS0都是非有效位,但是寫或者是取的操作,那麼SS0就是有效的。

28號引腳中,8088和8086雖然看起來相同,但是它們高低電頻的有效是不一樣的

| CPU | IO/M=0 | IO/M=1 |

|---|---|---|

| 8086 | IO | M |

| 8088 | M | IO |

A16/S3~A19/S6是地址狀態復用的引腳,三態輸出。

其中S3~S6是狀態信號線,S6恆等於0,S5指示中斷允許標誌位IF的狀態,S4和S3的組合指示CPU當前正在使用的段寄存器:

| S4 | S3 | 當前正在使用的段寄存器 |

|---|---|---|

| 0 | 0 | ES |

| 0 | 1 | SS |

| 1 | 0 | CS或未使用任何段寄存器 |

| 1 | 1 | DS |

AD0`AD7`和`AD8`AD15,其中8088只有0到7。這是地址、數據分時復用的雙向信號線,也是有三態。

其中,當ALE引腳為高電平時,這些引腳上傳輸的是地址信號;當DEN#為低電平時,這些引腳上傳輸的是數據信號。

WR#這個引腳是寫信號輸出,三態,當這個引腳輸出低電平時,表示CPU正在對存儲器或者IO口進行寫操作。

DT/R#表示數據傳送方向控制信號:

| 電平 | 執行的操作 |

|---|---|

| 1 | CPU向存儲器或IO介面發送數據 |

| 0 | 存儲器或IO介面向CPU發送數據 |

ALE引腳是地址鎖存器信號,當它有效時,表明CPU地址線上有有效信號。

DEN#數據允許信號。

RD#讀選信號,當有效時,表明CPU正在讀取存儲器或者IO介面。

READY外部同步控制輸入信號,這個位置是又外部被訪問的記憶體或IO設備發出的相應信號,當有效時,表示IO設備或存儲器準備就緒。如果沒有準備好,CPU的T3周期採樣READY信號,若還是一直沒準備好,那CPU會自動插入等待周期Tw,這個Tw一個或者多個,直到READY就緒。

INTR可屏蔽中斷請求輸入信號。

TEST#測試信號輸入引腳。

NMI非屏蔽中斷請求輸入信號。

RESET系統複位輸入信號,這個信號需要在4個時鐘周期保持有效才能進行複位,複位後CPU內部段寄存器的狀態如下:

| 內部寄存器 | 內容 |

|---|---|

| CS | FFFFH |

| DS | 0000H |

| ES | 0000H |

| SS | 0000H |

| IP | 0000H |

| FLAGS | 0000H |

| 其餘寄存器 | 0000H |

| 指令隊列 | 空 |

INTA#中斷響應信號輸出,當CPU對中斷請求信號INTR的響應,這個引腳有效。

HOLD匯流排保持請求信號輸入。

HOLA匯流排保持響應輸出。

CLK時鐘信號輸入引腳。

上面都是最小系統的時候,因為考試只考最小系統的引腳,所以這裡重點講的就是最小系統,最大系統不考。

3.8086/8088的功能結構

這主要講的是內部的執行單元EU和匯流排介面單元BIU的一些概念和CPU內部的一些寄存器組還要標註寄存器FLAGS,很重要。

3.1內部結構

86和88內部極為相似,但也有不同,88的指令隊列只有4位,而86的指令隊列有6位,其餘的都是相同的。

上面的是88的內部結構

下麵的是86的內部結構,可以看到,出來指令隊列的長度以外,其餘的都是一樣的。

匯流排介面單元BIU主要實現CPU與存儲器或IO介面之間的數據傳送,它由地址加法器、段寄存器、匯流排控制邏輯、指令隊列以及內部暫存寄存器組成。

執行單元EU主要的功能是:執行指令、分析指令、暫存中間運算結果並保留結果的特征,它由通用寄存器、暫存寄存器、算術邏輯單元ALU、標誌寄存器FLAGS和EU控制部件組成。

他們工作如下:

1.EU從執行隊列中取出指令後,指令隊列出現空位元組時,那麼BIU就自動執行一次取指令周期,講取出來的指令放入指令隊列中。

2.如果EU需要數據時,BIU根據EU提供的地址從給定的地址去尋找出數據供EU進行使用。

3.運算結束後,BIU會將需要的數據送入指定的記憶體單元或外設中。

4.如果指令隊列為空,EU需要進行等待,直到有指令為止。

5.當BIU正在取指令,EU發出訪問匯流排的請求,則必須等BIU取指令完畢後該請求才能得到響應。

3.2 內部寄存器

88和86都有14個16位的寄存器,按照功能可以分為:通用寄存器、段寄存器、控制寄存器。

3.2.1 通用寄存器

通用寄存器又分為數據寄存器、地址指針寄存器和變址寄存器。

數據寄存器有4個:

| 寄存器名 | 名稱 | 通常用法 |

|---|---|---|

| AX | 累加器 | 用來存放算術邏輯運算的操作數,一般IO指令都使用累加器與外設介面來傳送信息 |

| BX | 基址寄存器 | 常用來存放訪問記憶體時的基地址 |

| CX | 計數寄存器 | 在迴圈和串操作指令中用作計數器 |

| DX | 數據寄存器 | 在寄存器間接定址的IO指令中存放IO埠的地址 |

這4個寄存器都可以拿來存放數據,只不過它們有各自的使用習慣,就是那些用法,用特點的功能使用的速度會很快。

而數據寄存器可以分為兩個8位的寄存器:

| 寄存器名1 | 寄存器名2 | 名稱 |

|---|---|---|

| AH | AL | 累加器 |

| BH | BL | 基址寄存器 |

| CH | CL | 計數寄存器 |

| DH | DL | 數據寄存器 |

地址指針寄存器只有兩個,SP和BP

| 寄存器名 | 名稱 | 用法 |

|---|---|---|

| SP | 堆棧指針寄存器 | 永遠指向堆棧的棧頂 |

| BP | 基址指針寄存器 | 一般存放記憶體的基地址,通常和SS(堆棧段寄存器)一起使用 |

它們兩個也可以存放數據,但是一般用來存放記憶體的地址。

變址寄存器只有兩個,DI和SI:

| 寄存器名稱 | 名稱 | 用法 |

|---|---|---|

| DI | 目的變址寄存器 | 索引指針 |

| SI | 源變址寄存器 | 索引指針 |

3.2.2 段寄存器

| 寄存器名 | 名稱 |

|---|---|

| CS | 代碼段寄存器 |

| DS | 數據段寄存器 |

| SS | 堆棧段寄存器 |

| ES | 附加段寄存器 |

3.2.3 控制寄存器

| 寄存器名稱 | 名稱 |

|---|---|

| IP | 指令指針寄存器 |

| FLAGS | 標誌寄存器 |

IP指針寄存器中用來存放預取指令的偏移地址。

FLAGS標誌寄存器是一個16位的寄存器,但只能使用其中的9位,這9位中有6個狀態標誌位和3個控制標誌,狀態和控制標誌位如下:

| 標誌位 | 名稱 | 用法 |

|---|---|---|

| CF | 進位標誌位 | 當CF=1時,則表示最高位向前有進(借)位 |

| AF | 輔助標誌位 | 當AF=1時,則表示D3向D4有進(借)位。 |

| PF | 奇偶標誌位 | 當運算結果的低8位中1的個數為偶數時,PF=1。 |

| SF | 符號標誌位 | 如果運算的結果是正數,那SF=0。 |

| ZF | 零標誌位 | 如果運算的結果為0,則ZF=1。 |

| OF | 溢出標誌位 | 當運算的結果超出了範圍,那麼OF=1。 |

| 控制位 | 名稱 | 用法 |

|---|---|---|

| IF | 中斷允許標誌位 | IF=1時,使CPU可以響應可屏蔽中斷請求。 |

| TF | 陷阱標誌位 | TF=1時,激活CPU的調試特性,使CPU處於單步執行指令的方式。 |

| DF | 方向標誌位 | DF=1,按照減地址方式進行,從高地址開始,每進行一次操作,地址減一。DF=0,按照增地址方式進行,從低地址開始,每進行一次,地址增1。 |

3.3 存儲器組織

3.3.1 存儲器地址空間

86和88的儲存是以位元組為地位組織的,它們具有20條地址線,可定址的存儲器空間為220,每個位元組對應一個唯一的地址,地址範圍為0~220 - 1。

存儲器存取的基本單元為位元組,存儲器內兩個連續的空間稱為一個字,也就是2個位元組=1個字,字的低位位元組存放在低地址中,高位元組存放在高地址中,字的地址為低位元組的地址,各位的編號從0開始。

86允許字從任何地址開始,如果字的地址為偶地址時,也就是用偶數的地址開始,稱字的儲存是對準的,訪問一個對準的字需要一個匯流排周期。

如果字的地址為奇地址開始,那麼稱這個字是非對準的字,訪問一個非對準的字需要兩個匯流排周期。

3.3.2 物理地址和邏輯地址

88和86外部有20根地址線,可以訪問220的記憶體,但是在內部只有16根地址匯流排,只能訪問216的記憶體,如果要讓它能訪問2^20的記憶體,88和86採用了地址空間分段的方法來解決做個問題,就是將1M空間分為若幹個64K的段,然後用基地址加上偏移地址來訪問物理存儲器。

各邏輯段的起始地址的最低4位必須為0.

為了得到一個物理地址,需要使用下麵的公式來計算:

物理地址=段地址*16+偏移地址

段地址和偏移地址的組合又稱為邏輯地址,表示形式為:xxxxH:yyyyH,其中xxxxH是段地址,yyyyH是偏移地址。

比如有下麵的邏輯地址:3A00H:12FBH,那麼它指向的物理地址為:3B2FBH。

3.3.3 段寄存器的使用

分段的話也可以將信息按照特征進行分段處理,按照信息特征可分為:

- 數據段--用來存放數據和運算結果

- 代碼段--用來存放程式的指令代碼

- 堆棧段--用來傳遞參數、保持數據和狀態信息

- 附加段--用來存放數據和運算結果

對於訪問不同的記憶體段所使用的段寄存器和偏移地址的來源有一些具體約定:

| 記憶體訪問類型 | 預設段寄存器 | 可重設寄存器 | 段內偏移地址的來源 |

|---|---|---|---|

| 取指令 | CS | 無 | IP |

| 堆棧操作 | SS | 無 | SP |

| 串操作之源串 | DS | ES、SS | SI |

| 串操作之目標串 | ES | 無 | DI |

| BP用作基址定址 | SS | ES、DS | 按定址方式計算得到有效地址 |

| 一般數據存取 | DS | ES、SS | 按定址方式計算得到有效地址 |

3.4 工作時序

時序可分為兩種不同的粒度:時鐘周期和匯流排周期。

一條指令的執行需要若幹個匯流排周期才能完成,而一個匯流排周期又由若幹個時鐘周期構成。

微處理器在運行過程中是按照一個統一的時鐘一步一步的執行每一個操作的,每個時鐘脈衝的持續時間就稱為一個時鐘周期,時鐘周期越短,CPU執行速度越快。

一個典型的匯流排周期基本包含4個時鐘周期。

一個匯流排周期=4個時鐘周期

4.匯流排

4.1 概述

匯流排是一組信號線的集合,是電腦系統各部件中間傳輸地址、數據和控制信息的公共通路。

匯流排包括一組導線和相關控制、驅動電路組成,每一條導線都能傳輸一位二進位信息。

匯流排上連接的部件過多時,會減低信號響應的實時性。

4.2 匯流排的分類

匯流排可以按照傳輸的類型和層次結構來分類。

匯流排按照傳輸信息的類型可分為:數據匯流排DB、地址匯流排AB、控制匯流排CB。

按照層次結構可分為:前端匯流排、系統匯流排和外設匯流排。

4.3 匯流排的結構

匯流排結構可分為兩種:單匯流排結構和多匯流排結構。

單匯流排結構是將電腦的各個部件均掛接到一條匯流排上,這種接法的優點是控制簡單、擴充方便,缺點是數據傳輸的效率和速度收到了限制。

多匯流排結構又分為:雙匯流排結構、多匯流排結構。

雙匯流排結構又分為面向CPU的雙匯流排結構和麵向存儲器的雙匯流排結構。

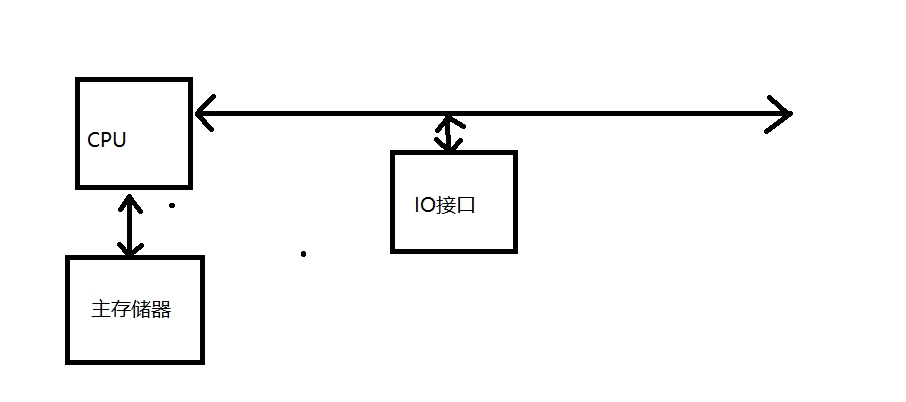

面向於CPU的雙匯流排結構:

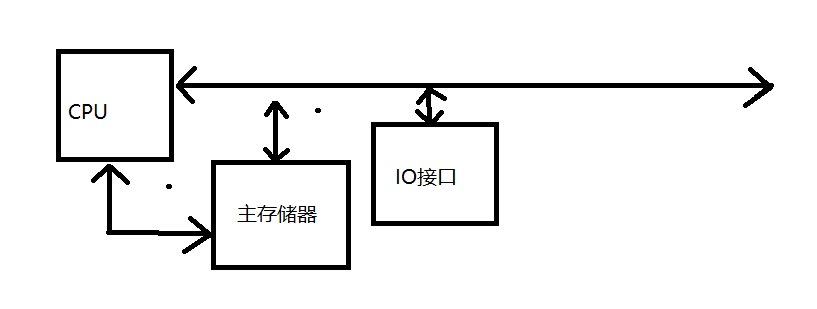

面向於存儲器的雙匯流排結構:

4.4 匯流排的操作

匯流排操作的特點:任意時刻,匯流排上只能允許一對設備(主控設備和從屬設備)進行信息交換。

匯流排周期可分為5個步驟:

- 匯流排請求

- 匯流排仲裁

- 定址

- 傳送數據

- 傳送結束

4.5 匯流排的主要性能指標

- 匯流排帶寬

- 匯流排位寬

- 匯流排的工作頻率

4.6 匯流排的基本功能

- 匯流排傳輸同步

- 匯流排仲裁控制

- 出錯處理

- 匯流排驅動