1.S5PV210 概述 1.1 架構概述 S5PV210 是一款 32 位 RISC 高性價比、低功耗、高性能的微處理器解決方案,適用於手機和一般應用。它集成了ARM Cortex-A8內核,實現了ARM架構V7-A,支持外設。 為3G和3.5G通信業務提供優化的硬體(H/W)性能,S5PV210 ...

目錄

1.S5PV210 概述

-

1.1 架構概述

S5PV210 是一款 32 位 RISC 高性價比、低功耗、高性能的微處理器解決方案,適用於手機和一般應用。它集成了ARM Cortex-A8內核,實現了ARM架構V7-A,支持外設。

為3G和3.5G通信業務提供優化的硬體(H/W)性能,S5PV210採用64位內部匯流排架構。這包括許多用於運動視頻處理、顯示控制和縮放等任務的強大硬體加速器。集成多格式編解碼器 (MFC) 支持 MPEG-1/2/4、H.263 和 H.264 的編碼和解碼,以及 VC1 的解碼。

此硬體加速器 (MFC) 支持實時視頻會議和模擬電視輸出、用於 NTSC 的 HDMI 和 PAL 模式。

S5PV210 具有與外部存儲器的介面,能夠維持高端通信服務所需的大量存儲器帶寬。存儲器系統具有用於並行訪問的 Flash/ROM 外部存儲器埠和 DRAM 埠,以滿足高帶寬。 DRAM 控制器支持 LPDDR1(移動 DDR)、DDR2 或 LPDDR2。

Flash/ROM 埠支持 NAND Flash、NOR-Flash、OneNAND、SRAM 和 ROM 類型的外部存儲器。

為了降低系統總成本並增強整體功能,S5PV210 包括許多硬體外設,例如 TFT 24 位真彩色 LCD 控制器、攝像頭介面、MIPI DSI、CSI-2、電源管理系統管理器、ATA 介面、四個 UART、 24 通道 DMA、五個定時器、通用 I/O 埠、三個 I2S、S/PDIF、三個(通用)IIC-BUS 介面、兩個 HS-SPI、USB Host 2.0、高速運行的 USB 2.0 OTG (480Mbps) 、四個 SD 主機和高速多媒體卡介面,以及四個用於時鐘生成的 PLL。

帶有 MCP 的包上包 (POP) 選項可用於小尺寸應用。

-

1.2 S5PV210 框圖

S5PV210 的完整框圖如圖 1-1 所示。

-

1.3 S5PV210的主要特性

S5PV210 的主要特性包括:

• 帶有 NEON 的基於 ARM CortexTM-A8 的 CPU 子系統

− 32/ 32 KB I/D 緩存,512 KB L2 緩存

− 工作頻率高達 800 MHz 或 1 GHz

• 64 位多層匯流排架構

− ARM CortexTM-A8 的 MSYS 域、3D 引擎、多格式編解碼器和中斷控制器

• 工作頻率高達 200 MHz

− DSYS 域主要用於 Display IP(如 LCD 控制器、Camera interface 和 TVout)和 MDMA

• 工作頻率高達 166 MHz

− PSYS 域主要用於其他系統組件,例如系統外設、外部存儲器介面、外圍 DMA、連接 IP 和音頻介面。

• 工作頻率高達 133 MHz

− 用於低功耗音頻播放的音頻域

• 移動應用的高級電源管理

• 64 KB ROM 用於安全啟動和 96 KB RAM 用於安全功能

• 8 位 ITU 601/656 相機介面支持水平尺寸高達 4224 像素的縮放和 8192 像素的未縮放解析度

• 多格式編解碼器提供高達 1080p@30fps 的 MPEG-4/H.263/H.264 編碼和解碼以及高達 1080p@30 fps 的 MPEG-2/VC1 視頻解碼

• 具有可編程著色器的 3D 圖形加速高達 2000 萬個三角形/秒和 1000 個百萬像素/秒

• 2D 圖形加速高達 160Mpixels/s

• 1/ 2/ 4/ 8 bpp Palletized 或 8/ 16/ 24 bpp Non-Palletized 彩色 TFT 建議高達 XGA 解析度

• 電視輸出和 HDMI 介面支持 NTSC 和 PAL 模式,帶有圖像增強器

• MIPI-DSI 和 MIPI-CSI 介面支持

• 1 個 AC-97 音頻編解碼器介面和 3 通道 PCM 串列音頻介面

• 三個 24 位 I2S 介面支持

• 1 個 TX only S/PDIF 介面支持數字音頻

• 三個 I2C 介面支持

• 兩個 SPI 支持

• 四個 UART 支持三個用於藍牙 2.0 的 Mbps 埠

• 片上 USB 2.0 OTG 支持高速(480 Mbps,片上收發器)

• 片上 USB 2.0 主機支持

• 非同步數據機介面支持

• 四個 SD/ SDIO/ HS-MMC 介面支持

• ATA/ATAPI-6 標準介面支持

• 24 通道 DMA 控制器(8 通道用於記憶體到記憶體 DMA,16 通道用於外設 DMA)

• 支持 14x8 鍵矩陣

• 10 通道 12 位多路復用 ADC

• 可配置的 GPIO

• 實時時鐘、PLL、PWM 定時器和看門狗定時器

• 系統定時器支持在掉電模式(睡眠模式除外)下提供準確的滴答時間

• 記憶體子系統

− 帶有 x8 或 x16 數據匯流排的非同步 SRAM/ ROM/ NOR 介面

− NAND 介面與 x8 數據匯流排

− 帶 x16 數據匯流排的復用/解復用 OneNAND 介面

− LPDDR1 介面與 x16 或 x32 數據匯流排(高達 400 Mbps/pin DDR)

− DDR2 介面與 x16 或 x32 數據匯流排(高達 400 Mbps/pin DDR)

− LPDDR2 介面(高達 400 Mbps/pin DDR) -

1.3.1 微處理器

- 該微處理器的主要特性包括:

• ARM CortexTM-A8 處理器是第一款基於ARMv7 架構的應用處理器。

• ARM CortexTM-A8 處理器能夠將速度擴展到 1 GHz,滿足功耗優化的移動設備的要求,這些設備要求以低於 300mW 的速度運行;性能優化的消費類應用程式需要 2000 Dhrystone MIPS。

• 支持首個採用 ARM 技術的超標量處理器,用於增強代碼密度和性能,NEONTM 技術用於多媒體和信號處理,以及 Jazelle® RCT 技術用於增強代碼密度和性能。

Java 和其他位元組碼語言的提前和即時編譯。

• ARM CortexTM-A8 的其他特性包括:

− Thumb-2 技術可實現更高的性能、能效和代碼密度

− NEOTM 信號處理擴展

− Jazelle RCT Java 加速技術

− 用於安全交易和 DRM 的 TrustZone 技術

− 13 級主整數流水線

− 10 級 NEOTM 媒體管道

− 使用標準編譯 RAM 的集成 L2 緩存

− 針對性能和功耗優化的 L1 緩存

- 該微處理器的主要特性包括:

-

1.3.2 記憶體子系統

記憶體子系統的主要特性包括:

• 高帶寬記憶體矩陣子系統

• 兩個獨立的外部存儲器埠(1 x16 靜態混合存儲器埠和 2 x32 DRAM 埠)

• 矩陣架構通過同時訪問能力增加了整體帶寬

− SRAM/ ROM/ NOR 介面

o x8 或 x16 數據匯流排

o 地址範圍支持:23 位

o 支持非同步介面

o 支持位元組和半字訪問

− OneNAND 介面

o x16 數據匯流排

o 地址範圍支持:16 位

o 支持位元組和半字訪問

o 支持 OneNAND 和 Flex OneNAND

o 支持專用 DMA

− NAND 介面

o 支持行業標準 NAND 介面

o x8 數據匯流排

− LPDDR1 介面

o x32 數據匯流排,400 Mbps/pin 雙倍數據速率 (DDR)

o 1.8V 介面電壓

o DMC0 埠支持高達 4 Gb,DMC1 埠支持高達 8 Gb

− DDR2 介面

o x32 數據匯流排,具有 400 Mbps/引腳雙倍數據速率 (DDR)

o 1.8V 介面電壓

o DMC0 埠支持高達 4 Gb,DMC1 埠支持高達 8 Gb

o 在 8 bank 的情況下,DMC 0&1 中只有 1 個 CS 可用

− LPDDR2 介面

o x32 數據匯流排,速率高達 400 Mbps/pin

o 1.2V/1.35V 介面電壓

o DMC0 埠支持高達 4 Gb,DMC1 埠支持高達 8 Gb -

1.3.3 多媒體

多媒體的主要特點包括:

• 相機介面

− 多輸入支持

o ITU-R BT 601/656 模式

o DMA(AXI 64 位介面)模式

o MIPI (CSI) 模式

− 多輸出支持

o DMA(AXI 64 位介面)模式

o 直接 FIFO 模式

− 數字放大 (DZI) 功能

− 多相機輸入支持

− 視頻同步信號的可編程極性

− 輸入水平尺寸支持高達 4224 像素的縮放和 8192 像素的非縮放解析度

− 圖像鏡像和旋轉(X軸鏡像、Y軸鏡像、90°、180°和270°旋轉)

− 各種圖像格式生成

− 捕捉幀控制支持

− 圖像效果支持

• 多格式視頻編解碼器 (MFC)

− ITU-T H.264、ISO/IEC 14496-10

o 解碼支持 Baseline/Main/High Profile Level 4.0(靈活巨集塊排序除外)

(FMO)、任意切片排序 (ASO) 和冗餘切片 (RS))

o 編碼支持 Baseline/Main/High Profile(FMO、ASO 和 RS 除外)

− ITU-T H.263 Profile level 3

o 解碼支持 Profile3,最高可達標清解析度 30 fps(支持 H.263 附件)- 附件 I:高級幀內編碼

- 附件 J:去塊(環路)濾波器

- 附件 K:無 FMO 和 ASO 的切片結構模式

- 附件 T:修改後的量化

- 附件 D:無限制運動矢量模式

- 附件 F:高級預測模式,除了亮度的重疊運動補償

o 編碼支持 Baseline Profile(支持客戶尺寸高達 1920x1088)

− ISO/IEC 14496-2 MPEG-4

o 解碼支持 MPEG-4 Simple/Advanced Simple Profile Level5

− 編碼支持MPEG-4 Simple/Advanced Simple Profile

− ISO/IEC 13818-2 MPEG-2

o 解碼支持 Main Profile High level

o 解碼支持除 D-picture 之外的 MPEG-1

− SMPTE 421M VC-1

o 解碼支持 Simple Profile Medium Level/Main Profile High Level/Advanced Profile Level4

• JPEG 編解碼器

− 支持高達 8192x8192 的壓縮/解壓

− 支持的壓縮格式

o 輸入原始圖像:YCbCr4:2:2 或 RGB565

o 輸出 JPEG 文件:YCbCr4:2:2 或 YCbCr4:2:0 的基線 JPEG

− 支持的解壓格式(參見第 9.13 章 JPEG)

o 輸入 JPEG 文件:YCbCr4:4:4、YCbCr4:2:2、YCbCr4:2:0 的基線 JPEG 或灰色

o 輸出原始圖像:YCbCr4:2:2 或 YCbCr4:2:0

− 支持通用色彩空間轉換器

• 3D 圖形引擎 (SGX540)

− 支持通用硬體上的3D圖形、矢量圖和視頻編解碼

− 基於瓦片的架構

− Universal Scalable Shader Engine – 包含像素和頂點著色器的多線程引擎功能

− 行業標準 API 支持 –OGL-ES 1.1 和 2.0 以及 OpenVG 1.0

− 細粒度的任務切換、負載均衡和電源管理

− 先進的幾何 DMA 驅動操作,可最大限度地減少 CPU 交互

− 可編程高質量圖像抗鋸齒

− 完全虛擬化的記憶體定址,用於操作系統在統一記憶體架構中的功能

• 2D 圖形引擎

− 比特BLT

− 支持最大 8000x8000 圖像尺寸

− 視窗剪裁、90°/180°/270° 旋轉、X 翻轉/Y 翻轉

− 反向定址(X 正/負,Y 正/負)

− 全 4 操作數光柵操作 (ROP4)

− Alpha 混合(固定 Alpha 值/每像素 Alpha 值)

− 任意大小的像素圖案繪製,圖案緩存

− 16/24/32-bpp。打包的 24-bpp 顏色格式

• 模擬電視介面

− 輸出視頻格式:NTSC-M/NTSC-J/NTSC4.43/PAL-B、D、G、H、I/PAL-M/PAL-N/PAL-Nc/PAL-60

合規

− 支持的輸入格式:ITU-R BT.601 (YCbCr 4 :4 :4)

− 支持 480i/p 和 576i 解析度

− 支持複合

• 數字電視介面

− 高清多媒體介面(HDMI)1.3

− 支持高達 1080p 30Hz 和 8 聲道/112 kHz/24 位音頻

− 支持 480p、576p、720p、1080i、1080p(不支持 480i)

− 支持 HDCP v1.1

• 旋轉器

− 支持的圖像格式:YCbCr422(交錯)、YCbCr420(非交錯)、RGB565 和 RGB888

(未包裝)

− 支持旋轉角度:90、180、270、垂直翻轉、水平翻轉

• 視頻處理器:視頻處理器支持:

− BOB/ 2D-IPC 模式

− 產生 YCbCr 4:4:4 輸出以幫助混音器混合視頻和圖形

− 1/4X 至 16X 垂直縮放,帶有 4 抽頭/16 相多相濾波器

− 1/4X 至 16X 水平縮放,帶有 8 抽頭/16 相多相濾波器

− 平移和掃描、信箱和使用縮放的 NTSC/PAL 轉換

− 顯示區域內靈活縮放的視頻定位

− 1/16 像素解析度平移和掃描模式

− 靈活的後期視頻處理

o 色彩飽和度、亮度/對比度增強、邊緣增強

o BT.601 和 BT.709 之間的色彩空間轉換

− 視頻輸入源尺寸高達 1920x1080

• 視頻混合器

視頻混合器支持:

− 重疊和混合輸入視頻和圖形層

− 480i/p、576i/p、720p 和 1080i/p 顯示尺寸

− 四層(1 個視頻層、2 個圖形層和 1 個背景層)

• TFT-LCD 介面

TFT-LCD 介面支持:

− 24/ 18/ 16-bpp 並行 RGB 介面 LCD

− 8/ 6 bpp 串列 RGB 介面

− 雙 i80 介面 LCD

− 1/ 2/ 4/ 8 bpp 托盤化或 8/16/24-bpp 非托盤化彩色 TFT

− 典型實際屏幕尺寸:1024x768、800x480、640x480、320x240、160x160等

− 虛擬圖像高達 16M 像素(4K 像素 x4K 像素)

− 五個用於 PIP 或 OSD 的視窗層

− 實時疊加平面復用

− 可編程 OSD 視窗定位

− 8 位 Alpha 混合(平面/像素)

− ITU-BT601/656 格式輸出

-

1.3.4 音頻子系統

音頻子系統的主要特性包括:

• 音頻處理由可重構處理器 (RP) 推進

• 低功耗音頻子系統

− 5.1 通道 I2S,具有 32 位寬 64 深度 FIFO

− 128 KB 音頻播放輸出緩衝區

− 硬體混音器混合主要和次要聲音 -

1.3.5 安全子系統

安全子系統的主要功能包括:

• 片上安全啟動 ROM

− 64 KB 安全啟動 ROM 用於安全啟動

• 片上安全 RAM

− 96 KB 安全 RAM 用於安全功能

• 硬體加密加速器

− 安全集成的 DES/TDES、AES、SHA-1、PRNG 和 PKA

− 訪問控制(帶有 ARM TrustZone 硬體的安全域管理器)

− 為安全的單獨(安全/非安全)執行環境啟用增強的安全平臺敏感應用

• 安全 JTAG

− JTAG 用戶認證

− JTAG 模式下的訪問控制 -

1.3.6 連通性

連通性的主要特點包括:

• PCM 音頻介面

− 16 位單聲道音頻介面

− 僅主模式

− 支持三口PCM介面

• AC97 音頻介面

− 立體聲 PCM 輸入、立體聲 PCM 輸出和單聲道 MIC 輸入的獨立通道

− 16 位立體聲(2 聲道)音頻

− 可變採樣率 AC97 編解碼器介面(48 kHz 及以下)

− 支持 AC97 全規格

• SPDIF 介面(僅限 TX)

− 每個樣本支持高達 24 位的線性 PCM

− 非線性 PCM 格式,如 AC3、MPEG1 和 MPEG2 支持

− 2x24 位緩衝區,交替填充數據

• I2S 匯流排介面

− 三個 I2S 匯流排,用於基於 DMA 操作的音頻編解碼器介面

− 串列,每通道 8/16/24 位數據傳輸

− 支持I2S、MSB-justified、LSB-justified數據格式

− 支持 PCM 5.1 聲道

− 各種位時鐘頻率和編解碼器時鐘頻率支持

o 16、24、32、48 fs 的位時鐘頻率

o 256、384、512、768 fs 的編解碼器時鐘

− 支持 1 個 5.1 通道 I2S 埠(在音頻子系統中)和 2 個 2 通道 I2S 埠

• 數據機介面

− 非同步直接/間接 16 位 SRAM 式介面

− 用於直接介面的片上 16 KB 雙埠 SRAM 緩衝器

• I2C 匯流排介面

− 三個多主 IIC 匯流排

− 串列、面向 8 位和雙向數據傳輸可在標準中以高達 100 Kbit/s 的速度進行模式

− 快速模式下高達 400 Kbit/s

• ATA 控制器

− 相容 ATA/ATAPI-6 標準

• 串口

− 四個 UART,具有基於 DMA 或基於中斷的操作

− 支持 5 位、6 位、7 位或 8 位串列數據發送/接收

− UART0 的 Rx/Tx 獨立 256 位元組 FIFO、UART1 的 64 位元組 FIFO 和 UART2/3 的 16 位元組 FIFO

− 可編程波特率

− 支持 IrDA 1.0 SIR (115.2 Kbps) 模式

− 用於測試的環回模式

− 波特時鐘生成中的非整數時鐘分頻

• USB 2.0 OTG

− 符合 USB 2.0 的 OTG Revision 1.0a 補充

− 支持高達 480 Mbps 的高速

− 片上 USB 收發器

• USB 主機 2.0

− 符合 USB Host 2.0

− 支持高達 480 Mbps 的高速

− 片上 USB 收發器

• HS-MMC/SDIO 介面

− 多媒體卡協議版本 4.3 相容 (HS-MMC)

− SD 存儲卡協議版本 2.0 相容

− 基於 DMA 或基於中斷的操作

− 128 字 FIFO 用於 Tx/Rx

− 四口HS-MMC或四口SDIO

• SPI 介面

− 符合三個串列外設介面協議 2.11 版

− 用於 SPI0 的 Rx/Tx 獨立 64 字 FIFO 和用於 SPI1 的 16 字 FIFO

− 基於 DMA 或基於中斷的操作

• 通用輸入輸出口

− 237 個多功能輸入/輸出埠

− 控制 178 個外部中斷

− GPA0:8 個輸入/輸出埠 – 2xUART 帶流量控制

− GPA1:4 個輸入/輸出埠 – 2xUART 不帶流量控制或 1xUART 帶流量控制

− GPB:8 個輸入/輸出埠 – 2x SPI

− GPC0:5 個輸入/輸出埠 – I2S、PCM、AC97

− GPC1:5 個輸入/輸出埠 – I2S、SPDIF、LCD_FRM

− GPD0:4 個輸入/輸出埠 – PWM

− GPD1:6 個輸入/輸出埠 – 3xI2C、PWM、IEM

− GPE0,1:13 進/出埠 – 攝像頭介面

− GPF0,1,2,3: 30 輸入/輸出埠 – LCD 介面

− GPG0,1,2,3: 28 in/out port – 4xMMC channel (Channel 0 and 2 support 4-bit and 8-bit mode, but channel 1 and 3 only support 4-bit mode)

− GPH0、1、2、3:32 輸入/輸出埠 – 鍵盤、外部喚醒(高達 32 位)、HDMI

− GPI:低功耗 I2S、PCM

− GPJ0、1、2、3、4:35 個輸入/輸出埠——數據機 IF、CAMIF、CFCON、鍵盤、SROM ADDR[22:16]

− MP0_1,2,3: 20 in/out port – EBI (SROM, NF, CF, and OneNAND) 的控制信號

− MP0_4,5,6,7: 32 in/out memory port – EBI(有關EBI配置的更多信息,請參閱第5.6章EBI) -

1.3.7 系統外設

系統外設的主要特性包括:

• 實時時鐘 − 完整的時鐘功能:秒、分鐘、小時、日期、日、月和年

− 32.768kHz 操作

− 報警中斷

− 計時中斷

• 鎖相環

− 4 個片上 PLL,APLL/MPLL/EPLL/VPLL

− APLL 生成 ARM 內核和 MSYS 時鐘

− MPLL 生成系統匯流排時鐘和特殊時鐘

− EPLL 生成特殊時鐘

− VPLL 為視頻介面生成時鐘

• 鍵盤

− 14x8 鍵矩陣支持

− 提供內部去抖動過濾器

• 帶脈寬調製的定時器

− 具有基於中斷操作的五通道 32 位內部定時器

− 帶 PWM 的四通道 32 位定時器

− 可編程占空比、頻率和極性

− 死區生成

− 支持外部時鐘源

• 系統定時器

− 準確的計時器在除睡眠以外的任何電源模式下提供精確的 1ms 滴答

− 可以在不停止參考滴答定時器的情況下更改中斷間隔

• DMA

− 基於微碼編程的DMA

− 特定指令集為編程 DMA 傳輸提供了靈活性

− 支持鏈表DMA功能

− 支持三個增強型內置 DMA,每個 DMA 有 8 個通道,因此通道總數 支持的是 24

− 支持一種 Memory-to-memory 類型優化的 DMA 和兩種 Peripheral-to-memory 類型優化 DMA

− M2M DMA 最多支持 16 個突發,P2M DMA 最多支持 8 個突發

• A/D 轉換器和觸摸屏界面

− 10 通道多路復用 ADC

− 最大 500Ksamples/sec 和 12 位解析度

• 看門狗定時器

− 16 位看門狗定時器

• 向量中斷控制器

− 中斷設備驅動程式等軟體可以屏蔽特定的中斷請求

− 中斷嵌套的中斷源優先順序

• 能源管理

− 組件的時鐘門控控制

− 提供多種低功耗模式,例如空閑、停止、深度停止、深度空閑和睡眠模式

− 休眠模式下的喚醒源為外部中斷、RTC 鬧鐘、Tick 定時器和按鍵介面。

− 停止和深度停止模式的喚醒源是 MMC、觸摸屏界面、系統定時器和睡眠模式的整個喚醒源。

− 深度空閑模式的喚醒源為 5.1ch I2S 和停止模式的喚醒源。 -

1.4 慣例

-

1.4.1 寄存器 R/W 約定

| 符號 | 定義 | 描述 |

|---|---|---|

| R | 只讀 | 應用程式有權讀取註冊欄位。 寫入只讀欄位無效。 |

| W | 只寫 | 應用程式有權在註冊欄位中寫入。 |

| R/W | 可讀寫 | 應用程式有權在“註冊”欄位中讀取和寫入。 應用程式通過寫入 1’b1 來設置該欄位,並通過寫入 1’b0 清除它。 |

| R/WC | 讀寫清除 | 應用程式有權在“註冊”欄位中讀取和寫入。 應用程式通過寫入 1’b1 清除該欄位。 寄存器寫入 1'b0 對該欄位沒有影響。 |

| R/WS | 讀取和寫入設置 | 應用程式有權在“註冊”欄位中讀取和寫入。 應用程式通過寫入 1’b1 來設置該欄位。 寄存器寫入 1'b0 對該欄位沒有影響。 |

-

1.4.2 寄存器值約定

| 表達式 | 描述 |

|---|---|

| x | 未定義位 |

| X | 未定義的多個位 |

| ? | 未定義,但取決於設備或引腳狀態 |

| Device dependent | 該值取決於設備 |

| Pin value | 該值取決於引腳狀態 |

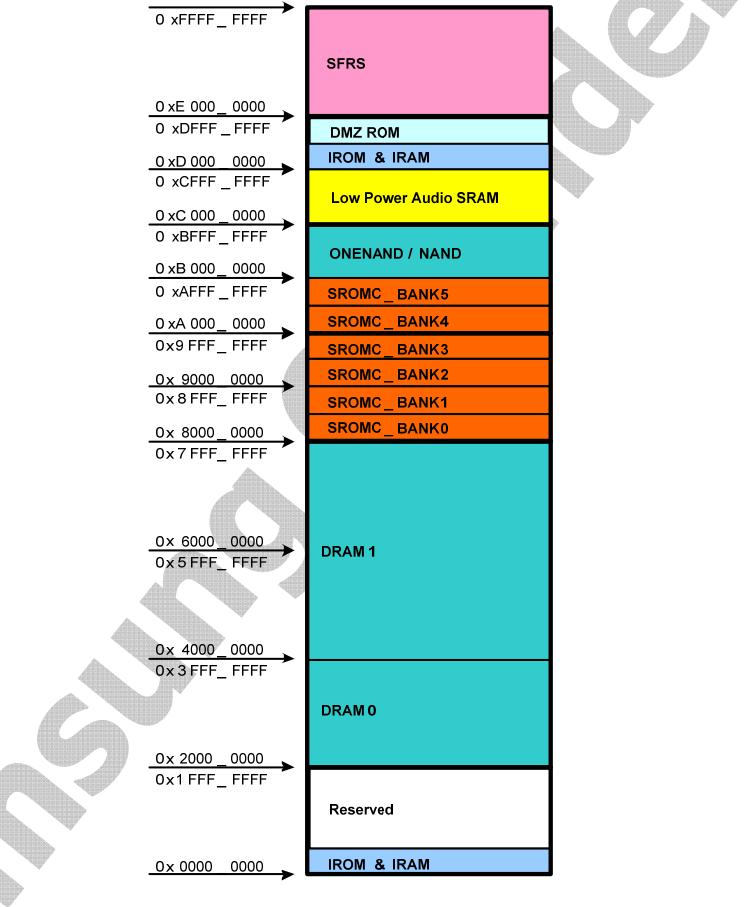

2.記憶體映射

本章介紹 S5PV210 處理器中可用的記憶體映射。

-

2.1 記憶體地址映射

-

2.1.1 設備特定地址空間

| 起始地址 | 結束地址 | 大小 | 描述(備註) |

|---|---|---|---|

| 0x0000_0000 | 0x1FFF_FFFF | 512MB | Boot area(鏡像區域取決於引導模式。) |

| 0x2000_0000 | 0x3FFF_FFFF | 512MB | DRAM 0 |

| 0x4000_0000 | 0x7FFF_FFFF | 1024MB | DRAM 1 |

| 0x8000_0000 | 0x87FF_FFFF | 128MB | SROM Bank 0 |

| 0x8800_0000 | 0x8FFF_FFFF | 128MB | SROM Bank 1 |

| 0x9000_0000 | 0x97FF_FFFF | 128MB | SROM Bank 2 |

| 0x9800_0000 | 0x9FFF_FFFF | 128MB | SROM Bank 3 |

| 0xA000_0000 | 0xA7FF_FFFF | 128MB | SROM Bank 4 |

| 0xA800_0000 | 0xAFFF_FFFF | 128MB | SROM Bank 5 |

| 0xB000_0000 | 0xBFFF_FFFF | 256MB | OneNAND/NAND Controller and SFR |

| 0xC000_0000 | 0xCFFF_FFFF | 256MB | MP3_SRAM output buffer |

| 0xD000_0000 | 0xD000_FFFF | 64KB | IROM |

| 0xD001_0000 | 0xD001_FFFF | 64KB | Reserved |

| 0xD002_0000 | 0xD003_7FFF | 96KB | IRAM |

| 0xD800_0000 | 0xDFFF_FFFF | 128MB | DMZ ROM |

| 0xE000_0000 | 0xFFFF_FFFF | 512MB | SFR region |

NOTE: TZPCR0SIZE[5:0](TZPC0); (in TZPC SFR)

- 4KByte chunks

- Recommended value: 6'b00_0000 ~ 6'b10_0000

* if (TZPCR0SIZE[5](TZPC0) == 1'b1), the full address range in iSRAM is configured as secure.

* if (TZPCR0SIZE(TZPC0) == 6'b00_0000), there is non-secure region in iSRAM (0kB).

* if (TZPCR0SIZE(TZPC0) == 6'b00_0001), the minimum secure region size is 4kB.

* if (TZPCR0SIZE(TZPC0) == 6'b01_0000), the 64KB from iSRAM start address specifies the secure region.

- iROM is always secure area

-

2.1.2 特殊功能寄存器映射

| 起始地址 | 結束地址 | 描述 |

|---|---|---|

| 0xE000_0000 | 0xE00F_FFFF | CHIPID |

| 0xE010_0000 | 0xE01F_FFFF | SYSCON |

| 0xE020_0000 | 0xE02F_FFFF | GPIO |

| 0xE030_0000 | 0xE03F_FFFF | AXI_DMA |

| 0xE040_0000 | 0xE04F_FFFF | AXI_PSYS |

| 0xE050_0000 | 0xE05F_FFFF | AXI_PSFR |

| 0xE060_0000 | 0xE06F_FFFF | TZPC2 |

| 0xE070_0000 | 0xE07F_FFFF | IEM_APC |

| 0xE080_0000 | 0xE08F_FFFF | IEM_IEC |

| 0xE090_0000 | 0xE09F_FFFF | PDMA0 |

| 0xE0A0_0000 | 0xE0AF_FFFF | PDMA1 |

| 0xE0D0_0000 | 0xE0DF_FFFF | CORESIGHT |

| 0xE0E0_0000 | 0xE0EF_FFFF | SECKEY |

| 0xE0F0_0000 | 0xE0FF_FFFF | ASYNC_AUDIO_PSYS |

| 0xE110_0000 | 0xE11F_FFFF | SPDIF |

| 0xE120_0000 | 0xE12F_FFFF | PCM1 |

| 0xE130_0000 | 0xE13F_FFFF | SPI0 |

| 0xE140_0000 | 0xE14F_FFFF | SPI1 |

| 0xE160_0000 | 0xE16F_FFFF | KEYIF |

| 0xE170_0000 | 0xE17F_FFFF | TSADC |

| 0xE180_0000 | 0xE18F_FFFF | I2C0 (general) |

| 0xE1A0_0000 | 0xE1AF_FFFF | I2C2 (PMIC) |

| 0xE1B0_0000 | 0xE1BF_FFFF | HDMI_CEC |

| 0xE1C0_0000 | 0xE1CF_FFFF | TZPC3 |

| 0xE1D0_0000 | 0xE1DF_FFFF | AXI_GSYS |

| 0xE1F0_0000 | 0xE1FF_FFFF | ASYNC_PSFR_AUDIO |

| 0xE210_0000 | 0xE21F_FFFF | I2S1 |

| 0xE220_0000 | 0xE22F_FFFF | AC97 |

| 0xE230_0000 | 0xE23F_FFFF | PCM0 |

| 0xE250_0000 | 0xE25F_FFFF | PWM |

| 0xE260_0000 | 0xE26F_FFFF | ST |

| 0xE270_0000 | 0xE27F_FFFF | WDT |

| 0xE280_0000 | 0xE28F_FFFF | RTC_APBIF |

| 0xE290_0000 | 0xE29F_FFFF | UART |

| 0xE800_0000 | 0xE80F_FFFF | SROMC |

| 起始地址 | 結束地址 | 描述 |

|---|---|---|

| 0xE820_0000 | 0xE82F_FFFF | CFCON |

| 0xEA00_0000 | 0xEA0F_FFFF | SECSS |

| 0xEB00_0000 | 0xEB0F_FFFF | SDMMC0 |

| 0xEB10_0000 | 0xEB1F_FFFF | SDMMC1 |

| 0xEB20_0000 | 0xEB2F_FFFF | SDMMC2 |

| 0xEB30_0000 | 0xEB3F_FFFF | SDMMC3 |

| 0xEB40_0000 | 0xEB4F_FFFF | TSI |

| 0xEC00_0000 | 0xEC0F_FFFF | USBOTG |

| 0xEC10_0000 | 0xEC1F_FFFF | USBOTG_PHY_CON |

| 0xEC20_0000 | 0xEC2F_FFFF | USBHOST_EHCI |

| 0xEC30_0000 | 0xEC3F_FFFF | USBHOST_OHCI |

| 0xED00_0000 | 0xED0F_FFFF | MODEM |

| 0xED10_0000 | 0xED1F_FFFF | HOST |

| 0xEE00_0000 | 0xEE8F_FFFF | AUDIO_SS |

| 0xEE90_0000 | 0xEE9F_FFFF | AUDIO_SS/ASS_DMA |

| 0xEEA0_0000 | 0xEEAF_FFFF | AUDIO_SS/ASS_IBUF0 |

| 0xEEB0_0000 | 0xEEBF_FFFF | AUDIO_SS/ASS_IBUF1 |

| 0xEEC0_0000 | 0xEECF_FFFF | AUDIO_SS/ASS_OBUF0 |

| 0xEED0_0000 | 0xEEDF_FFFF | AUDIO_SS/ASS_OBUF1 |

| 0xEEE0_0000 | 0xEEEF_FFFF | AUDIO_SS/ASS_APB |

| 0xEEF0_0000 | 0xEEFF_FFFF | AUDIO_SS/ASS_ODO |

| 0xF000_0000 | 0xF00F_FFFF | DMC0_SFR |

| 0xF100_0000 | 0xF10F_FFFF | AXI_MSYS |

| 0xF110_0000 | 0xF11F_FFFF | AXI_MSFR |

| 0xF120_0000 | 0xF12F_FFFF | AXI_VSYS |

| 0xF140_0000 | 0xF14F_FFFF | DMC1_SFR |

| 0xF150_0000 | 0xF15F_FFFF | TZPC0 |

| 0xF160_0000 | 0xF16F_FFFF | SDM |

| 0xF170_0000 | 0xF17F_FFFF | MFC |

| 0xF180_0000 | 0xF18F_FFFF | ASYNC_MFC_VSYS0 |

| 0xF190_0000 | 0xF19F_FFFF | ASYNC_MFC_VSYS1 |

| 0xF1A0_0000 | 0xF1AF_FFFF | ASYNC_DSYS_MSYS0 |

| 0xF1B0_0000 | 0xF1BF_FFFF | ASYNC_DSYS_MSYS1 |

| 0xF1C0_0000 | 0xF1CF_FFFF | ASYNC_MSFR_DSFR |

| 0xF1D0_0000 | 0xF1DF_FFFF | ASYNC_MSFR_PSFR |

| 0xF1E0_0000 | 0xF1EF_FFFF | ASYNC_MSYS_DMC0 |

| 起始地址 | 結束地址 | 描述 |

|---|---|---|

| 0xF1F0_0000 | 0xF1FF_FFFF | ASYNC_MSFR_MPERI |

| 0xF200_0000 | 0xF20F_FFFF | VIC0 |

| 0xF210_0000 | 0xF21F_FFFF | VIC1 |

| 0xF220_0000 | 0xF22F_FFFF | VIC2 |

| 0xF230_0000 | 0xF23F_FFFF | VIC3 |

| 0xF280_0000 | 0xF28F_FFFF | TZIC0 |

| 0xF290_0000 | 0xF29F_FFFF | TZIC1 |

| 0xF2A0_0000 | 0xF2AF_FFFF | TZIC2 |

| 0xF2B0_0000 | 0xF2BF_FFFF | TZIC3 |

| 0xF300_0000 | 0xF3FF_FFFF | G3D |

| 0xF800_0000 | 0xF80F_FFFF | FIMD |

| 0xF900_0000 | 0xF90F_FFFF | TVENC |

| 0xF910_0000 | 0xF91F_FFFF | VP |

| 0xF920_0000 | 0xF92F_FFFF | MIXER |

| 0xFA00_0000 | 0xFA0F_FFFF | G2D |

| 0xFA10_0000 | 0xFA1F_FFFF | HDMI_LINK |

| 0xFA20_0000 | 0xFA2F_FFFF | SMDMA |

| 0xFA30_0000 | 0xFA3F_FFFF | ROT |

| 0xFA40_0000 | 0xFA4F_FFFF | AXI_LSYS |

| 0xFA50_0000 | 0xFA5F_FFFF | DSIM |

| 0xFA60_0000 | 0xFA6F_FFFF | CSIS |

| 0xFA70_0000 | 0xFA7F_FFFF | AXI_DSYS |

| 0xFA80_0000 | 0xFA8F_FFFF | AXI_DSFR |

| 0xFA90_0000 | 0xFA9F_FFFF | I2C_HDMI_PHY |

| 0xFAA0_0000 | 0xFAAF_FFFF | AXI_TSYS |

| 0xFAB0_0000 | 0xFABF_FFFF | I2C_HDMI_DDC |

| 0xFAC0_0000 | 0xFACF_FFFF | AXI_XSYS |

| 0xFAD0_0000 | 0xFADF_FFFF | TZPC1 |

| 0xFAF0_0000 | 0xFAFF_FFFF | ASYNC_PSYS_DSYS_u0 |

| 0xFB20_0000 | 0xFB2F_FFFF | FIMC0 |

| 0xFB30_0000 | 0xFB3F_FFFF | FIMC1 |

| 0xFB40_0000 | 0xFB4F_FFFF | FIMC2 |

| 0xFB60_0000 | 0xFB6F_FFFF | JPEG |