STM32 SPI硬體NSS STM32F1的SPI NSS引腳並不是通常認為的,打開硬體NSS後在發送數據的時候NSS輸出低,去片選從設備,在發送完成後釋放從設備,硬體NSS而是用來實現多主機模式的。 當時我還以為買到了假STM32了呢。 在我們配置SPI為硬體NSS之後,配置代碼如下,發現不論發 ...

STM32 SPI硬體NSS

STM32F1的SPI NSS引腳並不是通常認為的,打開硬體NSS後在發送數據的時候NSS輸出低,去片選從設備,在發送完成後釋放從設備,硬體NSS而是用來實現多主機模式的。

當時我還以為買到了假STM32了呢。

在我們配置SPI為硬體NSS之後,配置代碼如下,發現不論發不發數據NSS都為0V;

//SPI Pins SCK MOSI

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_12|GPIO_Pin_13|GPIO_Pin_15;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;//註意這裡

GPIO_Init(GPIOB,&GPIO_InitStructure);

SPI_InitStructure.SPI_Direction = SPI_Direction_1Line_Tx;

SPI_InitStructure.SPI_Mode = SPI_Mode_Master;

SPI_InitStructure.SPI_DataSize = SPI_DataSize_8b;

SPI_InitStructure.SPI_CPOL = SPI_CPOL_High;

SPI_InitStructure.SPI_CPHA = SPI_CPHA_2Edge;

SPI_InitStructure.SPI_NSS = SPI_NSS_Hard;//註意這裡

SPI_InitStructure.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_4;

SPI_InitStructure.SPI_FirstBit = SPI_FirstBit_MSB;

SPI_InitStructure.SPI_CRCPolynomial = 7;

SPI_Init(SPI2,&SPI_InitStructure);

SPI_SSOutputCmd(SPI2,ENABLE);//註意這裡

SPI_Cmd(SPI2,ENABLE);

在閱讀Reference Manual時發現這麼一句話

This configuration is used only when the device operates in master mode. The NSS signal is driven low when the master starts the communication and is kept low until the SPI is disabled.

大概意思是:在disable SPI之後NSS才會不被拉低。於是我就這樣:

SPI_Cmd(SPI2,DISABLE);

發現NSS是0.5V左右,註意是0.5V,這裡像是開漏輸出的樣子;為什麼沒有輸出3.3V,於是在NSS上加了一個10K上拉電阻,結果NSS輸出了3.3V,這不就是開漏嗎?這也是為了能夠線與,實現多主機模式吧。

加了上拉電阻之後SPI的NSS功能就算正常啦。

Reference Manual寫到

When configured in master mode with NSS configured as an input (MSTR=1 and SSOE=0) and if NSS is pulled low, the SPI enters the master mode fault state: the MSTR bit is automatically cleared and the device is configured in slave mode

其中說到SSOE = 0,NSS配置為輸入,當NSS為低電平時,SPI 進入從機模式,也就下邊的代碼,註意這裡使用的SPI_NSS_Hard。

SPI_SSOutputCmd(SPI2,DISABLE);

在NSS未接上拉電阻的時候,NSS為邏輯0 ,那麼SPI就會進入從機模式,SCK和MOSI上無數據;接上拉電阻之後,這下就變正常啦,在NSS為高時SPI是主機模式SCK和MOSI可以輸出數據,當外部把NSS拉低後SPI就進入了從機模式。

那可不可以這樣

//SPI Pin NSS

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_12;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP;//註意這裡

GPIO_Init(GPIOB,&GPIO_InitStructure);

GPIO_WriteBit(GPIOB,GPIO_Pin_12,Bit_SET);//註意這裡

SPI_InitStructure.SPI_NSS = SPI_NSS_Hard;

SPI_SSOutputCmd(SPI2,ENABLE);//註意這裡

NSS引腳不用復用推輓輸出 ,而是用推輓輸出,也就是PB12不接入SPI,這樣NSS可以通過軟體的控制輸出高電平和低電平,也許可以省略一個上拉電阻(別問我為什麼這麼扣,為了省去一個上拉電阻大費周章,因為我的板子沒有設計上拉電阻,測試的上拉電阻是從外部接的),結論是否定的,因為推輓輸出 是這樣的

兩個SPI的NSS引腳都是推輓輸出,當一個輸出高,一個輸出低,那麼他們會各自分得1.6V的電壓,也就是邏輯1,若設置了SSOE = 0,SPI 也不會 從主機自動變成從機。

那麼可不可以這樣

//SPI Pin NSS

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_12;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_OD;//註意這裡

GPIO_Init(GPIOB,&GPIO_InitStructure);

GPIO_WriteBit(GPIOB,GPIO_Pin_12,Bit_SET);//註意這裡

SPI_InitStructure.SPI_NSS = SPI_NSS_Hard;

SPI_SSOutputCmd(SPI2,ENABLE);//註意這裡

PB12開漏輸出,然後在外部上拉一個大電阻。哈哈,這次答案是肯定的,NSS有高有低,SPI也可以進入從機模式,但是上拉電阻還是不能省啊。

PB12沒有設置成復用功能,為什麼SPI還會檢測到NSS引腳的低電平,而後進入從機模式呢?

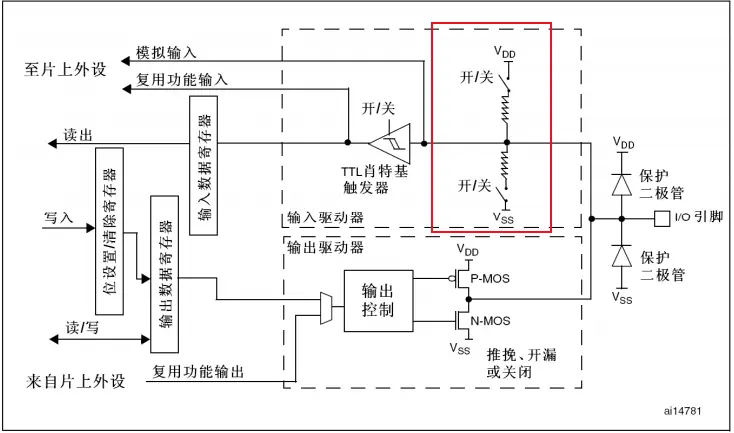

看上面STM32 GPIO的圖,會發現不管輸出設為那種模式,輸入是一直連接到STM32 內部的,這也就是為什麼 STM32 固件庫里輸入模式只有這幾種模式,而沒有復用輸入的原因。

GPIO_Mode_AIN = 0x0,

GPIO_Mode_IN_FLOATING = 0x04,

GPIO_Mode_IPD = 0x28,

GPIO_Mode_IPU = 0x48,

那怎麼才能使用多主機模式呢?

-

NSS設置成復用功能,加上拉電阻,SPI_NSS_Hard,且在不發送數據時失能NSS輸出,在要發送數據時使能NSS輸出。

-

NSS設置成開漏輸出,加上拉電阻,SPI_NSS_Hard,且在不發送數據時失能NSS輸出,在要發送數據時使能NSS輸出。

-

第2種方法真雞肋

如果只是單主機模式,那麼配置模式就比較的隨意啦。

-

NSS設置成復用功能,加上拉電阻,SPI_NSS_Hard,SPI_SSOutputCmd(SPI2,ENABLE),軟體去控制NSS。

-

NSS設置成開漏輸出,加上拉電阻或者推輓輸出,SPI_NSS_Hard,SPI_SSOutputCmd(SPI2,ENABLE),軟體去控制NSS。

-

直接NSS設置成推輓輸出,SPI_NSS_Soft,軟體去控制NSS。

-

還是第3種方法最實用。