VH6501硬體結構 1.式樣 1.正向有5個燈,用來指示干擾的觸髮狀態,干擾類型(數字或模擬),通道通信以及設備狀態。 2.兩個DB9介面(公頭male和母頭female),這是CAN或CANFD通道,單節點干擾,或多節點干擾, ,以及一個Extend觸發介面。 3.兩個DB9介面內部互聯,且PI ...

VH6501硬體結構

1.式樣

1.正向有5個燈,用來指示干擾的觸髮狀態,干擾類型(數字或模擬),通道通信以及設備狀態。

2.兩個DB9介面(公頭male和母頭female),這是CAN或CANFD通道,單節點干擾,或多節點干擾,

,以及一個Extend觸發介面。

3.兩個DB9介面內部互聯,且PIN腳定義一致。

1.反向一個USB2.0介面,連接到電腦

2.I/O介面:提供1路模擬輸入,2路數字輸入以及1路數字輸出

3.ETH,為乙太網介面

4.邊上兩個,是用於供電/同步的介面,同步用於VH6501通過同步線,與Vector其他硬體產品,實現硬體時鐘同步的作用。

選擇任意一個,給VH6501供電

2.基礎配置

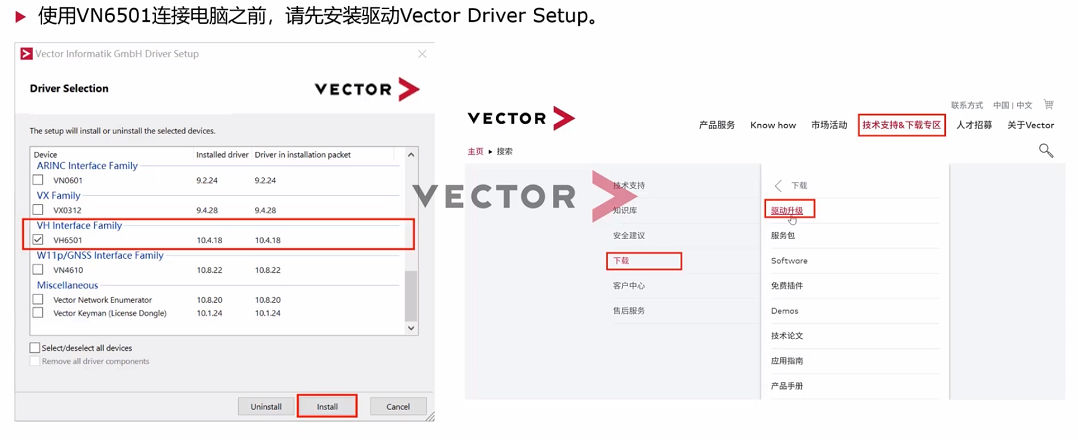

1.VH6501時,需要安裝硬體驅動。

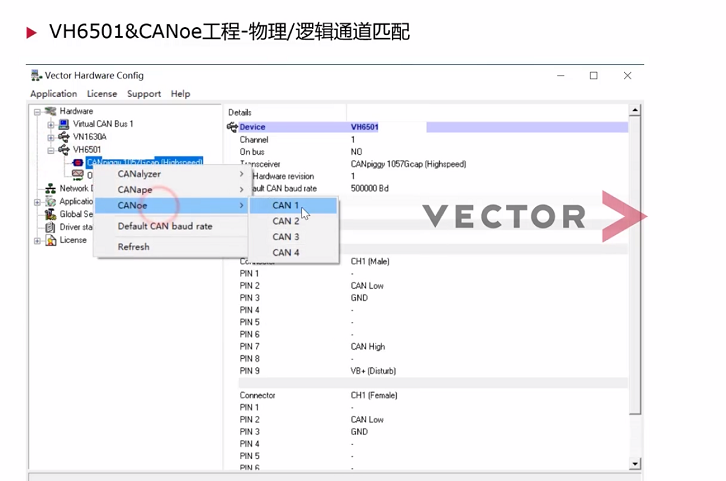

2.通道配置

選擇與CANoe工程進行物理/邏輯通道匹配關聯

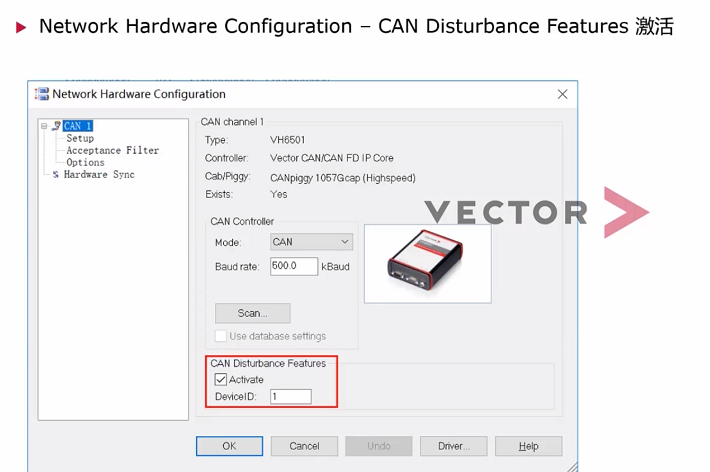

3.激活干擾功能

勾選Activate,若CANoe接入多個VH6501,則需要設置DeviceID,通過不同的ID,標識不同的VH6501設備。

CANDisturbance工程(sample configuration)介紹

工程位置:CANoe-File-Sample Configuration-CANDisturbance

通過Disturbance Interface工程可實現的干擾有:

External Trigger:外部觸發,使用VH6501的I/O口作為觸發源。

Frame Trigger:報文觸發,設定被干擾報文的觸發位置,併發送干擾位序列/報文

Software Trigger:軟體觸發,是配置好干擾序列厚,直接發送。

Error Frame Trigger:錯誤幀觸發,是基於錯誤標識為觸發條件觸發干擾。

Direction Trigger:方向觸發。根據Tx/Rx發送/接收方作為觸發條件。

Inverted Trigger:反向觸發。可對已定義的觸發條件反向觸發干擾。

Missing Bit Trigger :缺失位觸發,用於CANFD CRC長度不確定的情況觸發。

Scope Trigger:示波器觸發,VH6501干擾後,輸出一個脈衝信號至示波器。

數字干擾示例

使用VH6501干擾ID 0X100報文的ACK界定符位,將ACK Delimiter位從預設隱性1(Recessive)干擾成顯性0(Dominant),從而監測到Form Error格式錯誤,併發出錯誤幀。

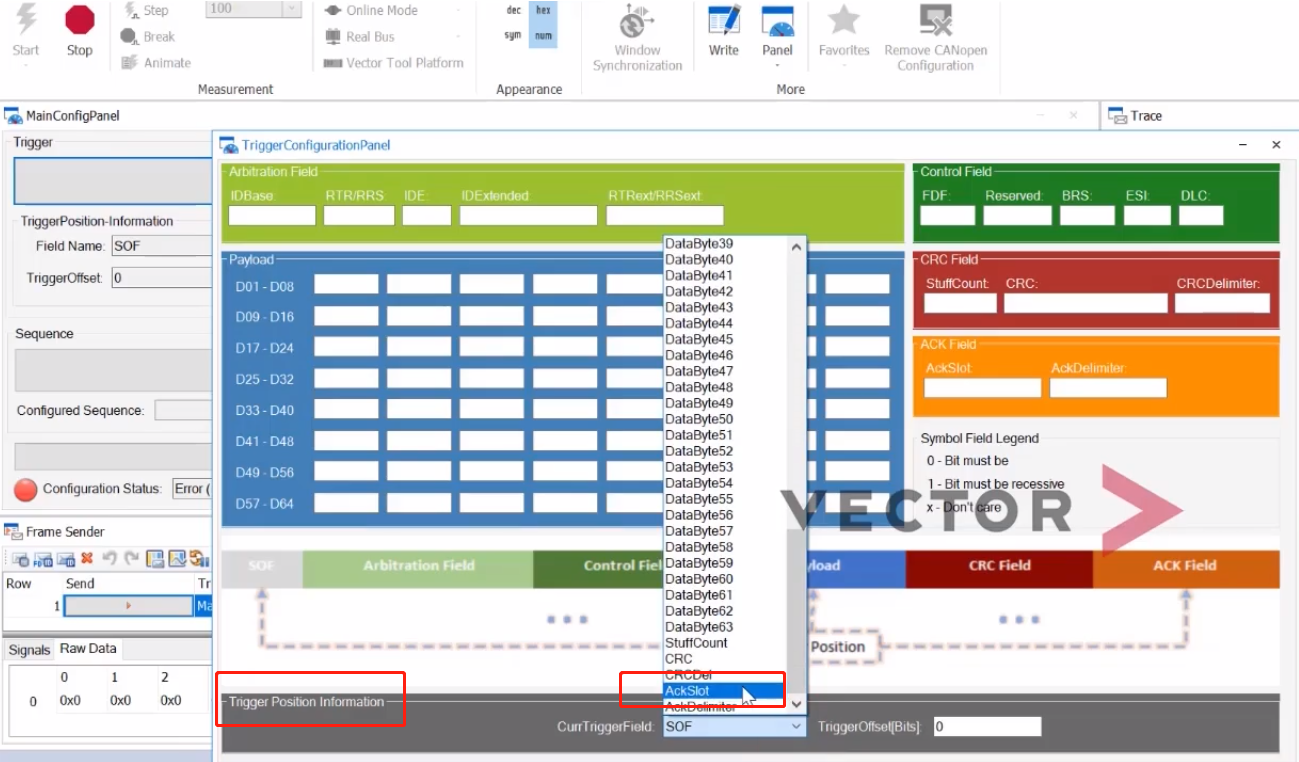

1.觸發條件配置

CurrentTriggerField選擇ACK Slot位(CK Delimiter位的前一位)

TriggerOffset為0。

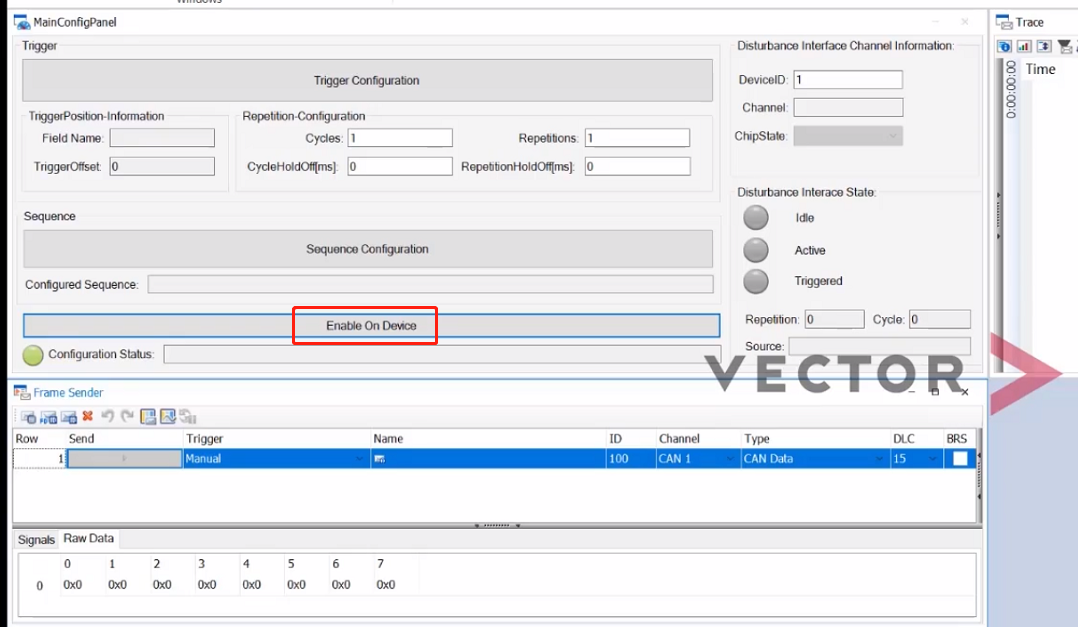

設置干擾的頻率:周期(Cycles)、周期間隔(CycleHoldOff)、重覆次數(Repetitions)、重覆間隔(RepetitionHoldOff)

2.干擾序列配置

干擾在觸發的下一位

選擇干擾的是數據場還是仲裁場(CANFD)

3.數字干擾激活

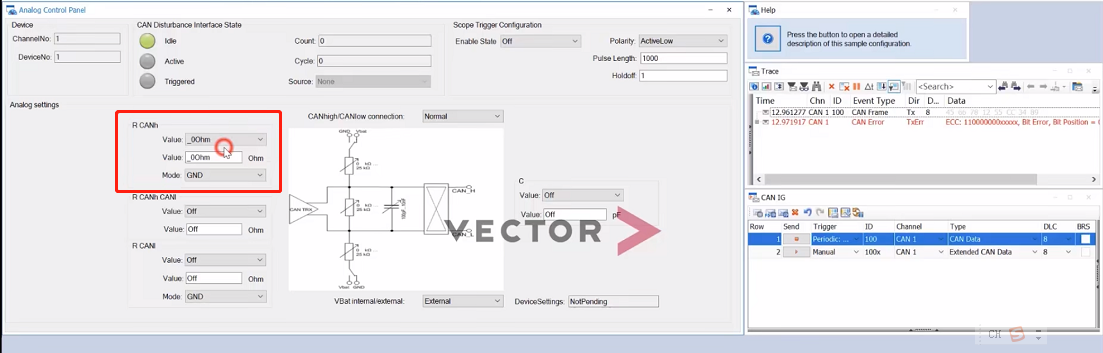

模擬干擾示例

1.CANH或CANL短接GND

2.CANH和CANL短接

3.CANH或CANL短接VBat(需要給VH6501外部供電)

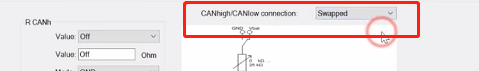

4.CANH和CANL反接(需要將DUT接到VH6501的ch1母頭)

5.CANH和CANL間電容/電阻值調整

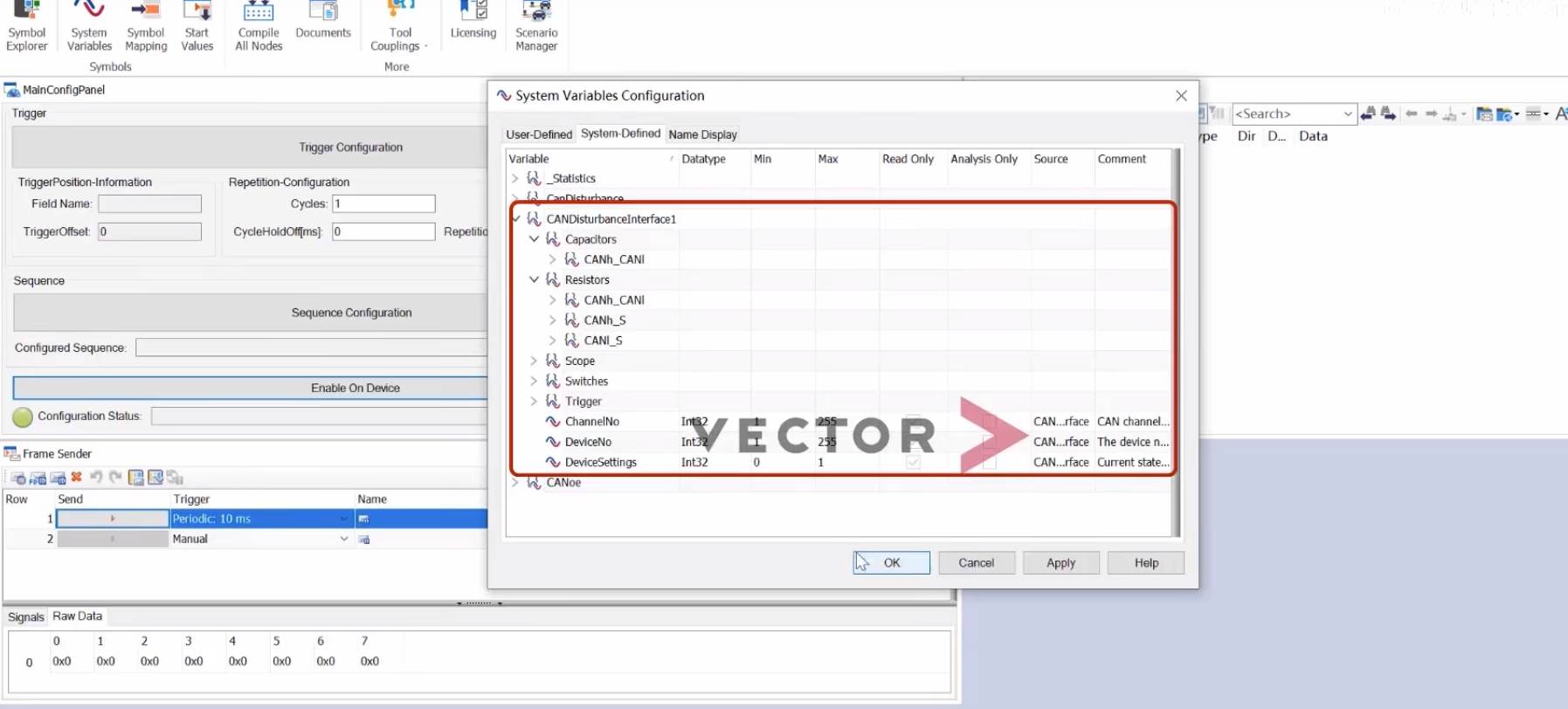

通過更新系統變數,來實現以上干擾。

CANH接地可以按照以下設置,其他干擾類似

R CANHh

Value:_0Ohm

Mode:GND

CANH和CANL反接,可以按照以下設置

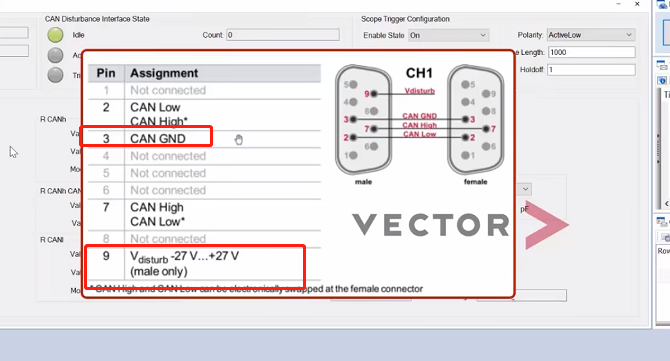

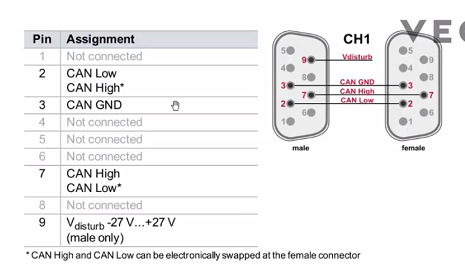

在CANH或CANL短接VBat時,需要將VH6501 CH1公頭的PIN9和PIN3連接外部供電電源,供電電源範圍:-27v到27v