SRAM是可在任何CMOS工藝中“免費獲得”的存儲器。自CMOS誕生以來,SRAM一直是任何新CMOS工藝的開發和生產製造的技術驅動力。利用最新的所謂的“深度學習領域專用域結構”(DSA),每個晶元上的SRAM數量已達到數百兆位。這導致了兩個具體挑戰。接下來由專註於代理銷售SRAM、SDRAM、MR ...

SRAM是可在任何CMOS工藝中“免費獲得”的存儲器。自CMOS誕生以來,SRAM一直是任何新CMOS工藝的開發和生產製造的技術驅動力。利用最新的所謂的“深度學習領域專用域結構”(DSA),每個晶元上的SRAM數量已達到數百兆位。這導致了兩個具體挑戰。接下來由專註於代理銷售SRAM、SDRAM、MRAM、Flash等存儲晶元的宇芯電子介紹關於SRAM兩大問題挑戰。

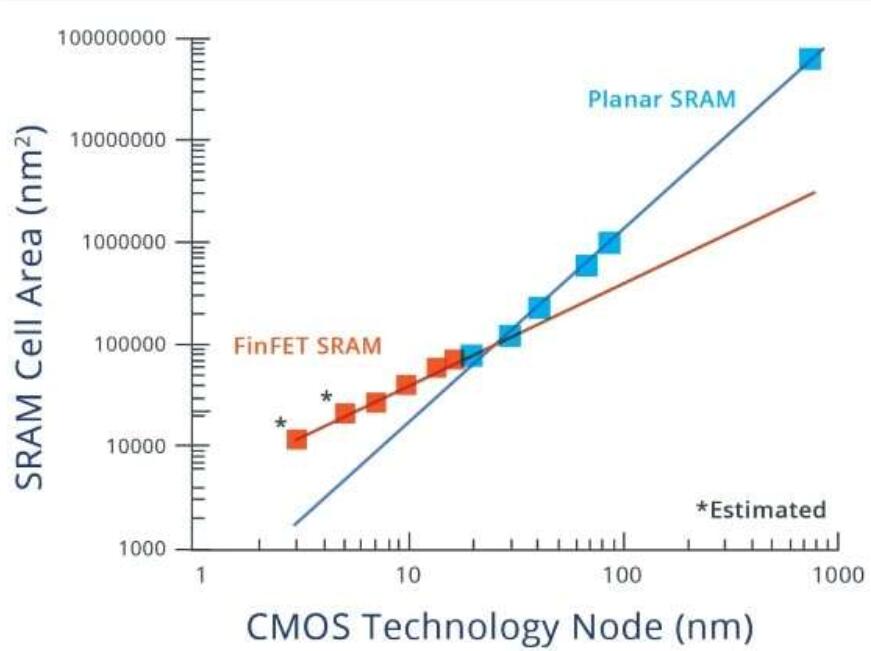

第一個挑戰是使用FinFET晶體管的最新CMOS技術使單元尺寸的效率越來越低。在圖1中可以看到這一點,其中SRAM單元大小是CMOS技術節點的函數。

圖1:過去30年中6晶體管SRAM單元尺寸的縮小趨勢。一旦FinFET晶體管成為CMOS的基礎,請註意減速。

平面到FinFET的過渡對SRAM單元的佈局效率有重大影響。使用FinFET逐漸縮小關鍵節距已導致SRAM單元尺寸的迅速減小。鑒於對更大的片上SRAM容量的需求不斷增長,這樣做的時機不會更糟。離SRAM將主導DSA處理器大小的局面並不遙遠。

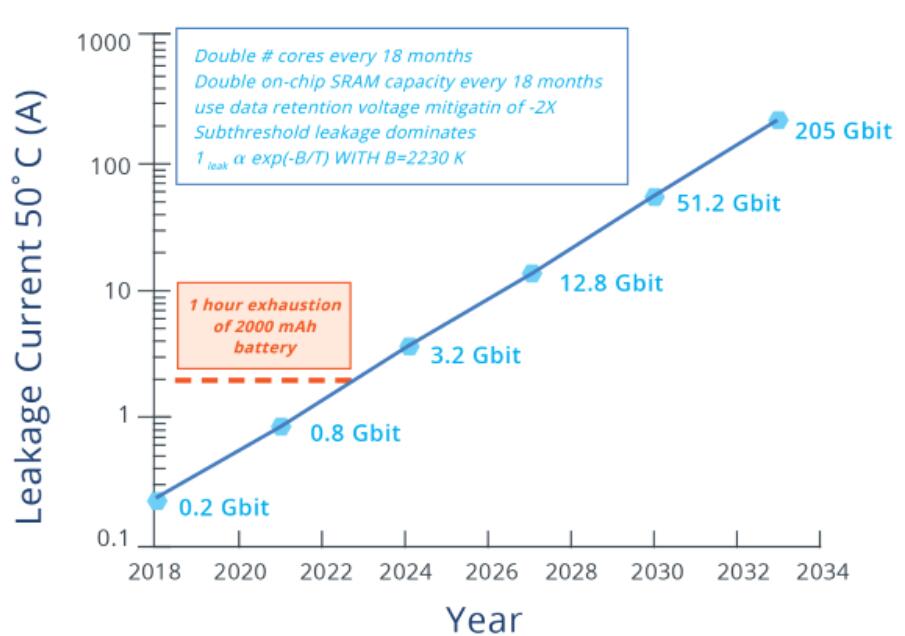

第二個挑戰是從正電源通過SRAM單元流到地面的泄漏電流。這主要是由於亞閾值晶體管泄漏是指數激活的,這意味著隨著晶元溫度的升高,泄漏急劇增加。由於它沒有做任何有用的工作,因此會浪費能源。儘管通常被稱為靜態功耗,但這種泄漏也會在SRAM處於活動使用狀態時發生,並形成能量浪費的下限。

已經採用了近20年的緩解技術來限制這種影響,最先進的技術是將SRAM電源電壓從其工作值降低到所謂的數據保持電壓(DRV)。最初此技術可將工作電源電壓下的漏電流降低5到10倍。隨著技術節點的發展,電源電壓不斷降低,工作電壓和DRV之間的凈空縮小了,從而導致使用該技術的漏電流降低了約2倍。

既然我們已經基本用盡了所有的泄漏緩解技術,那麼越來越大的SRAM容量將導致大量的浪費電流。如圖2所示,CPU晶元上的SRAM容量每18個月翻一番。

圖2:隨著片上SRAM容量的不斷增加,預計SRAM泄漏電流為50oC。結果是基於低於10nm CMOS的晶體管泄漏數據的模擬。

這兩個SRAM挑戰與不斷提高的片上高速緩存存儲速度和容量的需求密不可分,從而帶來了成本和能源浪費方面的真正挑戰。這種需求來自移動和數據中心應用程式。由於電池壽命的限制,對能源效率的最終要求在前者中是顯而易見的,但在後者中也變得至關重要。

由於深度學習而產生的DSA晶元應該可以優化數據中心的性能,成本和能源。作為其一部分,要求它們的晶元將數據“晃動”到正向傳播的數據中,該傳播已針對針對矩陣/矢量計算進行了優化的處理器進行。將結果數據與“目標”進行比較,然後將“錯誤數據”“拖拉”回記憶體以在下一個收斂周期中使用。除了通常需要每秒Tera浮點運算(TFLOPS)的處理器外,還需要越來越快的片上高速緩存來處理這種巨大的數據移動。

在許多此類DSA晶元並行運行的環境中,例如數據中心,此過程的低效率將導致數千安培從主電源流向地面。所有這些浪費的大量泄漏自然會導致巨大的浪費成本。