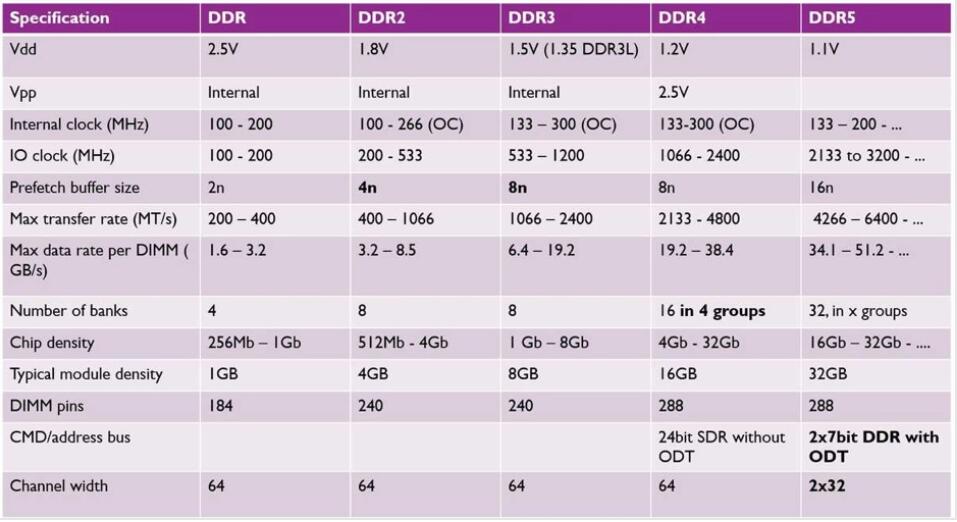

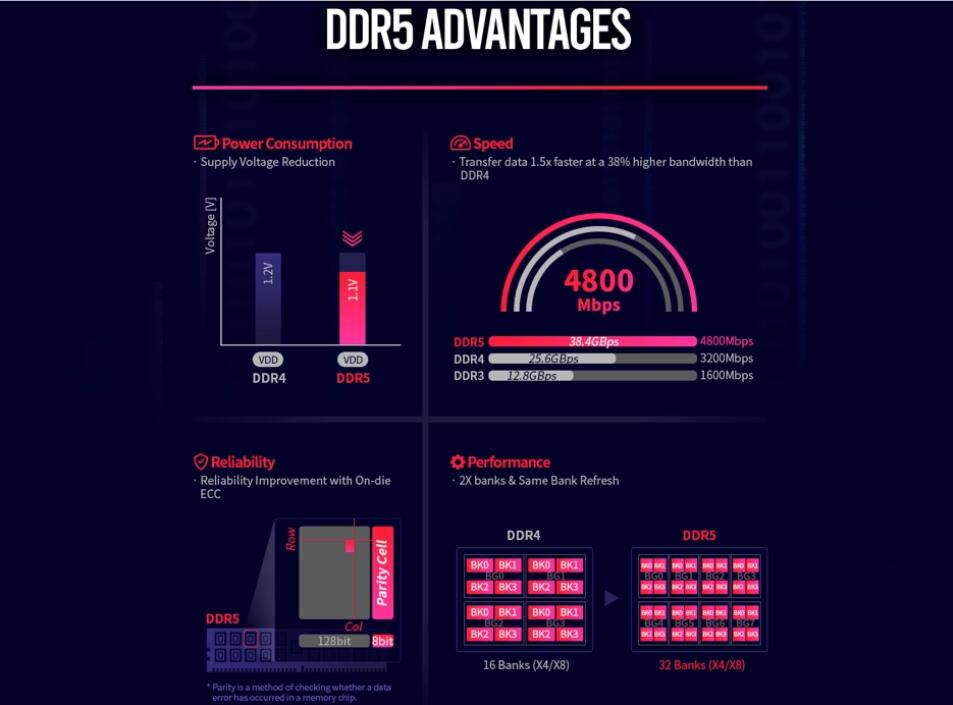

半導體工程組織JEDEC為動態隨機存取存儲器(DRAM)設定了標準,該組織上周發佈了最終的JESD79-5DDR5規範。新型存儲器是其每引腳數據傳輸速度的兩倍,其存儲設備的容量增加了四倍,降低了工作電壓,並引入了多種方法來提高瘦節點上DRAM的可靠性-並降低功耗。JEDEC說,DDR5 SDRAM將 ...

半導體工程組織JEDEC為動態隨機存取存儲器(DRAM)設定了標準,該組織上周發佈了最終的JESD79-5DDR5規範。新型存儲器是其每引腳數據傳輸速度的兩倍,其存儲設備的容量增加了四倍,降低了工作電壓,並引入了多種方法來提高瘦節點上DRAM的可靠性-並降低功耗。JEDEC說,DDR5 SDRAM將從明年開始用於即將推出的客戶端PC和伺服器。

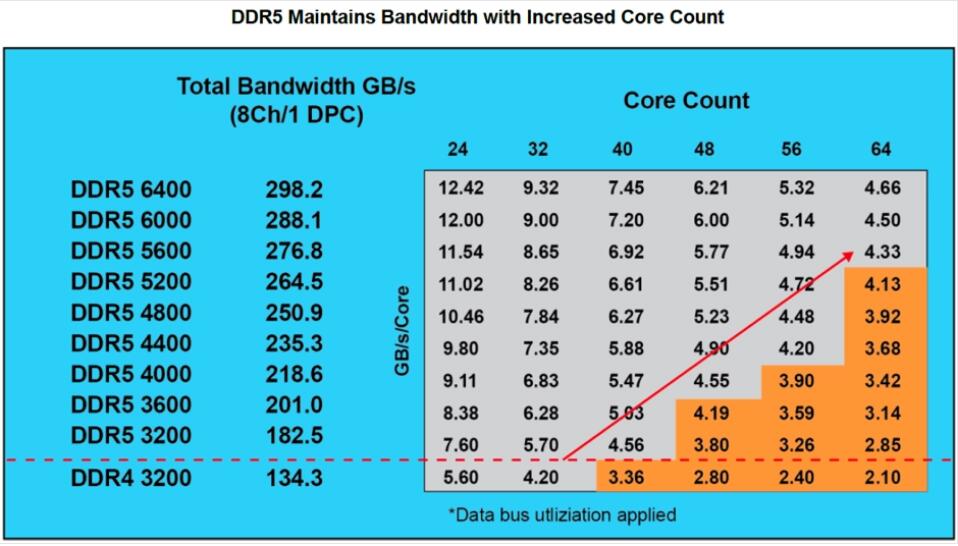

SDRAM的發展通常遵循與CPU發展相同的方向。如今微處理器致力於提高內核數,提高每個內核的性能以及提高電源效率,這對系統記憶體提出了要求。先進的內核需要足夠的記憶體帶寬,而此類內核的負載則需要高DRAM容量(和高帶寬),但是在記憶體控制器的功能,信號完整性以及功耗方面存在局限性。為此,DDR5通過同時向多個方向發展DRAM來滿足客戶和伺服器系統的需求。

資料來源:美光

JEDEC的JC-42記憶體委員會主席說:“通過在其設計中實現幾種新的性能,可靠性和省電模式,DDR5準備支持和啟用下一代技術。

DDR5帶來了無數的發展,並且由於新標準提供了所有可擴展性和改進的選擇,由於技術轉換通常較慢,因此新型記憶體的壽命可能比其前代產品長-這是一件好事適用於CPU和SoC設計人員。正式出版物表明開發已完成,所有參數均已設置,並且不添加任何新功能。

高性能計算所需要的記憶體必須能夠跟上當今處理器不斷增長的需求,隨著DDR5標準的發佈,AMD可以更好地設計其產品,以滿足我們的客戶和最終用戶的未來需求。

容量提高

儘管如今客戶端和伺服器機器在組件方面有很大不同,但它們有一個共同點:它們渴望獲得高密度DRAM。隨著伺服器CPU內部內核數量的增加,現代伺服器對記憶體容量的需求不斷增長,但是,如果不使用帶有緩衝區的複雜記憶體子系統(例如,LRDIMM或其他緩衝解決方案),今天在物理上不可能在每個記憶體通道上安裝兩個以上的模塊。PC的DRAM需求增長速度要慢得多,但是由於我們希望使用更時尚的筆記本電腦,因此PC製造商使用了更昂貴的LPDDR記憶體。巧合的是伺服器和客戶端的答案都是相同的:更高容量的通用DRAM設備。

CadenceIP集團表示DDR5主要是關於密度,使其特別適合企業,雲和大數據應用程式。

資料來源:IMEC

DDR5將以8GB和16GBDRAM開始,而今天的DDR4正是如此。但是該標準允許製造商設計具有24GB,32GB或64GB容量的設備。DDR4將每個設備的最大容量從8GB增加到16GB,而DDR5則從16GB一直增加到64GB,是原來的四倍。此外,DDR5最多可堆疊16個存儲設備(DDR4則為四個)。但是有一個局限性:該標準最多可堆疊16個DRAM,這些DRAM具有16GB,24GB或32GB的容量,但最多只能堆疊8個64GB的設備。

高位地址位是晶元ID還是高位地址位都有限制,因此對於64GB的設備,我們只能支持8-Hi堆棧。8-Hi64GB以及16-Hi32GBDRAM堆棧將使製造商能夠在未來數年內生產2TB伺服器級模塊,因此支持8個記憶體通道和每個通道兩個模塊的伺服器CPU可以配備64個TB5DDR5記憶體(今天為4TB)。

由於DDR5實際上在命令/地址中嵌入了等級信息(晶元ID),而不是像前幾代那樣使用單獨的信號,因此DDR5實現實際上可以支持多達32個等級(設備)的記憶體,因為我們可以擁有16個高3D堆棧記憶,模塊本質上是1或2級,然後模塊上的每個DRAM位置都可以支持16-Hi堆棧,因此網路為32。

由於製造上的挑戰,緊湊包裝的16-HiDDR5堆棧肯定不會在第一批DDR5晶元中提供。由於必要的額外製造工作,業界不太可能在DDR5中首次推出16-Hi堆棧。實際上,8-Hi堆棧可能會來得很晚。2-Hi和4-Hi堆棧的記憶體非常普遍,因此從一開始就意味著2、4和8級模塊將非常普遍。我們不再真正將它們稱為等級,而是指我們正在使用3D堆棧存儲器的事實。

資料來源:SK海力士

為了將每個設備的容量增加到64Gb,DDR5開發人員必須增加存儲庫的數量來解決這個問題。為此DDR5將存儲庫組的數量從16個增加到32個,而每個存儲庫組的存儲庫數量保持不變(四個存儲庫),這允許在任何給定時間打開更多頁面以提高頁面點擊率,僅可減輕更高的容量,但實際上可以提高系統性能,這是美光公司使用其16Gb DDR5器件測得的。