在常用感測器中,模數轉換器是其中至關重要的環節,模數轉換器的精度以及系統的成本直接影響到系統的實用性。因此。如何提高模數轉換器的精度和降低系統的成本是衡量系統是否具有實際應用價值的標準。 圖 1 ADC工作流程 一、ADC簡單介紹 ADC可分為SAR型、積分型、Σ-Δ型、摺疊型等方式。SAR ADC ...

在常用感測器中,模數轉換器是其中至關重要的環節,模數轉換器的精度以及系統的成本直接影響到系統的實用性。因此。如何提高模數轉換器的精度和降低系統的成本是衡量系統是否具有實際應用價值的標準。

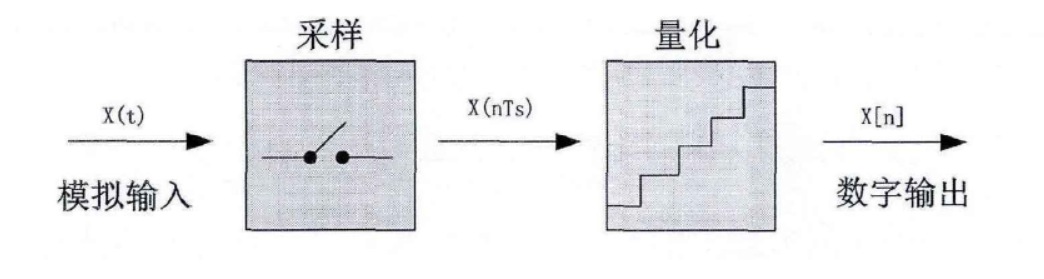

圖 1 ADC工作流程

一、ADC簡單介紹

ADC可分為SAR型、積分型、Σ-Δ型、摺疊型等方式。SAR ADC因其功耗低、精度高、面積小等特點而被用於超大規模IC和片上系統中。SAR ADC的精度是關鍵參數。SAR ADC有採樣、量化和編碼等三種功能。三種功能中,採樣最重要。採樣的精確性決定了ADC的轉換精度。逐次逼近型 ADC 中電路模塊主要包括:S/H 電路、電容陣列、比較器、逐次逼近控制邏輯、時鐘及偏置電路等,而 S/H 電路、電容陣列、比較器是高精度逐次逼近型 ADC 設計的關鍵。

首先由採祥保持電路採集並保持某點信號一段時間,在保持的這段時間里,對該點信號進行量化處理,以0或1數字編碼形式輸出,該串數字碼與不同權重的參考電壓相乘再相加,就是該點的電壓值。按照這種方式,每隔一定周期就可以量化連續的模擬信號某點的電壓值,採樣點越多,還原的模擬信號就會越精確。

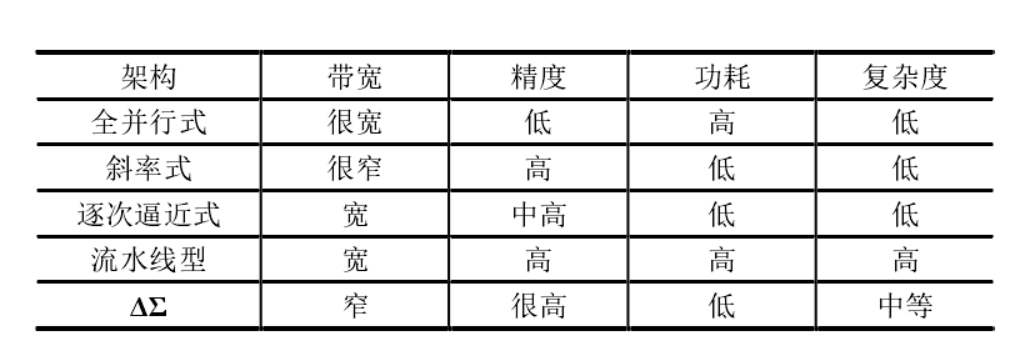

圖 2 不同ADC架構性能總結

ADC的精度是整個電路和系統精度至關重要的部分。ADC的精度和解析度是兩個不同的概念。精度指轉換後所得結果相對與實際值的準確度;解析度是指轉換器所能分辨的模擬信號的最小變化值。一般來講,解析度越高,轉換誤差越小;但影響精度的因素較多,解析度很高的ADC,可能並不一定具有很高的精度。

所謂嵌入式模數轉換器是指將模擬多路開關、採樣保持、A/D轉換、微控制器集成在一個晶元上。經常採用逐次比較型進行A/D轉換,模擬輸入信號一般為非負單極性。且輸入信號的電壓範圍為0~AVREF。

二、影響ADC精度參數

在驗證ADC性能的時候,可以通過相關參數衡量其性能優劣,這些參數大體分為兩大類,即靜態參數和動態參數。

1、ADC靜態特性參數

靜態特性與時間無關,它是指實際量化特性與理想量化特性之間存在的偏差,包括:積分非線性誤差(Integral Non-Linearity:INL)、微分非線性誤差(Differential Non-Linearity; DNL)、增益誤差(Gain error)、失調誤差(Offset error)、解析度(resolution)。

(1)增益誤差(Gain error)

ADC 模塊的輸入、輸出是線性關係。但實際上, ADC模塊是存在增益誤差和偏移誤差的, 其中增益誤差是實際曲線斜率和理想曲線斜率之間的偏差, 偏移誤差(或失調誤差)是0 V輸入時實際輸出值與理想輸出值(0 V)之間的偏差。

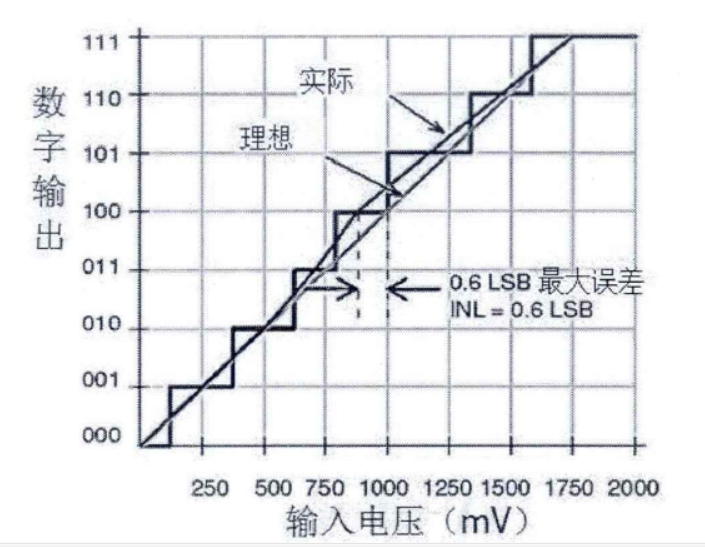

(2)積分非線性誤差(Integral Non-Linearity:INL)

模數轉換器的積分非線性誤差用來衡量實際特性曲線與理想特性曲線的最大差值,它表示了實際有限精度曲線相對與理想有限精度曲線的偏移量,可以用來估算諧波失真,通常以百分數或LSB為單位。

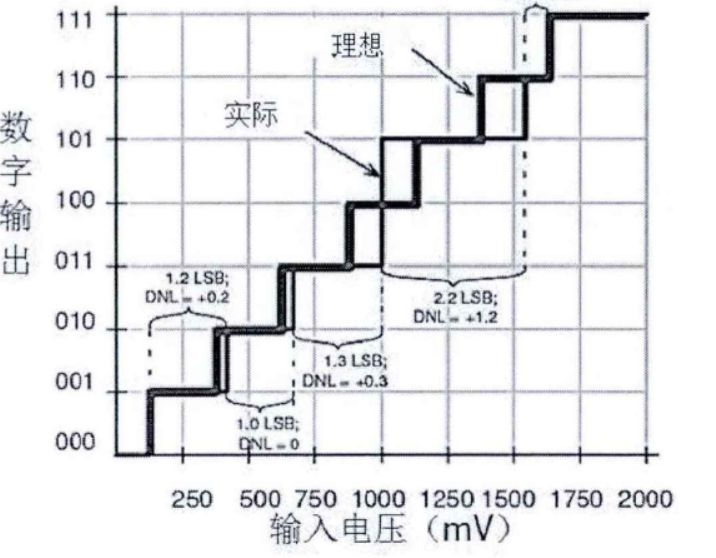

(3)微分非線性誤差(DNL)

微分非線性誤差為每個量化階梯上測量的相鄰編碼之間的距離,通常是由電路元器件的非理想因素引入的模擬増量偏移值,以百分比或LSB為單位。

2、ADC動態特性參數

ADC的動態特性參數通常與ADC的轉換速率和輸入信號頻率相關。主要包括:信噪比(SNR)、信噪失真比(SNDR)、無雜散動態範圍(SFDR)、總諧波失真(THD)、有效位數(ENOB)。

3、溫度濕度環境及電源電壓的波動引起的誤差、採樣電壓的波動

在實際應用中,由於環境溫度、濕度等參數的變化可能會引入一些誤差。電源電壓的不穩定也會帶來一定的誤差,採樣電壓的波動(可能是由於高頻信號疊加,或者其他隨機干擾信號),對整個系統的精度產生影響,電源電壓變化引起的轉換誤差在高精度要求場合不可忽略。

4、其他因素

模數轉換器(ADC)想要在實際應用中達到標稱的精度,僅僅依賴ADC模塊本身是不夠的,實際的測量精度還會受到一系列外在因素的影響,例如:

•ADC時間配置(包括採集時間、轉換時間、採樣時間、採樣時鐘抖動等等)

•電源性能(雜訊和內部阻抗)

•數據採集系統中數字和模擬部分的隔離情況

•內部阻抗與外部阻抗的匹配

•輸入/輸出開關切換的影響

•PCB佈局佈線

三、提高ADC精度方法

軟體演算法提高精度(常用的方法)

在運用具有內置模數轉換模塊的嵌入式單片機來進行模數轉換的過程中,為了提高解析度或對微弱信號採樣識別,目前比較常用的方法主要是採用過採樣技術來實現低於最小採樣解析度的微弱信號採樣。該技術是通過多次對輸入的採樣信號疊加白雜訊後,再模數轉換輸出,然後對輸出取平均值。 在採樣過程中,導致採樣電壓波動的因素有很多。可能是由於外界的隨機信號干擾引起。也可能是由於電路中產生的諧波信號引起的周期性干擾信號。用軟體濾波方法則可以有效減小此類誤差。常用濾波演算法如下:

算術平均濾波法

遞推平均濾波法(又稱滑動平均濾波法)

中值濾波法

一階滯後濾波法

加權平均濾波法

針對環境及電壓波動解決方案如下:

(1)採用高精度穩定電源供給,減少電源電壓變化誤差。

基準電壓是提供ADC轉換時的參考電壓,是保證轉換精度的基本條件。在要求較高精度時,基準電壓要考慮單獨用高精度穩定電源供給。此外,外加模擬電源和數字電源也要儘量採用穩定性高(電源電壓敏感度<0.002%)、受溫度變化小的電源。當然可以選擇溫度繫數比較好、精度比較高的電源模塊提供穩定的電壓。但是由於高精度的電源管理模塊價格往往不菲,會大大增加系統的成本。在本設計中,採用市場上面比較常見的LDO作為電源電壓。

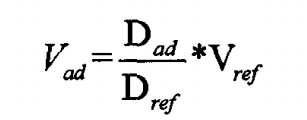

(2) 利用數學變換減小運算誤差,減小溫度漂移、濕度、環境等及電源電壓的波動引起的誤差。

(3)利用軟體濾波方法。

針對增益誤差和偏移誤差解決方案如下:

(1)最小二乘法和一元線性回歸(直線擬合問題) 用穩定信號源產生多個標準電壓, 通過輸入ADC通道記錄採樣值。然後利用最小二乘和一元線性回歸思想處理數據, 求出的擬合最佳曲線, 使得各個坐標點到該最佳曲線的距離的平方和(殘差平方和)最小。

(2)在用電腦對模擬信號採集情況下,將編碼器零電平信號讀入電腦記憶體中相應的單元,然後才開始採樣程式的執行。在採樣程式中,將採集到的數據與零電平相減,從而基本上消除偏移溫漂誤差。

ADC時間配置

在器件中,採樣時間等於一個ADC時鐘周期。該ADC模塊的採樣時間不僅依賴於ADC時鐘,還與其他配置有關,如NXP晶元中可以通過修改ADCx_CFG1寄存器中的ADLSMP位和ADCx_CFG2寄存器中的ADLSTS位來對採樣時間進行配置。因此,總的轉換時間並不會隨採樣時間增加而顯著增加,這種特性在高輸入阻抗的情況下尤其有用。

ADC硬體處理

為了使ADC達到最佳的性能,我們需要正確地設計和配置整個系統。在硬體方面,可進行以下配置,例如: • 在晶元電源引腳間放置0.1uF的電容,電容應儘可能地貼近晶元封裝(每對電源引腳間放置一個電容)

•在晶元電源引腳間放置約為100uF的電容

•PCB走線長度應該儘量短 •在實際應用設計中應充分考慮PCB走線上寄生參數的影響

•必須小心處理模擬電源以及參考引腳,使它們的雜訊幅度最小 •針對數字部分和模擬部分使用不同的供電電源和地平面

•如果數字部分和模擬部分連接到了相同的供電電源,則應該在數字部分和模擬部分之間使用一個小的電感或磁珠進行連接

•使用地平面將有雜訊的數字元件與模擬元件隔離開來,走線時用模擬地將模擬信號包圍起來

外部RC元件的取值會從本質上影響ADC轉換的精度,為了獲得最佳的ADC性能,我們需要小心對待並設計外部RC元件,在選取採樣時間時也必須參考採樣電容充電的時間常數