本小節我們來做一個好玩的事情,就是計數器,還記得在做LED自加實驗時我們就曾經提到過關於計數器的相關議題,那麼這節我們就來討論討論。 探討一下如下的問題:請用verilog記八個數的寫法,分析這個可以更好的理解觸發器的工作原理。1. reg [3:0]cnt; always@(pose...

本小節我們來做一個好玩的事情,就是計數器,還記得在做LED自加實驗時我們就曾經提到過關於計數器的相關議題,那麼這節我們就來討論討論。

探討一下如下的問題:請用verilog記八個數的寫法,分析這個可以更好的理解觸發器的工作原理。

1. reg [3:0]cnt; always@(posedge clk or negedge rst_n) begin if(!rst_n) cnt <= 4'd0; else if (cnt < 4'd8) cnt <= cnt + 1'b1; else cnt <= 4'd0; end 2. reg [3:0]cnt; always@(posedge clk or negedge rst_n) begin if(!rst_n) cnt <= 4'd0; else if (cnt < 4'd8 - 1) cnt <= cnt + 1'b1; else cnt <= 4'd0; end 3. reg [3:0]cnt; always@(posedge clk or negedge rst_n) begin if(!rst_n) cnt <= 4'd1; else if (cnt < 4'd8 ) cnt <= cnt + 1'b1; else cnt <= 4'd1; end 4. reg [3:0]cnt; always@(posedge clk or negedge rst_n) begin if(!rst_n) cnt <= 4'd1; else if (cnt < 4'd7 ) cnt <= cnt + 1'b1; else cnt <= 4'd1; end

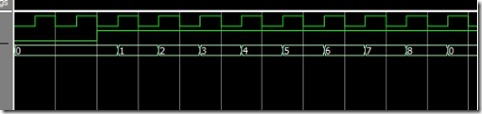

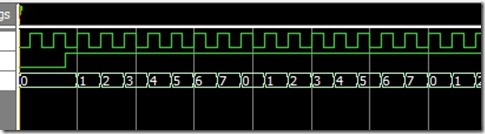

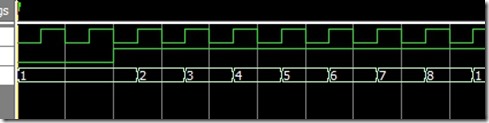

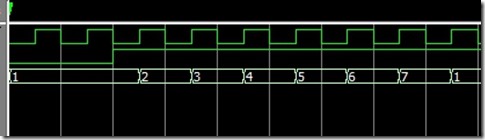

對應的模擬結果為:

1.計數為9個。

2.計數為8個

3.計數為8個

4.計數為7個

在else if語句中的判斷條件為 cnt < 4’d7或者cnt <4’d8,以cnt < 4’d7為例,當cnt =4’d7顯然是不滿足條件的,所以利用跳出自加程式,執行else語句,但是cnt = 4’d7也會被列印輸出,這是由於時序電路在時鐘的節奏下一拍一拍的輸出,當時鐘上升沿來臨時,這時cnt = 4’d7,然後等待下一個時鐘沿到來把cnt = 4’d7打入到鎖存器裡面去,然後再在下一個時鐘沿來臨將cnt = 4’d0打入。以此類推。

針對上述的四種情況,大家在寫一些利用計數器進行分頻的程式時,若是精確控時,請註意cnt小於的常數是多少,這一點務必搞清楚。