回到目錄 BJT晶體管可以實現邏輯門,事實上,在場效應管被髮明用於集成電路以前,各種邏輯門晶元中的電路就是用BJT晶體管來實現的。最早人們使用二極體與BJT組合來實現邏輯門,這個稱為二極體-晶體管邏輯(Diode-Transistor Logic),簡稱DTL;後來改進為全部用BJT晶體管來實現邏輯 ...

BJT晶體管可以實現邏輯門,事實上,在場效應管被髮明用於集成電路以前,各種邏輯門晶元中的電路就是用BJT晶體管來實現的。最早人們使用二極體與BJT組合來實現邏輯門,這個稱為二極體-晶體管邏輯(Diode-Transistor Logic),簡稱DTL;後來改進為全部用BJT晶體管來實現邏輯門,這個稱為晶體管-晶體管邏輯(Transistor-Transistor Logic),簡稱TTL。早期廣為人知的TTL電平,就是基於這種用BJT晶體管實現的邏輯門。TTL的優點是響應速度比較快,缺點是功耗較大,所以後來基本被功耗更低的場效應管取代。

我們這裡僅介紹幾個最簡單的邏輯門的實現:反相器、或非門、與非門,主要是用來說明概念。除非你是專門設計邏輯門晶元的,否則一般平時也不太可能用分立元件去搭建邏輯門,還有就是在電路修補中萬不得已時應急用一下。

在前面幾小節的放大電路中,BJT都工作於放大區。而在用BJT實現邏輯門時,卻要使用飽和區和截止區,而不能使用放大區,這個是邏輯電路和放大電路的在使用BJT時的根本區別。

1. 反相器

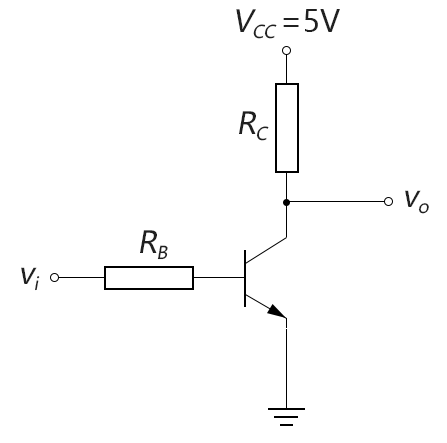

反相器的功能很簡單,就是將輸入的電平反向輸出:輸入高電平-輸出低電平、輸入低電平-輸出高電平。下麵是反相器的實現電路:

圖3-9.01

在作邏輯分析時,我們一般做如下近似:將VBE的導通值視為0.7V,將典型值為0.1V~0.3V的飽和電壓VCEsat近似視為0.2V。

下麵是反相器電路工作原理:

• 當vi輸入為0V時,BJT截止,vo輸出電平即為5V。

• 當vo輸入為5V時,BJT的CE端導通,產生電流IC,若此時BJT處於飽和區,VCE近似可視為飽和電壓0.2V,此時輸出電平vo即為0.2V。

這個電路的關鍵點在於如何選取合適的RB與RC值以確保BJT在導通時確實工作於飽和區。一般可以先根據外部負載條件定出一個符合輸出阻抗要求的RC,然後再根據飽和要求,用公式原理推算出能使BJT進入臨界飽和的大致RB值,再加點餘量。最後驗證在高電平輸入條件下,BJT在此RB配置下是否確實工作於飽和區。具體方法可參看下麵的案例:

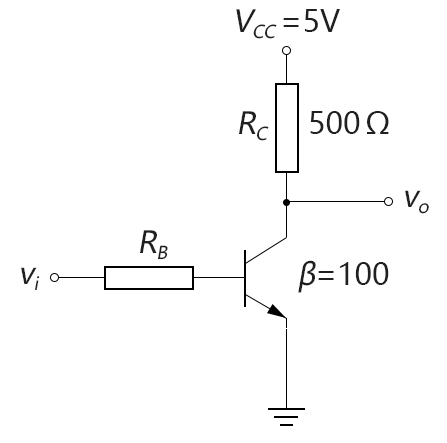

案例3-9-1:在下圖的反相器中,已知β=100,根據外部負載匹配,要求RC為500Ω,請選取合適的RB值使反相器能正常工作。

圖3-09.a1

解:先計算出,在這個RC條件下,當BJT處於臨界飽和時的ICsat值:

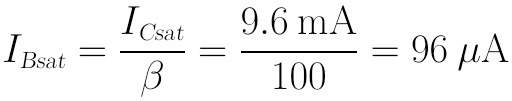

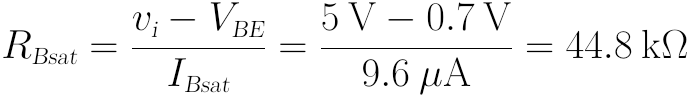

然後計算臨界飽和時的IBsat值(當處於臨界飽和時,β仍視為100):

使此IBsat成立的RBsat為:

為使BJT進入更深度的飽和,我們選取RB為比RBsat更小的值,假定選取為20kΩ。

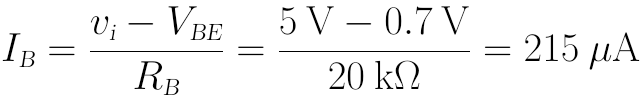

驗證:當RB為20kΩ時,IB為:

此時電流放大倍數為:

可知,在此RB值下,BJT導通時確實處於飽和區,原假設正確。

2. 或非門

或非門BJT實現電路和輸入輸出真值表如下圖所示(其中1表示高電平,0表示低電平):

圖3-9.02

• 當vi1和vi2輸入都為0V時,晶體管Q1和Q2都截止,vo輸出電平為5V。

• 當vi1輸入為5V、vi2輸入為0V時,晶體管Q1導通、Q2截止,由於Q1工作於飽和區,VCE1=VCEsat≈0.2V,故vo輸出電平為0.2V。

• 同樣的,當vi2輸入為5V時、vi1輸入為0V時,晶體管Q2導通、Q1截止,VCE2=VCEsat≈0.2V,故vo輸出電平為0.2V。

• 當vi1和vi2都輸入0V時,晶體管Q1和Q2都導通,VCE1=VCE2=VCEsat≈0.2V,故vo輸出電平為0.2V。

關於如何配置RB1、RB2、RC的值使BJT晶體管工作於飽和區,這個和前面反相器的計算方法是類似的,可參看上面的案例3-9-1。

3. 與非門

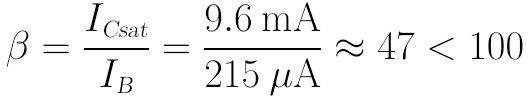

與非門的實現需要二極體的配合,其實現電路和真值表如下圖所示:

圖3-9.03

• 當vi1和vi2輸入中有任一個為0V時,輸入二極體Di1或Di2就會導通,此時v1點的電壓即為二極體的導通閾值電壓0.7V。這個電壓無法使右邊的D1和Q1都導通,因為若要使D1和Q1的發射結都導通,vB點的電壓起碼需要0.7V,而v1點的電壓需要0.7+0.7=1.4V。而在v1只有0.7V的情況下,右邊的D1和Q1的發射結每個只能分到0.35V左右的電壓,故D1和Q1都截止,輸出vo保持5V的高電平。

• 當vi1和vi2輸入全都為5V時,輸入二極體Di1和Di2全都截止,此時VCC會使R1、D1和Q1形成通路,vB點的電壓為0.7V,v1點的電壓為1.4V。由於Q1導通時工作於飽和狀態,故輸出vo為VCEsat約等於0.2V。

至於如何配置R1、RB、RC,原理和前面是一樣的:根據輸出阻抗匹配先定RC,然後計算為使Q1進入飽和區的R1,具體方法可參看前面的案例3-9-1。

順便提一下,RB稱作下拉電阻,其主要作用是當Q1從飽和狀態切換到截止狀態時,使基區過剩的少數載流子有個渠道流掉,以減少切換開關時間。這個稍微瞭解一下即可,一般選一個大約的幾千歐的阻值就差不多了,在要求不高的場合下,即使不用RB也問題不大。

4. 關於TTL

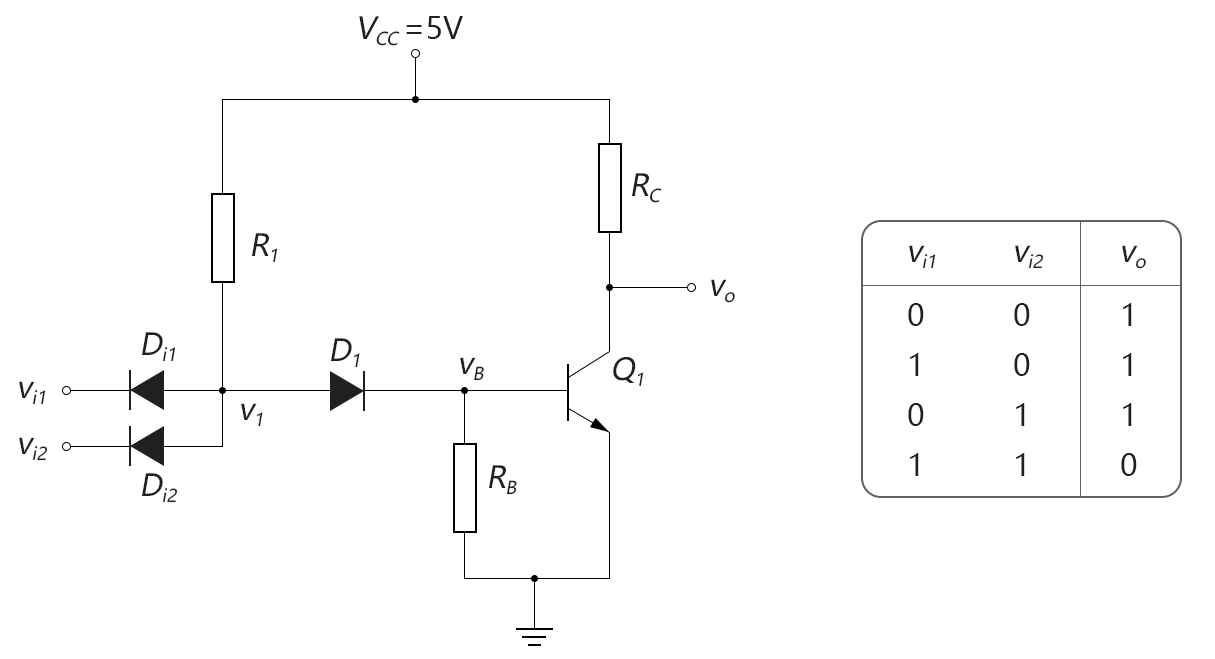

在上面電路中,我們用DTL(二極體-晶體管邏輯)實現了與非門。如果你想知道傳說中的TTL(晶體管-晶體管邏輯)到底是什麼樣的,那麼本小節可以稍稍滿足一下你的好奇心。

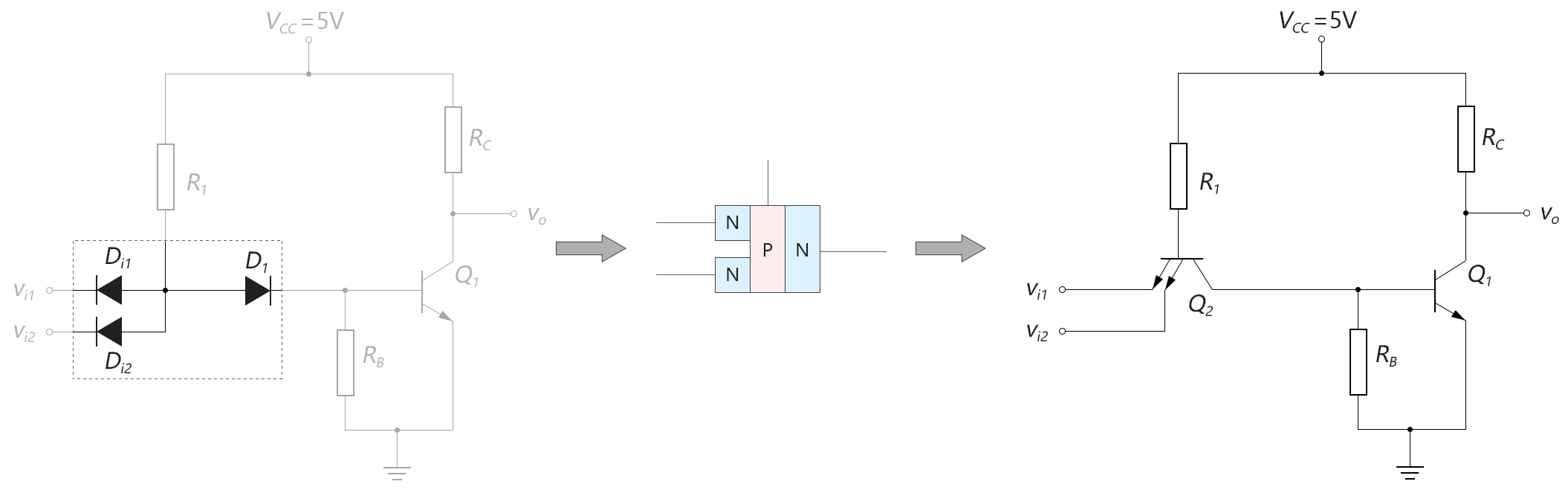

我們仍以上面的與非門為例,假設先去掉Di2,那麼,在圖中兩個背靠背的二極體Di1和D1,其實可以看成是一個NPN型三極體,如下圖所示:

圖3-9.04

我們前面說過,在分立元器件的BJT晶體管中,C極和E極的摻雜濃度是不對稱的,所以分立元器件中不能像上圖這樣等效,但是在製作集成電路晶元時,是可以在片上做成像上面右圖那樣的對稱管的。

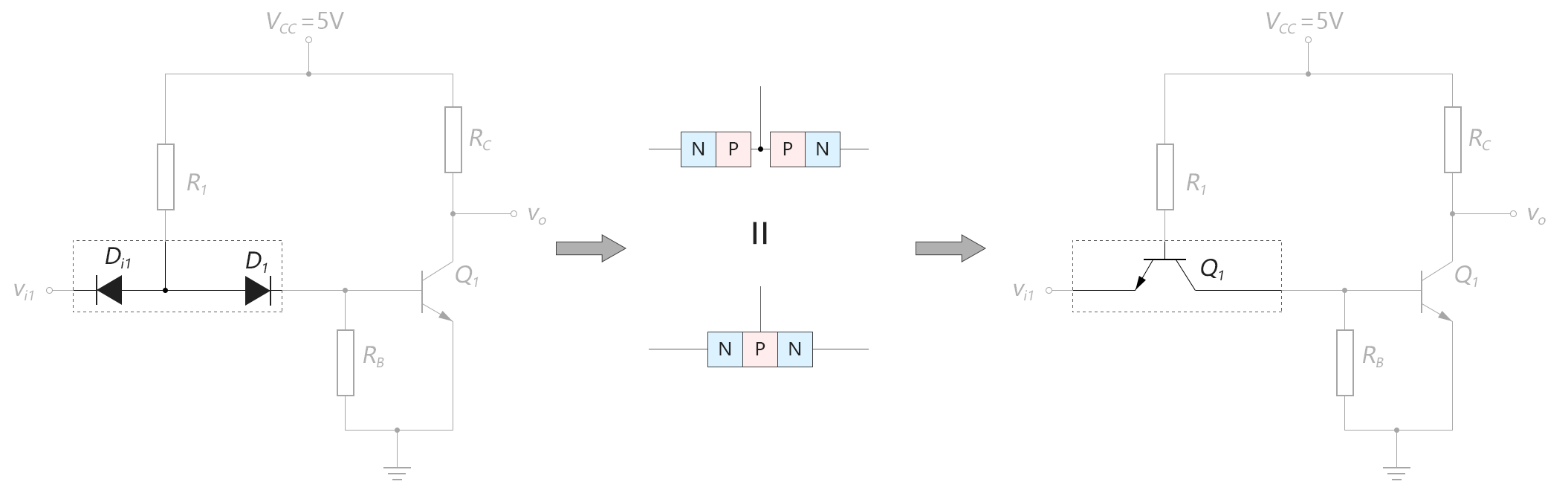

而且,在集成電路製作時還可以加入多個發射極,如下圖所示:

圖3-9.05

如此,就實現了一個二輸入與非門的TTL電路。如果要實現n個輸入的與非門,還可以加入n多個發射極。當然,這種多發射極的BJT晶體管只能在集成電路晶元中實現,分立元器件的話是沒有這種器件的。

( end of 3-9)