SDRAM基本信息 儲存能力計算 4X16X4=256(Mbit),註意不是MByte SDRAM控制 sdram包含兩個部分:sdram_ctrl、fifo_ctrl。 sdram_ctrl:其頂層為SDRAM的控制模塊內部實例化了5個模塊,有初始化、自刷新、寫和讀模塊,還有一個仲裁模塊對這四個不 ...

SDRAM基本信息

儲存能力計算

- 4X16X4=256(Mbit),註意不是MByte

SDRAM控制

sdram包含兩個部分:sdram_ctrl、fifo_ctrl。

- sdram_ctrl:其頂層為SDRAM的控制模塊內部實例化了5個模塊,有初始化、自刷新、寫和讀模塊,還有一個仲裁模塊對這四個不同操作進行分配;

- fifo_ctrl:其頂層為SDRAM的數據輸入輸出,內部實例化了兩個用於連接SDRAM輸入和輸出端的FIFO,以及控製程序

sdram_ctrl模塊內部例化了四個模塊

初始化模塊sdram_init

-

SDRAM在上電後首先需要執行初始化操作,才可執行其他操作。

-

配置寄存器模式

-

潛伏期為三個周期

-

突髮長度為頁突發

-

突發類型為順序類型

-

寫模式為頁突發寫模式

-

信號操作:

- 正常載入時鐘信號:設置CKE時鐘使能為高電平CKE = 1

- 等待Vdd和CLK信號穩定:等待T= 200us

- 進行預充電操作,對所有L-Bank進行預充電:cmd = PRECHARGE,A10 = 1

- 等待預充電操作:cmd = NOP,TRP =20ns

- 自動刷新命令:cmd = AUTO REFRESH

- 等待自動刷新:cmd = NOP,TRFC = 70ns

- 重覆多次自動刷新操作:重覆8次

- 配置模式寄存器:cmd = LOAD MODE REGISTER,address= ,A10 = ,bank = 0

- 等待配置模式寄存器完成,TMRD = 30ns

-

總體採用狀態機來設計,分為以下幾個狀態:

- 初始化

- 預充電

- 預充電等待

- 自動刷新

- 自動刷新等待

- 配置模式寄存器

- 配置模式寄存器等待

- 初始化完成

-

為了防止亞穩態的產生,狀態機編碼均使用格雷碼

-

跳轉條件使用計數器進行計數完成判斷

- cnt_clk,等待狀態的計數器

- cnt_clk_rst,負責等待計數器的清零操作

-

另外為了跳轉操作代碼簡潔,聲明組合邏輯的信號完成各個狀態的跳轉

- trp_end

- trc_end

- tmrd_end

-

由於自動刷新信號需要重覆進行,因此使用計數器完成自動刷新操作計數

- cnt_init_aref,計數自動刷新操作的重覆個數

-

最終按照各個狀態完成輸出信號的幅值,註意使用的為時序邏輯,因此輸出相比狀態跳轉延遲一拍

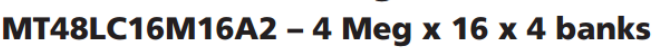

自動刷新模塊sdram_a_ref

- SDRAM刷新有兩種操作方式:

- 自刷新:用於休眠模式可以低功耗的保存數據

- 操作:CKR信號為低電平時,寫入刷新指令,進入自刷新模式,當CKE信號拉高時,退出自刷新模式;

- 自動刷新模式:由於SDRAM動態特性,使用電容來保存數據,因此需要不斷對電容進行充放電,以此保證數據不丟失。本文主要討論自動刷新。

- 自刷新:用於休眠模式可以低功耗的保存數據

- 自動刷新操作需要不斷的迴圈操作,是一個周期操作,至少需要每64ms完成一次。

- 自動刷新時間計算

- 存儲體中電容的數據有效保存期上限是 64ms那麼使用的SDRAM的地址位寬為13位,共有2^13=8192行。

- 那麼每行刷新的時間為:64ms/8192=64*1000000ns/8192=7812.5ns。

- SDRAM的時鐘為100MHz,周期為10ns,那麼計數器最大值為:7812.5/10=781.25個。

- 但是由於自動刷新操作和寫讀請求會產生衝突,會出現不會立即刷新的情況,因此需要保留一段時間,那麼設置計數器最大值為750個,要求在7500ns中完成其中一行的刷新。

- 信號操作

- 預充電操作:cmd = PRECHARGE、A10 = 1、bank = 2'b11

- 預充電等待:cmd = NOP,TRP = 20ns

- 自動刷新:cmd = PRECHARGE

- 自動刷新等待:cmd = NOP,TRFC = 70ns

- 自動刷新重覆兩次

- 初始化模塊為所有信號的首位,因此需要初始化信號拉高後在開始執行

- init_end = 1時,模塊開始正常工作

- 由於是一個周期信號,那麼需要一個計數器進行周期計數,並以此信號完成狀態機的啟動。

- cnt_ref作為計數器,最大值經計算為750-1,並且達到最大值後清零繼續計數

- 其餘信號需要在狀態機跳轉下進行操作:

- 初始

- 預充電

- 預充電等待

- 自動刷新

- 自動刷新等待

- 自動刷新結束

- 另外自動刷新需要和仲裁模塊進行握手,當仲裁模塊同意進行刷新操作時,才可進行該操作

- 當內部計數器cnt_ref達到最大值時,此時需要自動刷新,拉高自動刷洗請求信號aref_req = 1,仲裁模塊接受該信號,進行判斷若同意則拉高自動刷新使能信號,aref_en = 1。

- 當自動刷新完成,拉高自動刷新結束信號,aref_end= 1,仲裁模塊接受該信號,拉低自動刷新使能信號,aref_en = 0;

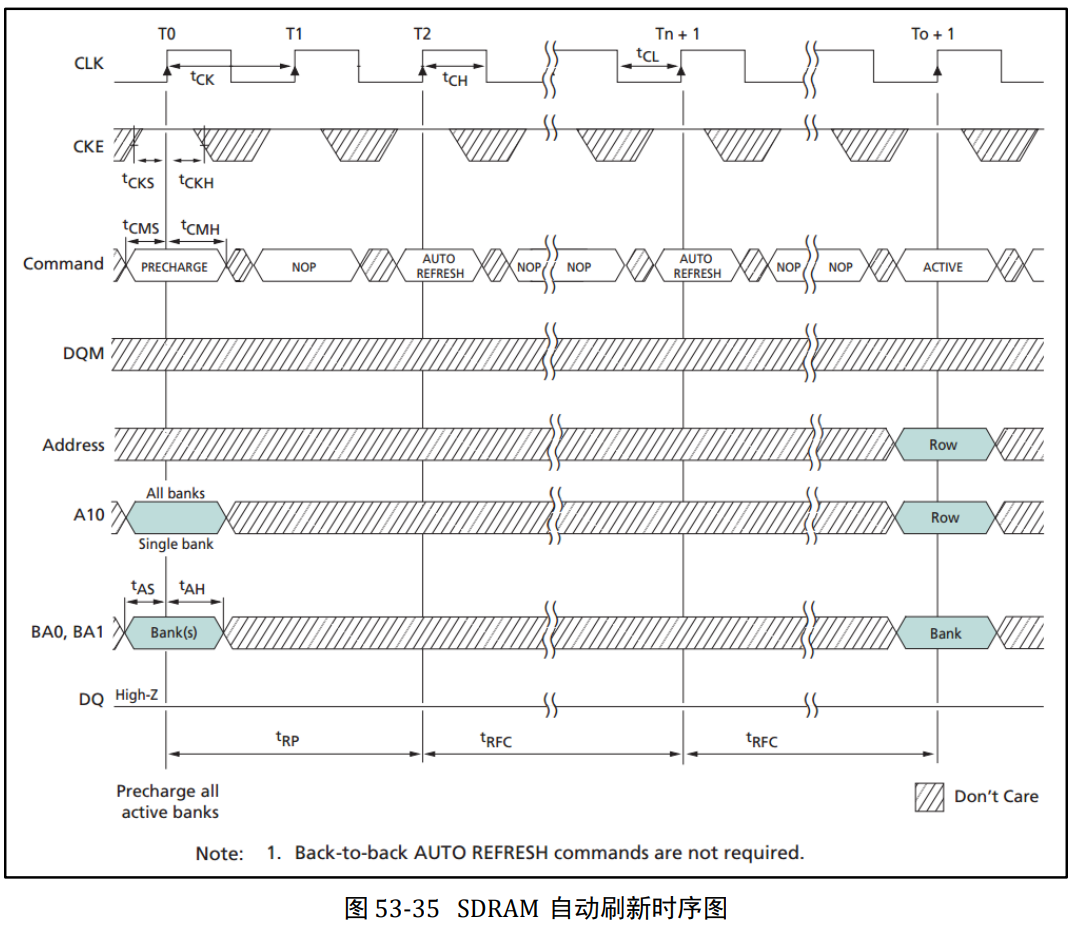

寫操作模塊sdram_write

- 本模塊使用的寫操作模式為:不自動進行預充電的頁突發寫模式

- 信號操作

- 激活L-Bank特定行:

- cmd = ACTIVE

- address = 特定寫入行地址

- bank = 特定寫入bank地址

- 等待激活

- cmd = NOP

- 寫數據命令

- cmd = WRITE

- address = 特定寫入列地址

- DQ = 寫入第一個數據

- 寫入數據中

- cmd = NOP

- DQ = 開始寫入第二個數據,每隔一個周期寫入一個數據

- 突發終止命令

- cmd = BURST TERM

- DQ = 不寫入數據

- 預充電命令

- cmd = PRECHARGE

- A10 = 1

- bank = 2'b11

- 預充電等待

- cmd = NOP

- TRP = 20ns

- 激活L-Bank特定行:

- 當初始化模塊完成初始化後才可以SDRAM才可以正常操作

- init_end = 1,此時寫模塊才可以正常開始工作

- sdram模塊的寫操作是由SDRAM上端的fifo模塊發起請求,經過sdram仲裁器同意後開始執行寫操作的

- SDRAM仲裁器判斷可以寫入時拉高,wr_en = 1

- 當寫數據操作執行完畢後狀態機跳轉至寫結束狀態時,通過組合邏輯賦值將寫結束信號拉高

- wr_end = 1

- 另外當FIFO請求向SDRAM寫入數據時,SDRAM並不能直接開始寫入,因此當真正開始寫入數據時需要一個提前一拍的響應信號告知fifo可以輸出數據

- wr_ack = 1

- 相比於寫數據的同步信號需要提前一拍,作為FIFO的讀出數據的讀請求信號

- 其餘信號在狀態機下完成

- 初始狀態

- 激活命令

- 激活等待

- 寫命令

- 寫等待

- 預充電

- 預充電等待

- 寫結束

- 寫入數據的信息由外部信號傳入,具體為輸入端的FIFO傳入

- [23:0] wr_addr:寫入數據的地址,可以分割為:2bit bank地址、13bit 行地址、9bit 列地址

- [15:0] wr_data,寫入數據

- [9:0] wr_burst_len,寫入數據個數

- 除了常規控制信號輸出外還有一個,控制SDRAM數據匯流排輸出使能信號,該信號和真正寫入sdram的數據同步。

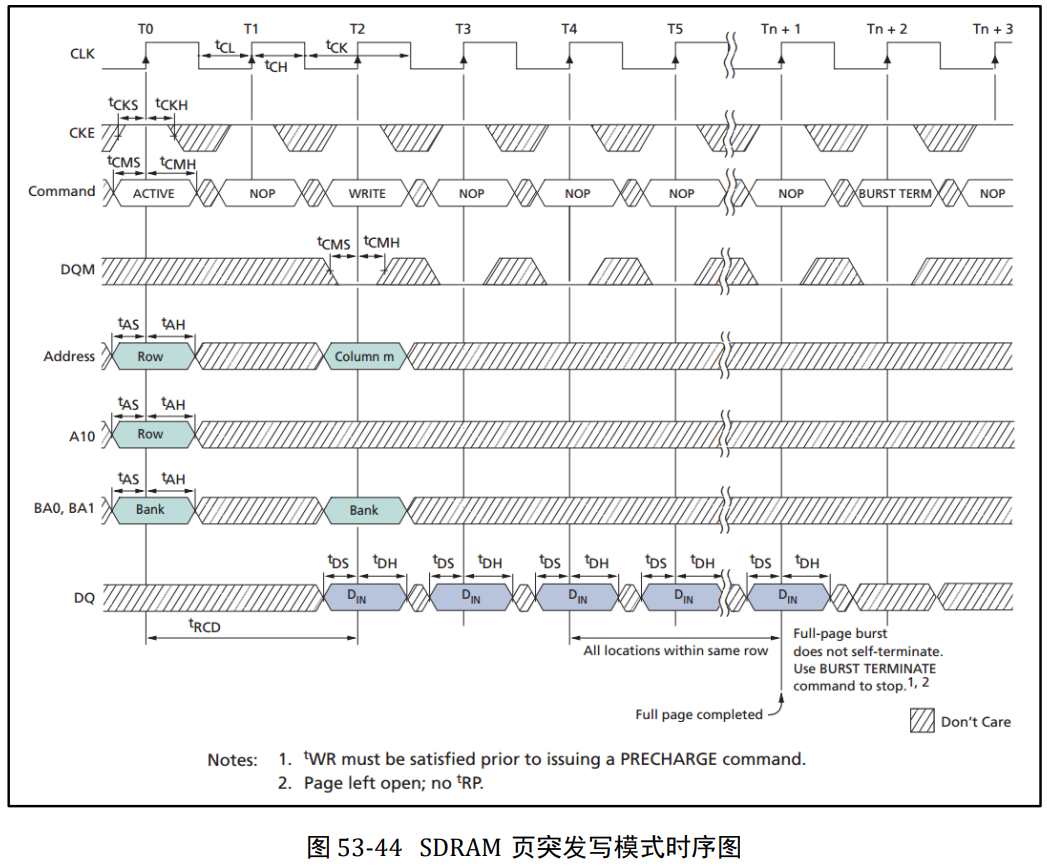

讀操作模塊 sdram_read

- SDRAM數據讀方式為:不帶自動預充電的頁突發讀模式

- 信號操作

- 激活L-Bank的特定行

- cmd = ACTIVe

- address = Row

- bank = 2‘b11

- 等待激活

- CMD = NOP

- TRCD =

- 讀命令

- CMD = READ

- address = column

- 讀出數據

- cmd = NOP

- 潛伏期設置為3,因此在寫入讀命令後的間隔3個周期,會有讀數據的輸出

- 突發終止

- cmd = BURST TERM

- cmd = BURST TERM

- 激活L-Bank的特定行

- 讀數據操作需要在初始化操作完成後進行

- 當init_end = 1 時,sdram_read進入正常工作模式

- sdram讀數據操作是由外部信號發起的,具體而言是SDRAM下端FIFO發出的讀請求信號,並且該信號需要經過仲裁器判斷後生效,仲裁器拉高讀使能信號

- rd_en = 1,讀模塊開始進行讀操作

- 當sdram_read讀操作完成後,狀態機進入結束狀態,使用組合邏輯同步拉高讀結束信號

- rd_end = 1

- 由於數據需要存入下端FIFO模塊因此需要輸出一個讀模塊工作響應信號,並且需要與數據同步,作為FIFO輸入的寫請求信號

- rd_ack = 1,需要和輸出數據同步

- 其餘信號在狀態機下完成

- 空閑狀態

- 激活

- 激活等待

- 讀命令

- 潛伏期

- 讀數據

- 預充電

- 預充電等待

- 讀結束

- 並且為了儘可能的滿足建立時間,SDRAM真正的驅動信號相比SDRAM的控制信號有-75°的相移,因此為了將SDRAM的輸入數據納入本時鐘域,需要對SDRAM的輸出數據進行打拍操作,因此看起來並不會有一拍的延遲,因為SDRAM的輸出本身就是提前了一些。

- 75°相移更多的是時序上的考量,本質上是犧牲了保持時間換取建立時間的冗餘

- 最終SDRAM讀出的數據和其同步信號輸出至下端的FIFO

- rd_sdram_data

- rd_ack

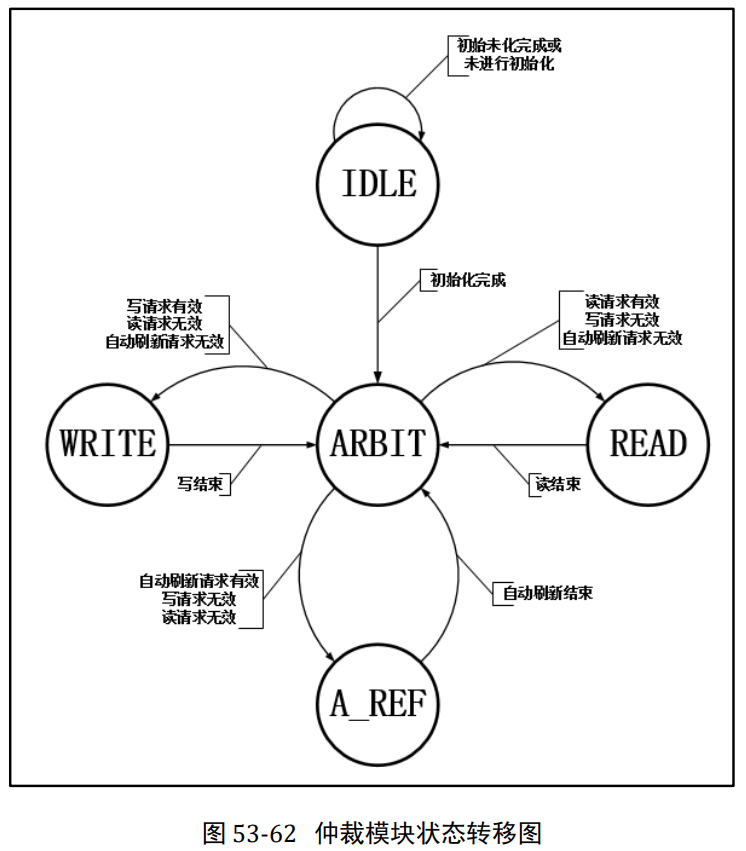

仲裁模塊 sdram_arbit

- SDRAM共有四種操作模式,且有著明確的執行 優先順序要求,其中初始化最高,次之自動刷新,最後是寫讀操作。在實際使用中不免會遇到多個模塊同時需要執行或者當前執行過程中有新的請求需要執行這兩種情況,此時就需要仲裁器來保證SDRAM收到的請求正常被執行。

- 同時優先順序的判斷在狀態跳轉條件處體現,以及在各個操作模塊的使能信號判斷條件處體現