@[TOC](靜態時序分析) # 一、TCL語言和synopsys TCL語言入門 基本目標: 1.掌握常用TCL基本指令(至少要看得懂) 2.掌握常用synopsys TCL常用指令,包括信息與屬性的獲取以及過濾 3.重點關註TCL正則匹配與文本處理方法,能夠寫出簡單的文本處理腳本 ## 1.1 ...

@

目錄一、TCL語言和synopsys TCL語言入門

基本目標:

1.掌握常用TCL基本指令(至少要看得懂)

2.掌握常用synopsys TCL常用指令,包括信息與屬性的獲取以及過濾

3.重點關註TCL正則匹配與文本處理方法,能夠寫出簡單的文本處理腳本

1.1 TCL基本指令

置換:變數置換$、命令置換[]、反斜杠置換\

變數賦值與輸出:set、puts

其他:\t、\n、""、{}、#

set X 1.2

set Y 1.3

puts "[expr $X + $Y]"

#結果為2.5

puts "\[expr $X + $Y\]"

#結果為[expr 1.2 + 1.3]

puts "\[expr \$X + \$Y\]"

#結果為[expr $X + $Y\]

puts {\[expr \$X + \$Y\]}

#結果為[expr \$X + \$Y\]

數組:使用array指令獲取數組信息

set cell_1(ref_name) "bufx2"

set cell_1(full_name) "top/cell_1"

set cel1_1(pins) "A B C"

puts $cell_1(ref_name)

#結果為bufx2

arry size cel1_1

#結果為3

arry names cel1_1

#結果為ref_name full_name pins

列表:concat、lindex、llength、lappend、lsort

set list1 {bufx1 bufx2 bufx4}

set list2 {ivtxl ivtx2 ivtx4}

concat $list1 $list2

#輸出結果為bufx1 bufx2 bufx4 ivtxl ivtx2 ivtx4

llength $list1

#輸出結果為3

llength [concat $list1 $list2]

#輸出結果為6

lindex $list1 1

#輸出結果為bufx2

lindex $list1 [expr [llength $list1] - 1]

#輸出結果為bufx4

lappend list1 bufx5

#輸出結果為bufx1 bufx2 bufx4 bufx5

set list3 {4 1 2 3 2 1}

lsort -real $list3

#按數字大小排序,輸出結果為1 1 2 2 3 4

lsort -unique $list3

#按唯一性輸出1 2 3 4

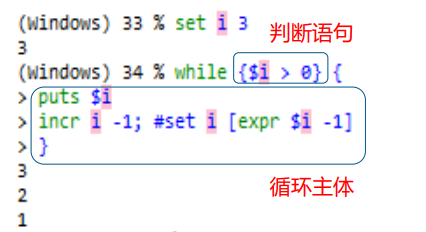

控制流:if、foreach、break、continue、while、for

Tips:腳本語句的'{'一定要寫在上一行,因為如果不這樣,TCL 解釋器會認為if命令在換行符處已結束,下一行會被當成新的命令,從而導致錯。

if

foreach……break

foreach……continue

while

for

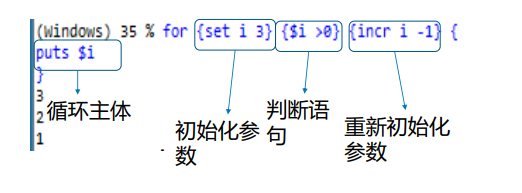

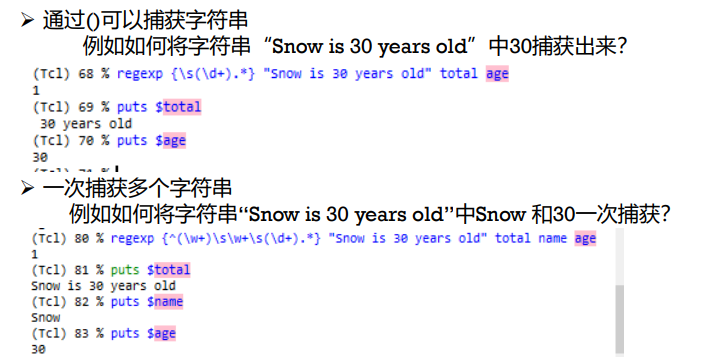

過程函數:proc

Tips:指令global,可以在過程內部引用全部變數

proc proc_name {argument} {

......

return return_value

}

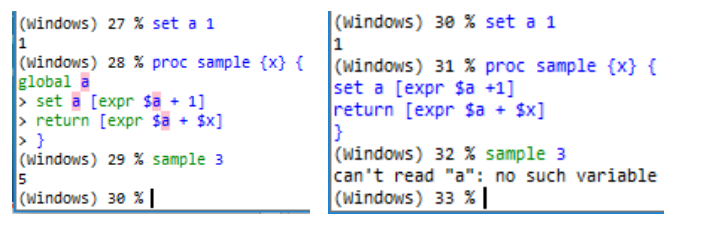

正則匹配:

\w,用來匹配一個字母、數字、下劃線

\d ,用來匹配一個數字

\s表示空格

. 表示任意一個字元

正則匹配-量詞

正則匹配-錨位

捕獲變數

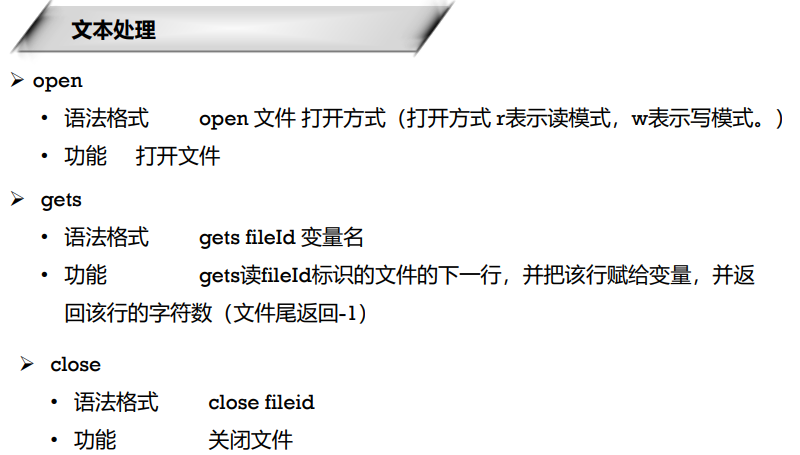

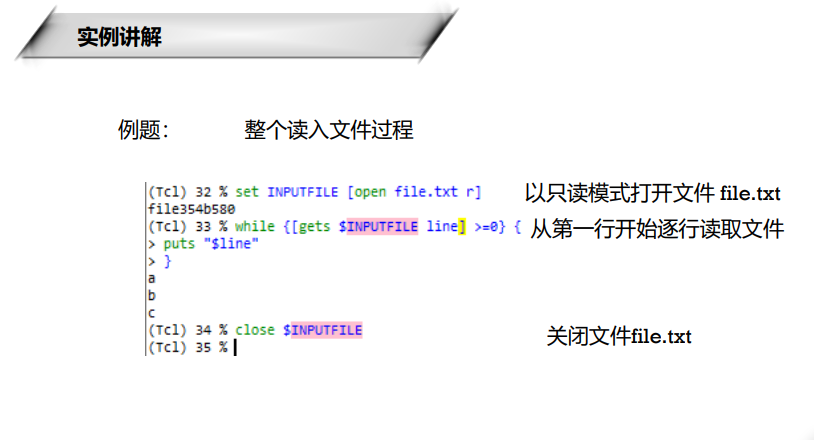

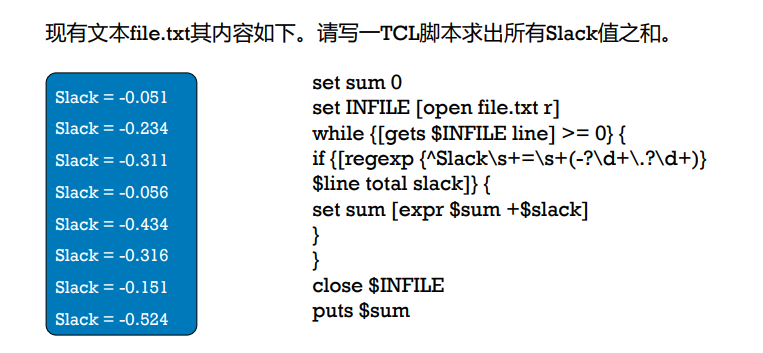

文本處理

1.2 synopsys TCL常用語言

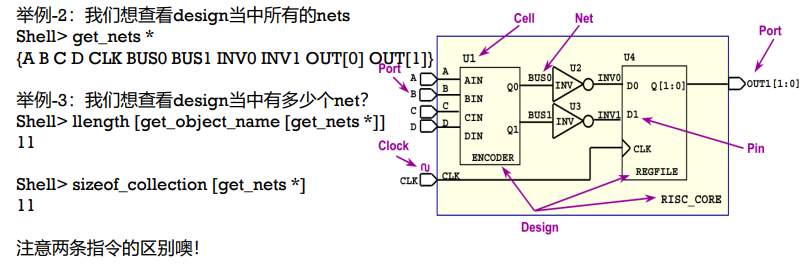

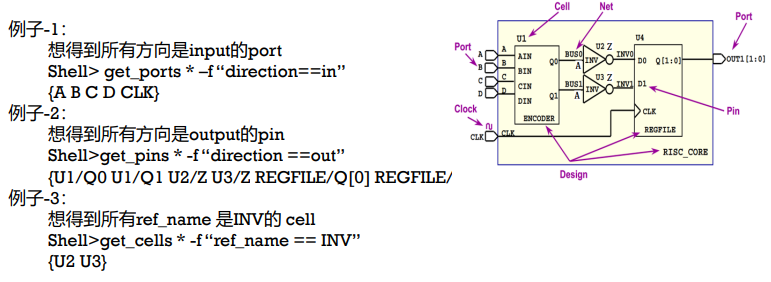

1.信息獲取

#語法

get_ports 埠名稱

get_cells 單元名稱

get_nets 網表名稱

get_pins 管腳名稱

獲取信息的時候可以搭配通配符*去獲取想要的信息,以get_ports指令為例子:

get_ports * #返回所有的埠名稱

get_ports I* #返回所有的以I開頭的埠名稱

get_ports *1 #返回所有的以1結尾的埠名稱

2.屬性獲取

get_attribute [get_cells 單元名] ref_name

#單元對象 的 ref_name 屬性:用來保存其映射到參考單元的名稱

get_attribute [get_nets 網表名] full_name

#網表對象 的 full_name 屬性:用於保存網表名稱

get_attribute [get_pins 單元/引腳] owner_net

#引腳對象 的 owner_net 屬性:用來保存與之相連的網表名稱

get_attribute [get_ports 單元名] direction

#埠對象 的 direction 屬性:用來保存埠的方向

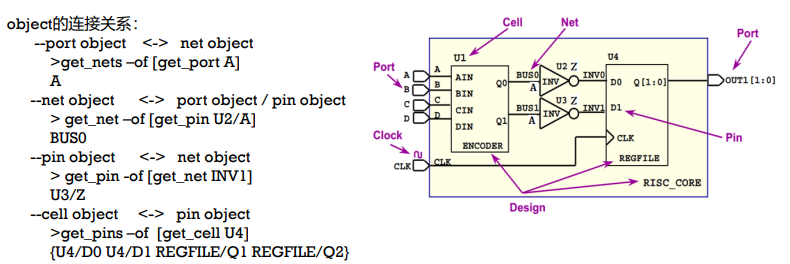

3.屬性過濾和對象連接

get_ports 埠名 -f "過濾條件"

#“-f”可以用來過濾屬性,以得到我們想要的object

get_nets -of [get_ports 埠名]

#“-of”可以用來得到指定object相連接的object

二、STA基本概念

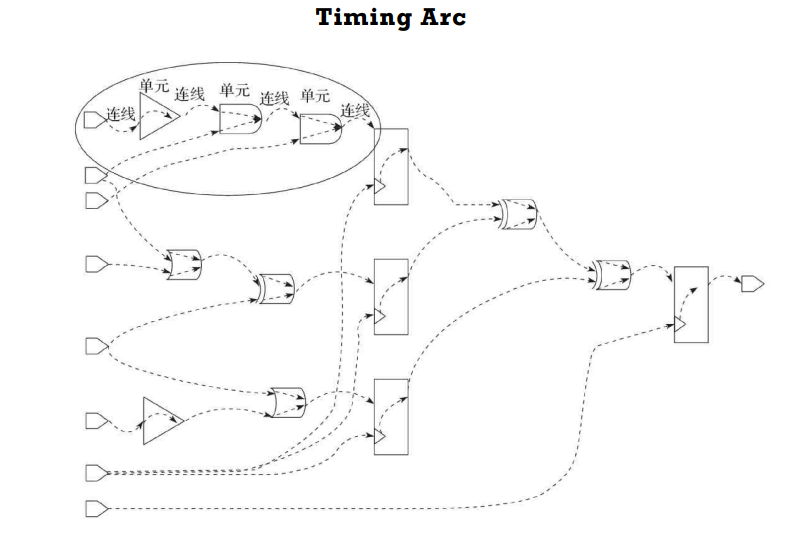

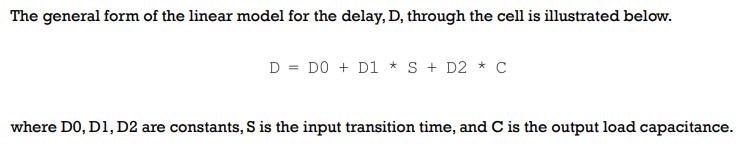

2.1 時序弧(Timing Arc)與線延遲、單元延遲

時序弧用來描述,兩個節點延時信息的參數。通常分為Net delay(線延遲)和Cell delay(單元延遲)。其中Cell delay(單元延遲)內部有兩種延遲,分別為 Transition delay(翻轉延遲)和Logic gate delay(邏輯門延遲)。

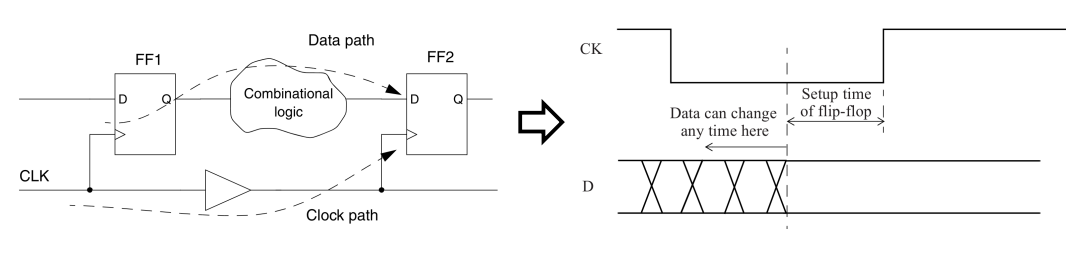

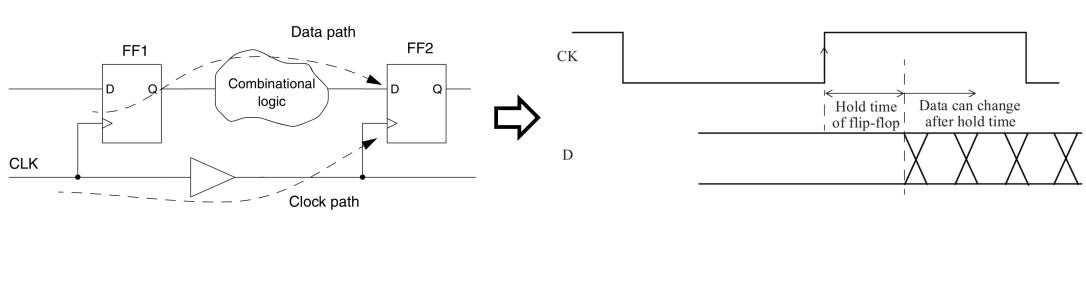

2.2 建立時間與保持時間

建立時間:在觸發器的捕獲沿到來之前,數據必須提前保持穩定的持續時間,以保證觸發器可以順利安全的取到數據。此參數可以用來約束數據路徑上的最大時序。

保持時間:在觸發器的捕獲沿到來之後數據必須保持穩定的持續時間。此參數可以用來約束數據路徑的最小時序。

Tips:建立時間與保持時間對應的最大延時和最小延時不要記反了!

2.3 時序路徑(Timing path)

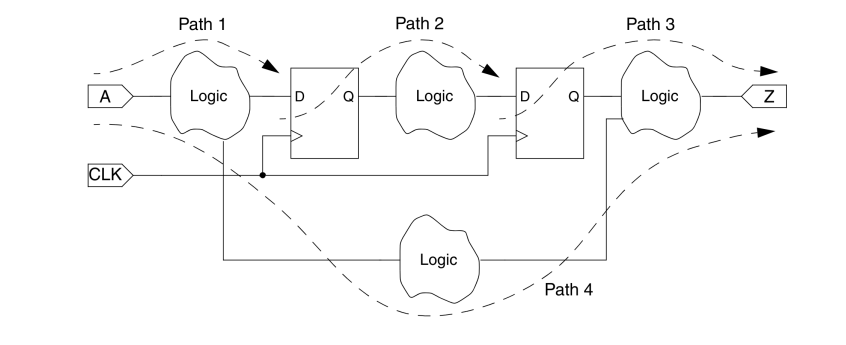

PrimeTime 進行時序分析的第一步是將設計分解為一組時序路徑。每個時序路徑都有一個起點和終點,起點和終點各有兩種,起點包括 clock pin 和 input port,終點包括data input pin 和 output port,所以一共有四種時序路徑。

2.4時鐘域(Clock Domains)

大多數數字電路都是“全局非同步,局部同步”的時序,但是所有的靜態時序分析(STA)都是針對的同步電路。

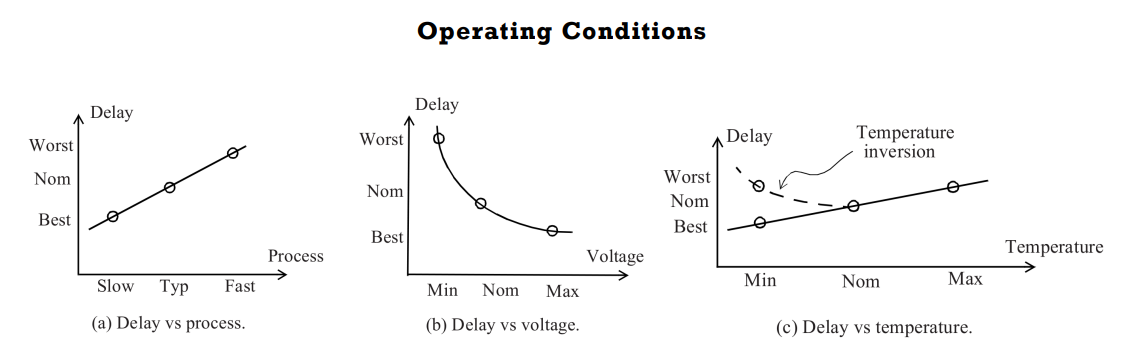

2.5 操作條件(Operating Conditions)和 PVT(Process Voltage Temperature)

由於半導體不同的工藝製成,不同的使用環境,對器件本身的延遲存在較大影響。所以在進行STA時一定要明確操作的環境和條件,主要包括工藝製程(Process)、電壓(Voltage)、溫度(Temperature)。在指定上述的條件之後,單元延時和互連線的延時也就根據上述條件進行計算分析。

工藝製程的模型主要分為3種:slow、typical、fast。其中 slow 和 fast都是極端的條件,對於穩健的設計,PVT(Process Voltage Temperature)都要在極端環境下測試通過。高溫低壓對應最壞的情況,低溫高壓對應最佳情況。

一般在最大延遲環境下檢查建立時間,在最小延遲環境下檢查保持時間。

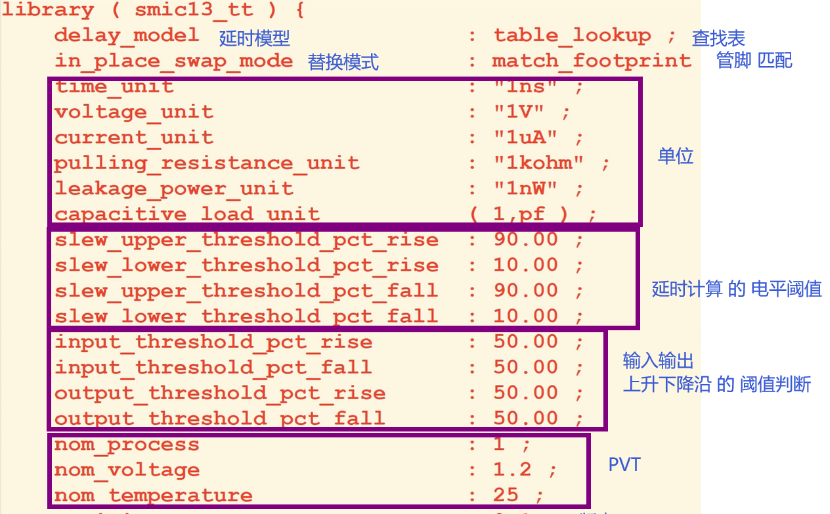

三、標準單元工藝庫

3.1 庫文件概述

通過庫文件可以讀出單元的相關信息,如下圖所示:

具體可以參考:靜態時序分析(STA)—— 標準單元庫

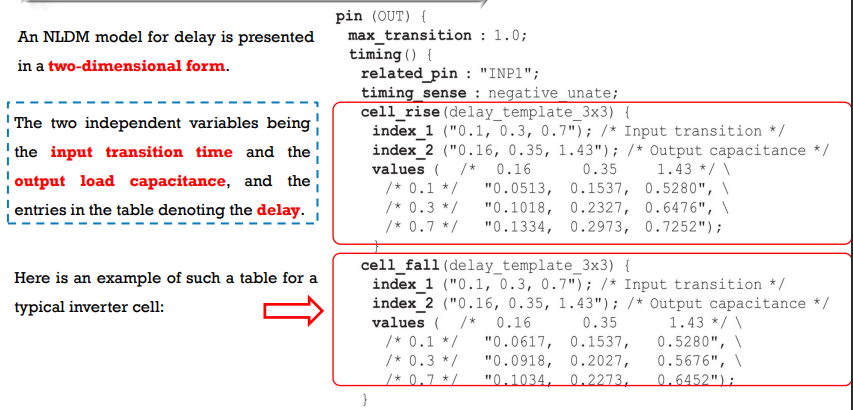

3.2 非線性延遲模型

單元延遲取決於兩個因素:輸出負載電容和電平轉換時間

1、輸出負載,即輸出端的電容負載的大小。容性負載越大,延遲越大。

2、輸入端信號高低電平轉換時間。大多數情況下,此參數越大,對應的延時也會越大。

根據電容負載和電平轉換時間可以推導出線性延遲模型去預估模型的具體延遲。然而,線性模型在微小工藝半導體器件中並不是很精確,大都數用的是非線性模型。

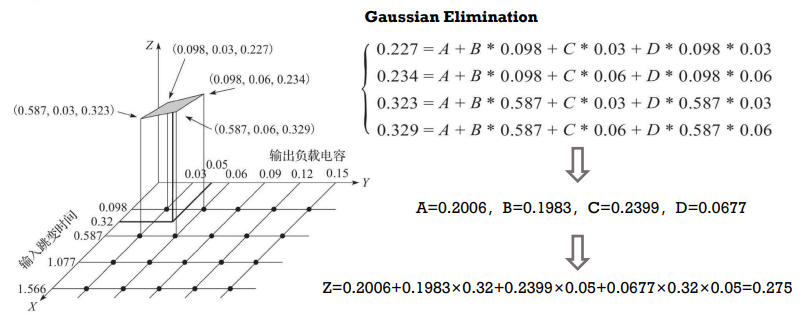

第一步:根據查表法得到對應的延時。

第二步:如果找不到對應的點,則根據相鄰的四個點進行插值然後根據高斯消元法得到模型延時。

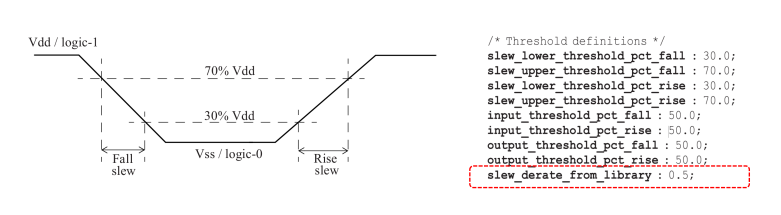

3.3 電平翻轉閾值調整(slew_derate)

電平翻轉閾值調整主要是應對一些實際工藝製程與工藝庫的不同導致延遲差異的問題。例如工藝庫單元閾值為10%—90%,而實際的工藝為30%—70%,閾值相當於下降了50%。為瞭解決這類問題,只需要slew_derate_from_library設置為0.5即可。如下圖所示:

四、建立靜態時序分析的環境

正確的約束對於分析STA結果很重要,只有準確指定設計環境,STA分析才能夠識別出設計中的所有時序問題。STA的準備工作包括設置時鐘、指定IO時序特性以及指定偽路徑和多周期路徑。

什麼是STA環境?大部分數字設計是同步的,從前一個時鐘周期計算出的數據在時鐘有效沿上被鎖存在觸發器中。為了對這種設計執行STA,需要指定觸發器的時鐘、以及進入設計和退出設計的所有路徑的時序約束。

4.1 Specifying Clocks

4.1.1(主)時鐘定義

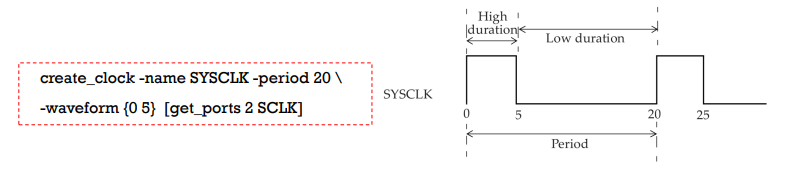

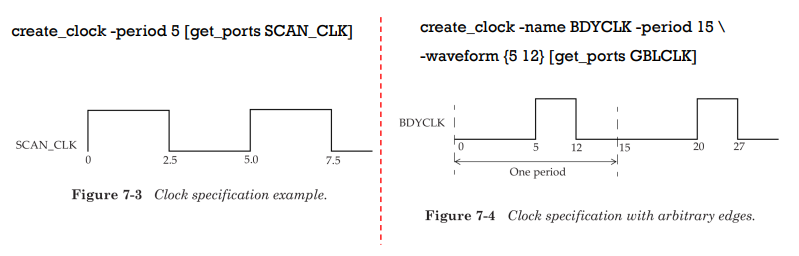

要定義時鐘,我們需要提供以下信息:時鐘源(Clock source)、周期(Period)、占空比(Duty cycle)邊沿時間(Edge times)。

以下是一個基本的時鐘約束規範:

create_clock -name SYSCLK -period 20 -waveform {0 5} [get_ports SCLK]

4.1.2.時鐘不確定度(set_clock_uncertainty)

可以使用set_clock_uncertainty約束來指定時鐘周期的時序不確定度(uncertainty),該不確定度可用於對可能會減少有效時鐘周期的各種因素進行建模。 這些因素可能是時鐘抖動(jitter)以及可能需要在時序分析中考慮的任何其它悲觀度。建立時鐘不確定性聲明,會使整個電路的時序變得更加嚴苛,滿足設計的穩健性。

時鐘不確定性的主要來由:

時鐘偏差(clock skew):時鐘源到達不同觸發器的時間偏差

時鐘抖動(clock jitter):時鐘邊沿的超前或滯後

時鐘延遲(clock delay):網路延遲和源延遲

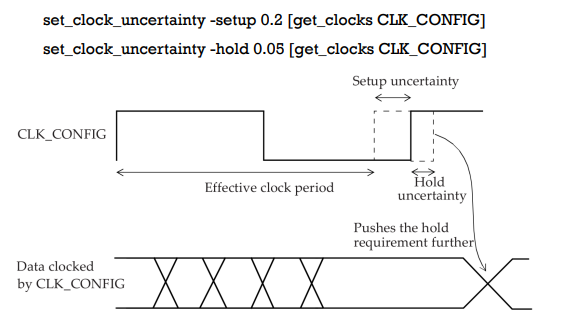

對於保持時間檢查,時鐘不確定度將用作需要滿足的額外時序裕量,如下圖所示:

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG]

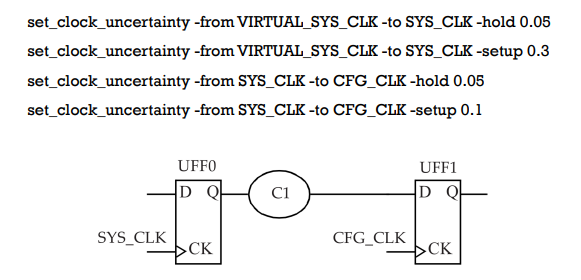

以下命令可用於指定跨時鐘邊界路徑上的時鐘不確定度:

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYSCLK -hold 0.05

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYSCLK -setup 0.3

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

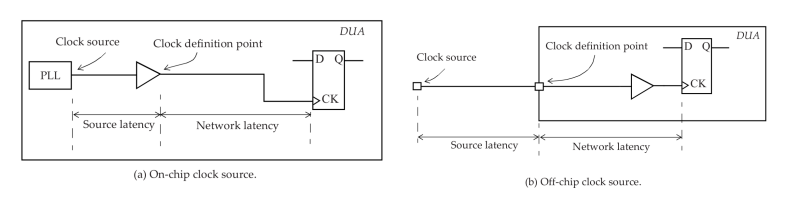

4.1.3 時鐘延遲

時鐘延遲分為兩種類型:網路延遲(network latency)和源延遲(source latency)。網路延遲是指從時鐘定義點(create_clock)到觸發器時鐘引腳的延遲,源延遲是指從時鐘源到時鐘定義點(create_clock)的延遲。具體如下圖所示:

以下指令可以指定時鐘的延遲:

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

# Specify a network latency (no -source option) of 0.8ns for rise, fall, max and min.

set_clock_latency 1.9 -source [get_clocks SYS_CLK]

# Specify a source latency

set_clock_latency 0.851 -source -min [get_clocks CFG_CLK]

# Specify a min source latency

set_clock_latency 1.322 -source -max [get_clocks CFG_CLK]

# Specifv a max source latency

set_clock_latency 1.8 -rise [get_clocks MAIN_CLK]

# Specify a rise latency

set_clock_latency 2.1 -fall [all_clocks]

# Specify a fall latency

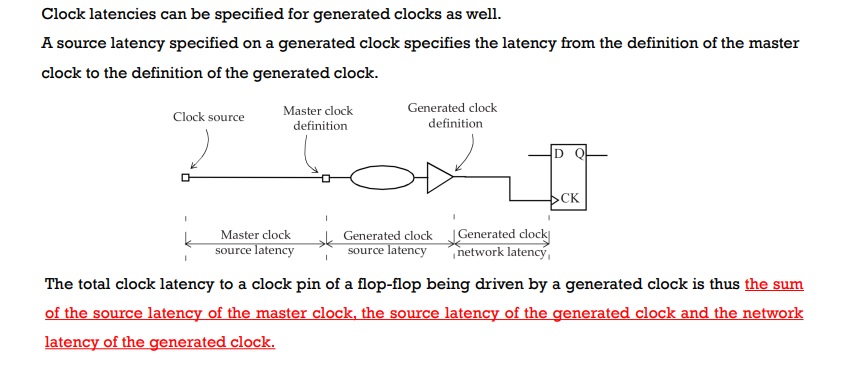

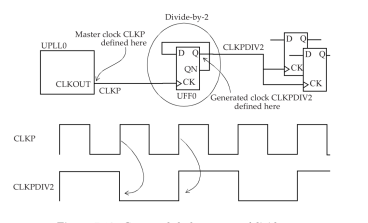

4.2 Generated Clocks

衍生時鐘是從主時鐘(master clock)派生而來的時鐘,主時鐘是指使用create_clock命令定義的時鐘。在基於主時鐘的設計中生成一個新時鐘時,可以將這個新時鐘定義為衍生時鐘。

例如根據一個時鐘周期為10的主時鐘CLKP生成一個二分頻衍生時鐘CLKPDIV2,指令示例如下:

create_clock -name CLKP 10 [get_pins UPLL0/CLKOUT]

#主時鐘

create_generated_clock -name CLKPDIV2 -source UPPL0/CLKOUT -divide_by 2 [get_pins UFF0/Q]

#衍生時鐘

可以在觸發器的輸出端定義一個新的時鐘,即主時鐘,而不是生成的時鐘嗎?

答案是肯定的,但是有一些缺點。定義一個主時鐘而不是一個衍生時鐘會創建一個新的時鐘域,軟體工具會當做非同步時鐘處理而不是同步時鐘處理。將新時鐘定義為衍生時鐘不會創建新的時鐘域,並且衍生時鐘被認為與其主時鐘同相,衍生時鐘不需要開發額外的約束。因此,儘量將內部新生成的時鐘定義為衍生時鐘,而不是將其聲明為另一個主時鐘。

主時鐘和衍生時鐘之間的另一個重要區別是時鐘源的概念。在主時鐘中,時鐘源位於主時鐘的定義點。而在衍生時鐘中,時鐘源是主時鐘的源而不是衍生時鐘的源。這意味著在時鐘路徑報告中,時鐘路徑的起點始終是主時鐘的定義點。這樣一來,與定義新的主時鐘相比,衍生時鐘具有很大優勢,是不會自動考慮源延遲的。因此,由衍生時鐘驅動的觸發器的時鐘引腳的總時鐘延遲是主時鐘源延遲、衍生時鐘源延遲和衍生時鐘網路延遲的總和。如下圖所示:

相反的,如果時鐘操作輸出的時鐘和源時鐘沒有太多關係(不是直接的倍頻分頻等),失去了相位和周期的繼承性,那麼此時輸出的時鐘就是可以定義為主時鐘,而非衍生時鐘。

4.3 Constraining Input Paths and Output Path

為什麼需要進行輸入輸出路徑的約束?

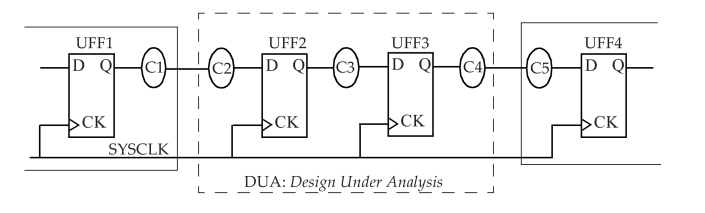

這裡需要註意的一點是,STA無法檢查不受約束的路徑上的任何時序,因此需要約束所有路徑以進行時序分析。輸入輸出路徑的約束關係可以用來確定可靠地捕獲DUA內部數據的可用時間。

1.輸入路徑約束

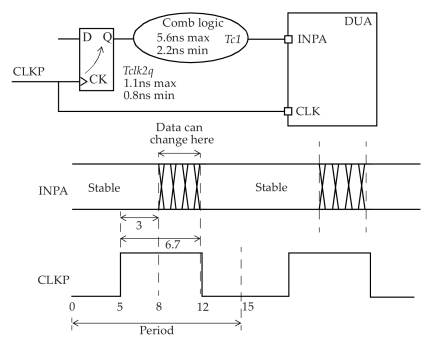

讓我們同時考慮最大和最小延遲情況,以下是輸入路徑的約束:

create_clock -period 15 -waveform {5 12} [get_ports CLKP]

set_input_delay -clock CLKP -max 6.7 [get_ports INPA]

set_input_delay -clock CLKP -min 3.0 [get_ports INPA]

可以通過約束關係得到:CLK到INPA的最大延遲為和最小延遲分別為6.7ns和3.0ns,已知時鐘周期為15ns,則可以得到8.3ns是用來可靠地捕獲DUA內部數據的可用時間。

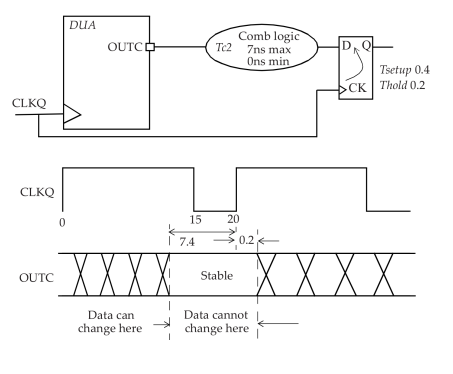

2.輸出路徑約束

讓我們同時考慮最大和最小延遲情況,以下是輸入路徑的約束:

create_clock -period 20 -waveform {0 15} [get_ports CLKQ]

set_output_delay -clock CLKQ -min -0.2 [get_ports OUTC]

set_output_delay -clock CLKQ -max 7.4 [get_ports OUTC]

可以通過約束關係得到:CLKQ到OUTC的最大延遲為和最小延遲分別為7.4ns和-0.2ns,已知時鐘周期為15ns,則可以得到7.6ns是OUTC必須保持穩定狀態的時間。

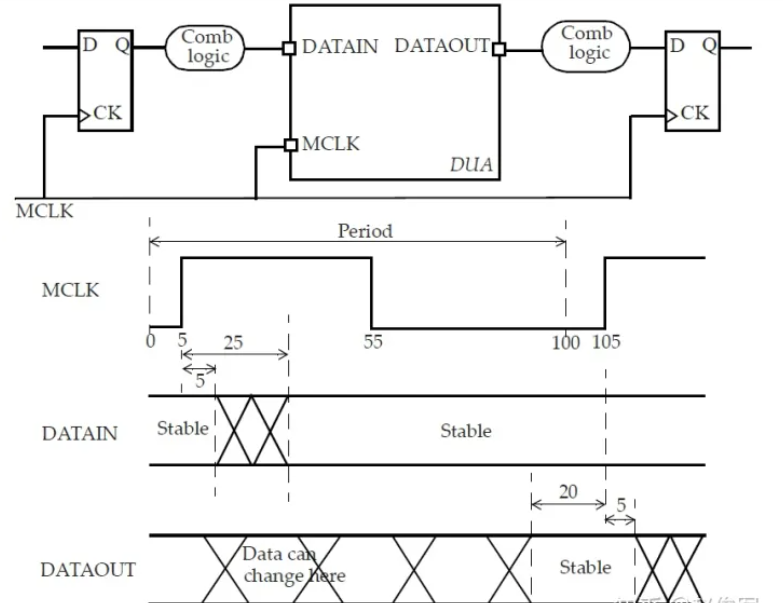

3.輸入輸出路徑約束

補充:

1.瞭解時序路徑組(Timing Path Groups):由終點決定命名

2.瞭解外部屬性建模(Modeling of External Attributes

):對於輸入,需要在輸入埠處指定驅動強度;對於輸出,需要指定輸出引腳的負載電容;

#輸入驅動

set_drive 100 UCLK

set_drive -rise 3 [all_inputs]

set_drive -fall 2 [all_inputs]

#指定驅動強度,數字代表驅動電阻,電阻越小驅動強度越高,0表示無限的驅動強度

#第一種已經過時,不推薦

set_driving_cell -lib_cell INV3 -library slow [get_ports INPB]

set_driving_cell -lib_cell INV2 -library tech13g [all_inputs]

set_driving_cell -lib_cell BUFFD4 -library tech90gwc [get_ports {testmode[3]}]

#指定驅動輸入埠的單元類型

#第二種功能同第一種,用法更精準更方便

set_input_transition 0.85 [get_ports INPC]

set_input_transition 0.6 [all_inputs]

set_input_transition 0.25 [get_ports SD_DIN*]

#輸入埠表示過渡時間的便捷方法

#第三種更為直接,直接指定輸入埠的轉換時間;

#輸出驅動

set_load 5 [get_ports OUTX]

set_load 25 [all_outputs]

set_load -pin_load 0.007 [get_ports {shift_write[31]}]

#輸出負載影響驅動輸出的單元的延遲,數值越小延遲越小

4.4 Design Rule Checks(DRC)

STA中兩個常用的設計規則是最大過渡時間-max_transition和最大電容-max_capacitance。這些規則將會檢查設計中的所有埠和引腳是否滿足過渡時間和電容的規定約束。作為STA的一部分,任何設計規則的違例(violation)均以裕量(slack)的形式報告。這些規則可以使用以下命令指定:

set_max_transition 0.6 IOBANK

set_max_capacitance 0.5 [current_design]

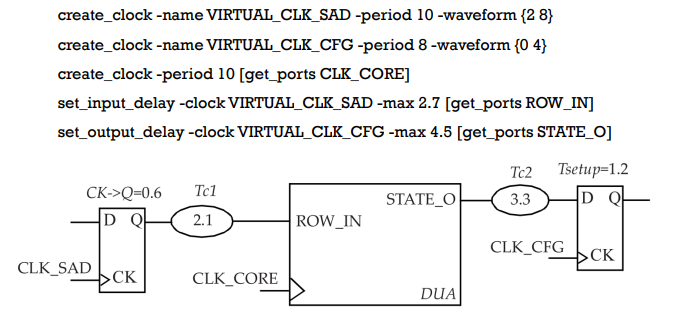

4.5 Virtual Clocks

虛擬時鐘存在但是不和設計中的埠和引腳相連接。它在STA分析中用作參考,以指定相對於時鐘的輸入和輸出延遲。

4.6 Refining the Timing Analysis

用於精細化約束分析的四個常用命令是:

set_case_analysis

#在單元的引腳或輸入埠上指定常量值。

set_disable_timing

#中斷單元的時序弧。

set_false_path

#指定實際不存在的路徑,這意味著在STA中不需要檢查這些路徑。

set_multicycle_path

#指定可能花費超過一個時鐘周期的路徑。

1.指定無效信號

主要面臨的情況是DFT、多功能模式和MUX:

1.如果晶元中具有DFT(可測性設計)邏輯,則在正常功能模式下,晶元的TEST引腳將一直為0。

2.如果設計具有多種功能模式,而只需要分析其中一種功能模式,則可以使用set_case_analysis來指定要分析的模式。

3.在MUX設計中指定set_case_analysis,分別對每個信號進行分析是十分必要的。

set_case_analysis 0 TEST

set_case_analysis 0 [get_ports {testmode[3]}]

set_case_analysis 0 [get_ports {testmode[2]}]

set_case_analysis 0 [get_ports {testmode[1]}]

set_case_analysis 0 [get_ports {testmode[0]}]

#指定DFT端信號無效

set_case_analysis 1 func_mode[0]

set_case_analysis 0 func_mode[1]

set_case_analysis 1 func_mode[2]

#具有多功能的模塊,對每個功能分別單獨分析

set_case_analysis 1 UCORE/UMUX0/CLK_SEL[0]

set_case_analysis 1 UCORE/UMUX1/CLK_SEL[1]

set_case_analysis 0 UCORE/UMUX2/CLK_SEL[2]

#對MUX每個信號單獨分析

2.中斷單元內的時序弧

在某些情況下,單元中的一條路徑可能無法發生。由於時序弧不再存在,因此需要分析的時序路徑更少。

使用set_disable_timing命令需要格外小心,因為它會刪除通過指定引腳的所有時序路徑。在可能的情況下,最好使用set_false_path和set_case_analysis命令。

set_disable_timing -from S -to Z [get_cells UMUX0]

#直接中斷時序弧

3.偽路徑時序分析

指定實際不存在的路徑,這意味著在STA中不需要檢查這些路徑。偽路徑約束很重要,對於跨時鐘域的模塊之間的路徑,不予分析。註意,偽路徑約束是單向的。偽時序路徑後文重點分析。

4.多周期路徑時序分析

信號傳輸可能花費超過一個時鐘周期的路徑。輸入到輸出的延遲跨越了多個時鐘周期。多周期時序路徑後文重點分析。

五、時序檢查

5.1 建立時間與保持時間檢查方法

5.1.1建立時間檢查

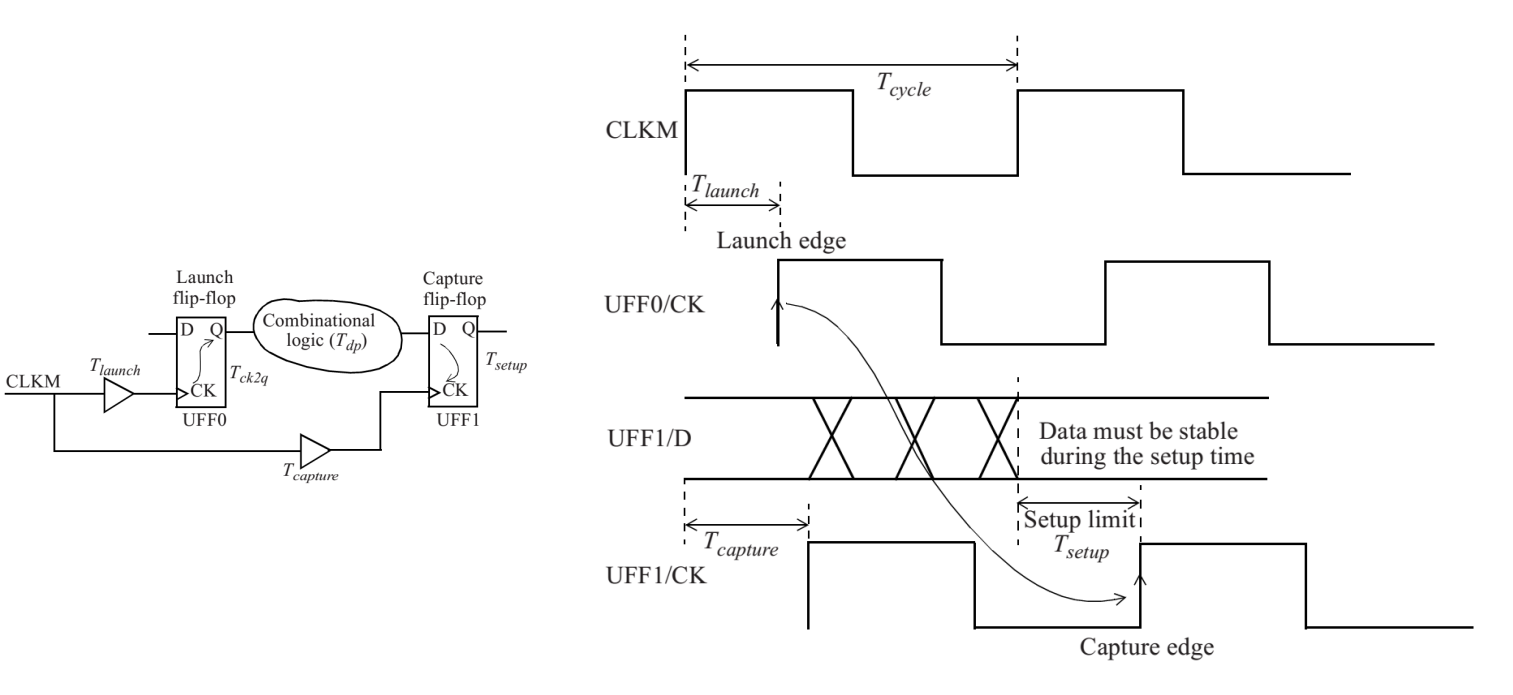

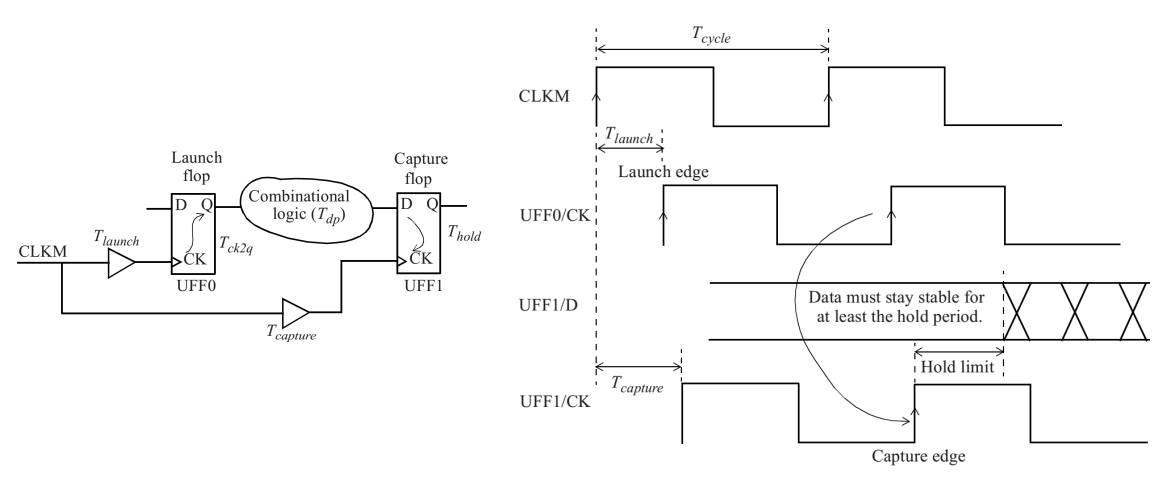

建立時間檢查可以用數學公式表示:

$$T_{launch}+T_{ck2q}+T_{dp} < T_{capture}+T_{cycle}-T_{setup}$$

通常,有一個發起觸發器(用於發起數據的觸發器)和捕獲觸發器(用於捕獲數據的觸發器),這個捕獲觸發器的建立時間要求必須滿足上述公式。換而言之,數據到達捕獲觸發器D引腳所花費的總時間必須小於時鐘傳輸到捕獲觸發器所花費的時間加上時鐘周期再減去建立時間要求。

由於建立時間檢查受到 -max的約束,因此建立時間檢查始終使用 最長或最大的時序路徑。出於同樣的原因,通常在 延遲最大的慢工藝角(slow corner)下執行建立時間檢查。

具體時序如下所示:

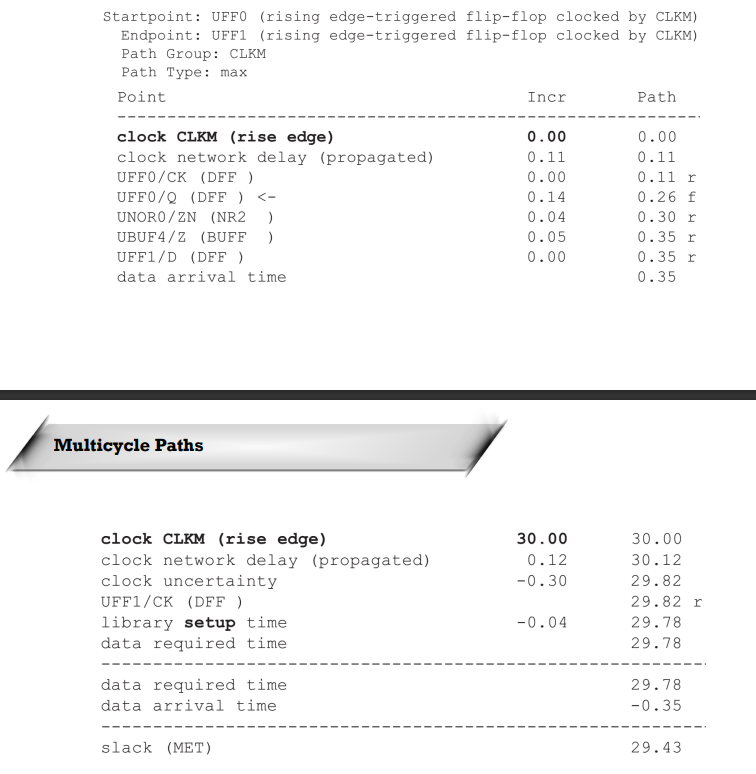

在前面我們知道時序路徑有四種,如下為觸發器到觸發器的時序報告:

其他三條時序路徑不再贅述,具體可查看靜態時序分析聖經翻譯計劃——第八章:時序檢查(上)

時序報告中的時鐘網路延遲(clock network delay)是什麼?為什麼將其標記為理想(ideal)?

時序報告中的這一行表明時鐘樹被認為是理想的,時鐘路徑中的任何緩衝器(buffer)都假定為零延遲。一旦構建了時鐘樹,就可以將時鐘網路標記為“已傳播”(propagated),從而使得時鐘路徑顯示實際延遲值,例如時序報告中所示:0.11ns延遲是發起時鐘上的時鐘網路延遲,而0.12ns延遲是捕獲觸發器上的時鐘網路延遲。

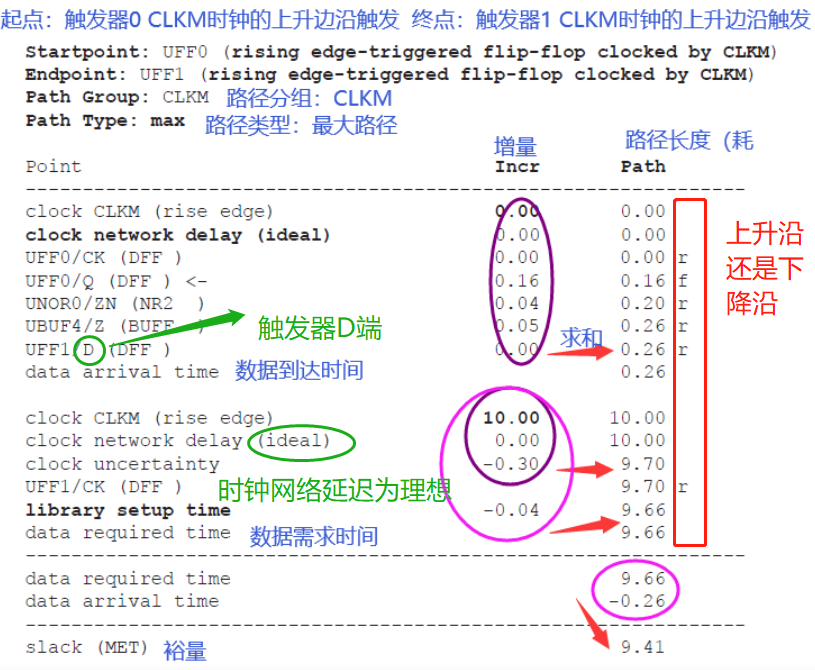

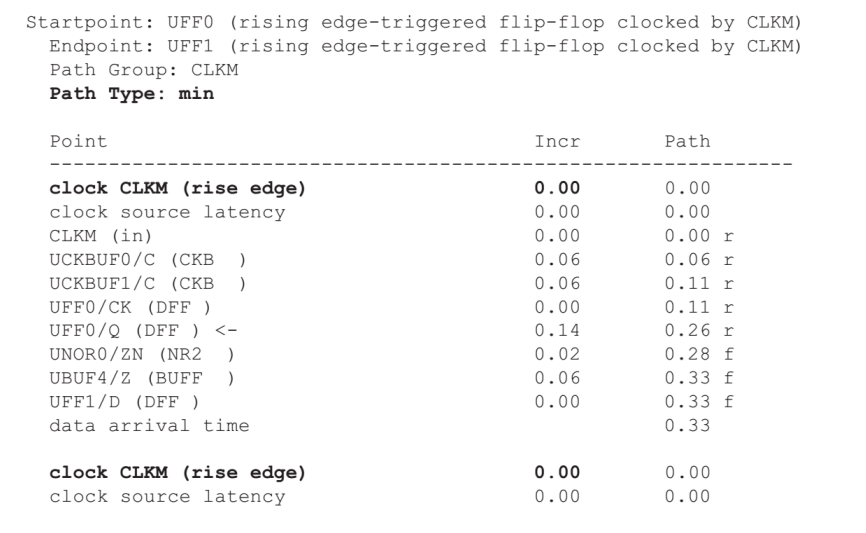

5.1.2保持時間檢查

保持時間時間檢查可以用數學公式表示:

$$T_{launch} + T_{ck2q} + T_{dp} > T_{capture} + T_{hold}$$

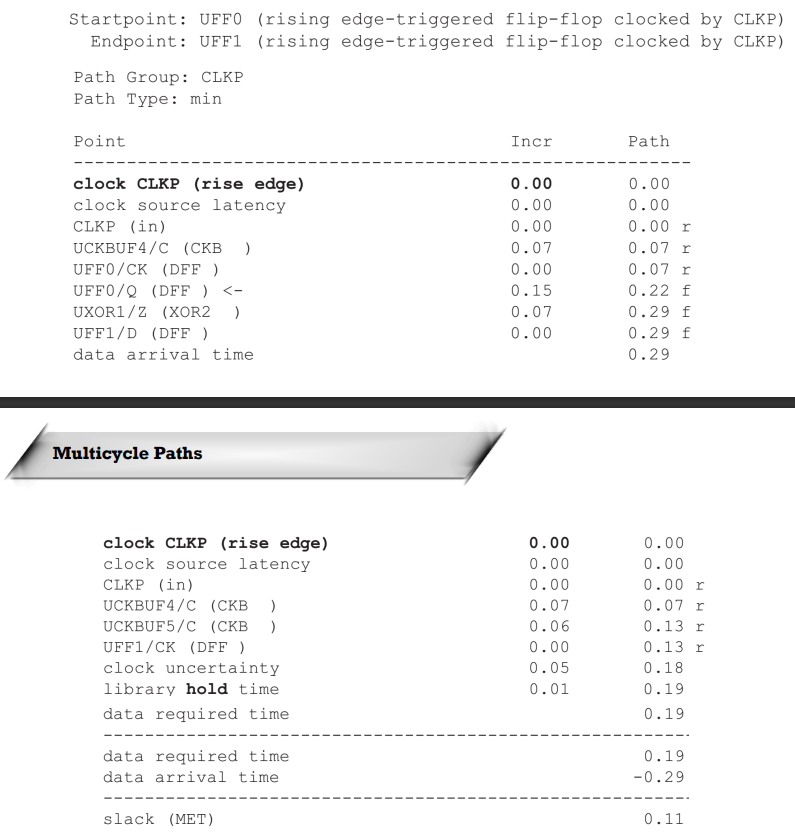

保持時間是在發起觸發器(發起數據的觸發器)和捕獲觸發器(捕獲數據的觸發器以及必須滿足其保持時間要求的觸發器)之間進行檢查的,保持時間檢查從發起觸發器時鐘的一個有效沿到捕獲觸發器中相同的時鐘沿。因此,保持時間檢查與時鐘周期無關,保持時間檢查會在捕獲觸發器時鐘的每個有效沿上執行。

保持時間檢查對捕獲觸發器的數據路徑施加了最小值 -min 約束,使用 最短或最小的時序路徑來進行保持時間檢查,同樣,在 延遲最小的快工藝角(fast corner)下執行建立時間檢查。

具體時序如下所示:

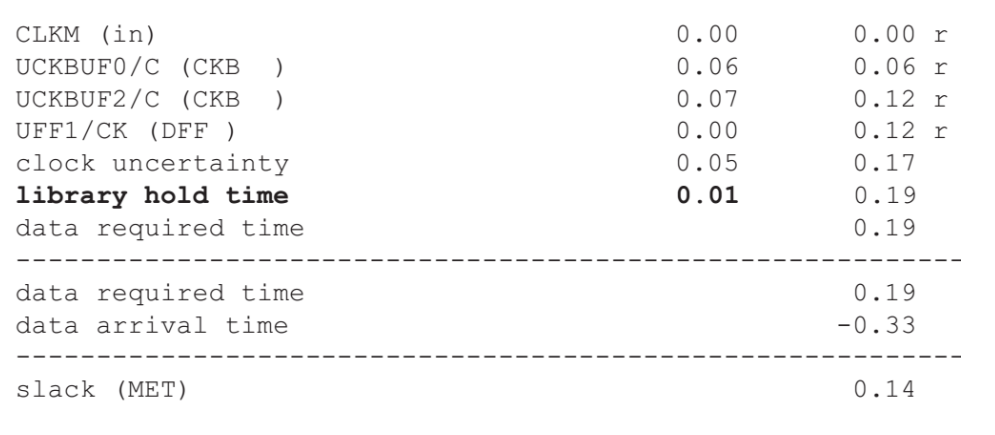

在前面我們知道時序路徑有四種,如下為觸發器到觸發器的時序報告:

Tips:對於建立時間與保持時間的裕值slack的計算並不相同,建立時間的slack為數據需要到達時間 - 數據實際到達時間,正值則表示不違例;保持時間的slack為數據需要到達時間 - 數據實際到達時間,然後添加負號,最終正值則表示不違例。(時序報告數據實際到達時間的“-”表示此為時間為實際到達時間,計算時去絕對值即可)

5.2 多周期路徑、半周期路徑、偽路徑時序檢查

5.2.1 多周期路徑檢查

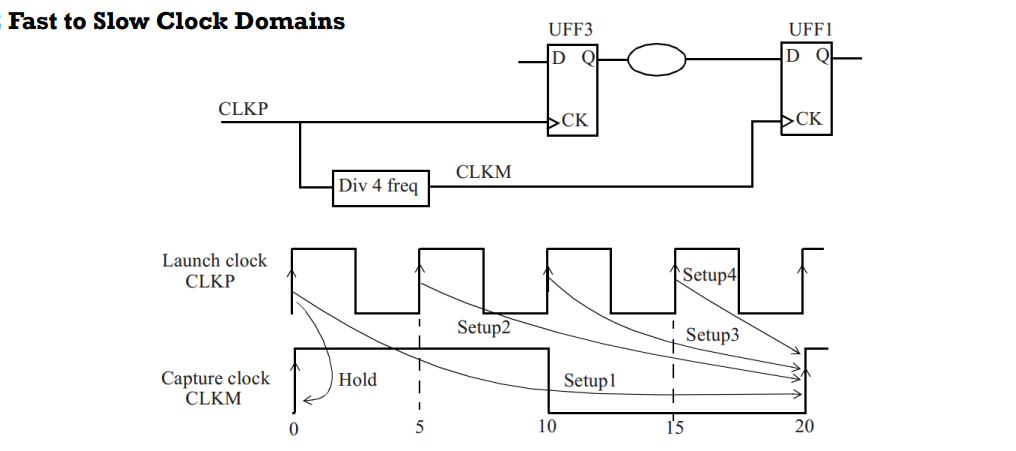

在某些情況下,兩個觸發器之間的數據路徑可能需要一個以上的時鐘周期才能傳播通過邏輯。在這種情況下,這條組合邏輯路徑會被定義為多周期路徑(multicycle path)。雖然數據還是會在每個時鐘沿上都被捕獲觸發器捕獲,但我們需要告知STA在指定數量的時鐘周期之後才會出現有效的捕獲時鐘沿。

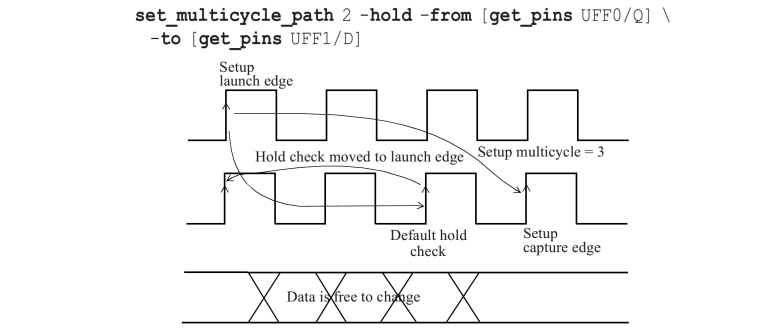

對多周期路徑進行如下約束:

create_clock -name CLKM -period 10 [get_ports CLKM]

#主時鐘CLKM

set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

#建立時間多周期約束

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

#保持時間多周期約束,將保持時間檢查邊沿前移兩個時鐘周期

Tips:如果保持時間的檢查邊沿沒有移動到launch edge,則對於後序的保持時間要求太嚴苛,即數據在多周期都要求保持不變,這顯然是難以實現的。只有對保持時間的檢查邊沿前移 N-1 個時鐘周期才能更加滿足時序要求。

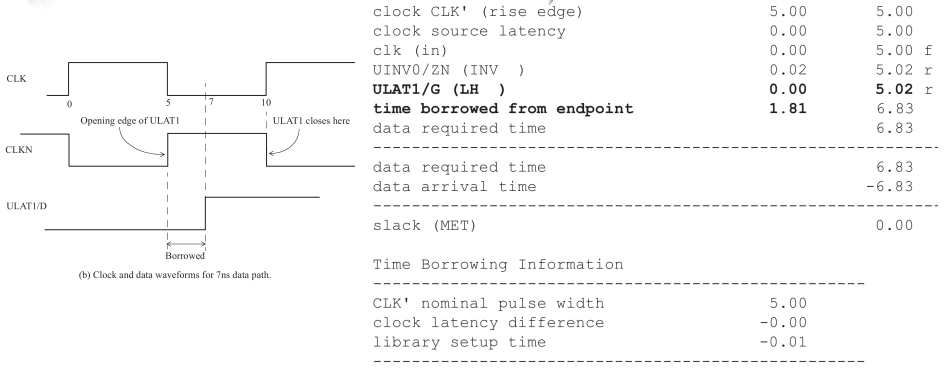

建立時間時序報告

保持時間時序報告

5.2.2 半周期路徑

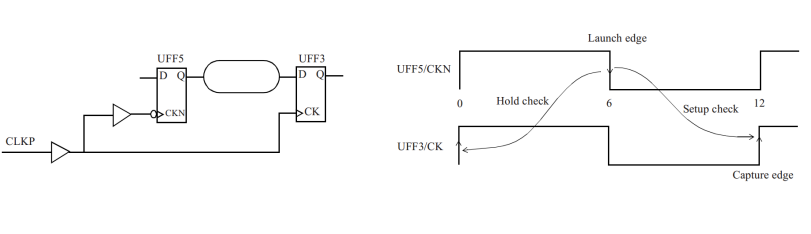

如果設計中同時具有負邊沿觸發的觸發器(有效時鐘沿為下降沿)和正邊沿觸發的觸發器(有效時鐘沿為上升沿),則設計中可能存在半周期路徑(half-cycle path)。半周期路徑可能是從一個觸發器的上升沿到另一個觸發器的下降沿,或者反過來。半周期導致建立時間時序更加嚴苛,而保持時間時序更加寬鬆。

5.2.3 偽路徑

當設計的功能運行時,某些時序路徑可能不真實(或不可能)存在。在執行STA時可以將這些路徑設置為偽路徑(false path),這樣就可以關閉這些路徑,那麼STA就不會對這些偽路徑去進行分析了。一般來說,跨時鐘域信號涉及的路徑都不用STA,所以跨時鐘域的路徑都需要設置偽路徑。

set_false_path -from [get_clocks clockA] -to [get_clocks clockB]

set_false_path -from [get_pins {regA_ * }/CK] -to [get_pins {regB_ * }/D]

set_false_path -through [get_pins UMUX0/S]

Tips:

①少用-through選項,因為會增加時序分析的複雜程度。僅在絕對有必要且沒有替代方法可以指定該偽路徑的情況下,才可以使用-through選項。

②儘量直接抓取時鐘,例如第一條約束與第二條約束,速度更快。

③不要將一條多周期路徑約束為偽路徑。

5.3 恢復時間與去除時間

恢復時間(Recovery Time):是指非同步控制信號(如寄存器的非同步清除和置位控制信號)在“下個時鐘沿”來臨之前變無效的最小時間長度。這個時間的意義是,如果保證不了這個最小恢復時間,沒有給寄存器留有足夠時間來恢復至正常狀態,那麼由於離得太近就不能保證“下個時鐘沿”能正常作用導致“時鐘沿”可能會失效。

去除時間(Removal Time):是指非同步控制信號(如寄存器的非同步清除和置位控制信號)在“有效時鐘沿”之後變無效的最小時間長度。這個時間的意義是,如果保證不了這個去除時間,那麼由於離得太近就不能保證有效地屏蔽這個“時鐘沿”。

尤其註意,恢復時間與去除時間是針對非同步控制信號而言的!如果不對非同步控制信號進行 Recovery Time 和 Removal Time 時序約束,也就是說可能會造成寄存器處於不確定的狀態。而這些情況是應該避免的。

Tips:單從時序的位置看,可以將恢復時間、去除時間類比為建立時間、保持時間。

5.4 跨時鐘域時序

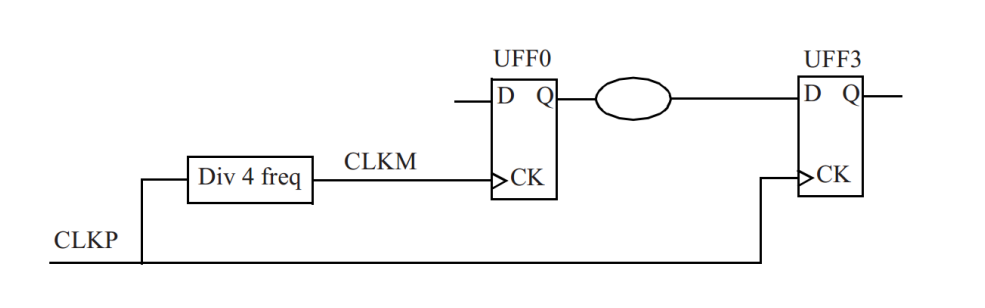

5.4.1 慢時鐘域到快時鐘域

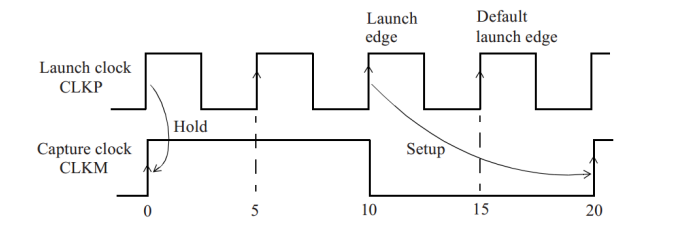

時序分析一般選擇最嚴苛的路徑進行分析,最嚴苛的建立時間和保持時間時序如下圖所示:

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

#時鐘定義

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] -end

#多周期約束檢查建立時間

set_multicycle_path 3 -hold -from [get_clocks CLKM] -to [get_clocks CLKP] -end

##多周期約束檢查保持時間

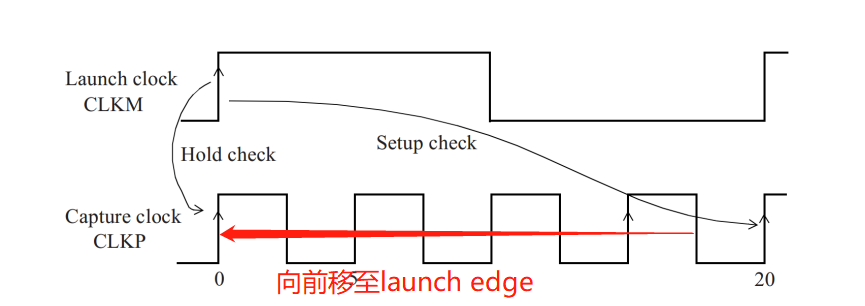

5.4 2 快時鐘域到慢時鐘域

時序分析一般選擇最嚴苛的路徑進行分析,最嚴苛的建立時間為 Setup4,如果對時序放寬鬆則選擇其他檢查邊沿,例如以 Setup2 作為檢查邊沿進行寬鬆的時序分析,建立時間和保持時間時序如下圖所示:

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

#時鐘定義

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] -start

#多周期約束檢查建立時間

set_multicycle_path 1 -hold -from [get_clocks CLKP] -to [get_clocks CLKM] -start

#多周期約束檢查保持時間

補充:選項-end是對捕獲端時鐘周期進行移動,-start是對發射端時鐘周期進行移動。

5.5 多時鐘

5.4.1 整數倍關係

參考5.3部分慢時鐘域到快時鐘域和快時鐘域到慢時鐘域

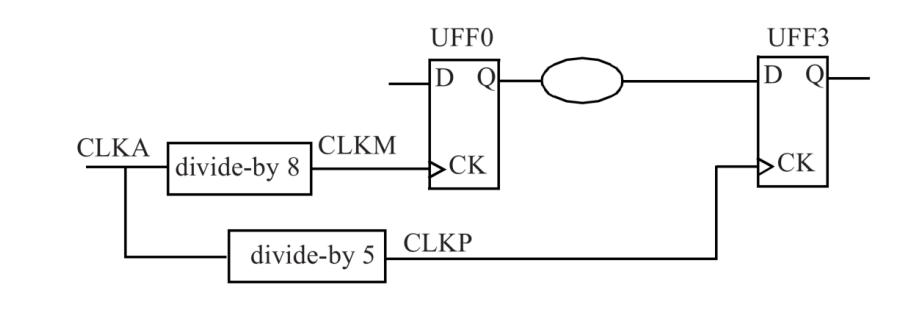

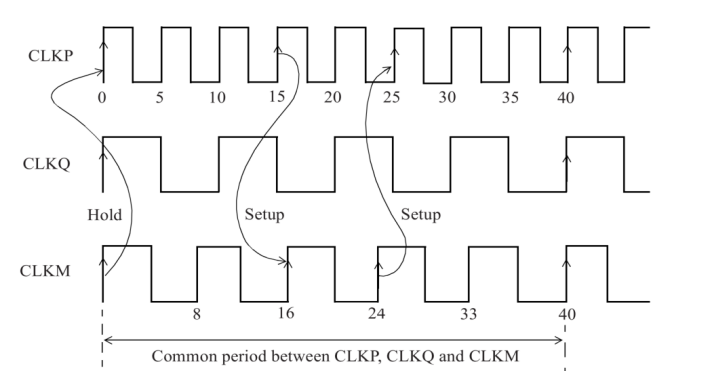

5.4.2 非整數倍關係

最重要的是找出最小公共周期!然後再將時鐘擴展到該公共周期。

CLKQ和CLKP之間數據路徑的公共周期僅擴展為10ns的公共周期;

CLKM和CLKQ之間數據路徑的公共周期為40ns;

而CLKM和CLKP之間數據路徑的公共周期也為40ns。

最嚴苛的建立時間檢查是在時鐘發起沿和捕獲沿之間的最短時間內進行。最嚴格的保持時間檢查是從0ns處的CLKM發起沿到0ns處的CLKP捕獲沿。

以CLKM時鐘域到CLKP時鐘域的數據路徑分析為例子:最嚴苛的建立時間檢查就是24ns處的時鐘CLKM發起沿以及25ns處的時鐘CLKP捕獲沿,最嚴苛的保持時間檢查從0ns處的CLKM發起沿到0ns處的CLKP捕獲沿。

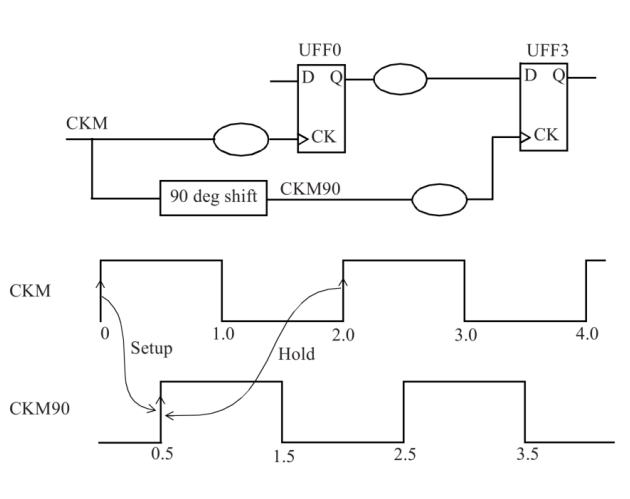

5.4.3 相移關係

建立時間:距離發射沿最近的捕獲沿就是建立時間的檢查邊沿。

保持時間:建立時間檢查的捕獲邊沿前一個有效邊沿就是保持時間的檢查邊沿。

六、魯棒性檢查

本章節將介紹特殊的STA分析,例如時間借用(time borrowing)、時鐘門控(clock gating)和非時序(non-sequential)檢查。此外,還介紹了高級STA概念,例如片上變化(on-chip variation)、統計時序(statistical timing)以及功耗和時序之間的折中。

6.1 片上變化(OCV)

6.1.1 降額(derate)

什麼是片上變化?

不同製造批次中的工藝參數差異可能會覆蓋慢工藝到快工藝,而片上變化是一個晶元上的局部工藝差異和不同的電源電壓和溫度導致的,該差異遠小於不同製造批次之間的差異(稱為全局工藝差異)。因此,同一晶元的兩個區域可能不在相同的PVT條件下。

為了消除或者減小片上變化,可以通過降額(derate)特定路徑的延遲就可以對OCV帶來的影響進行建模。

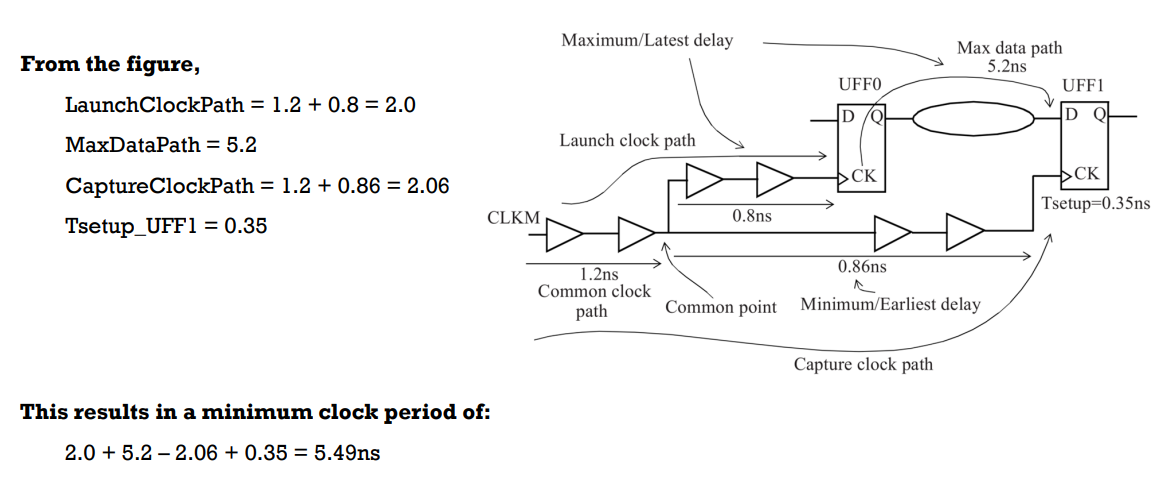

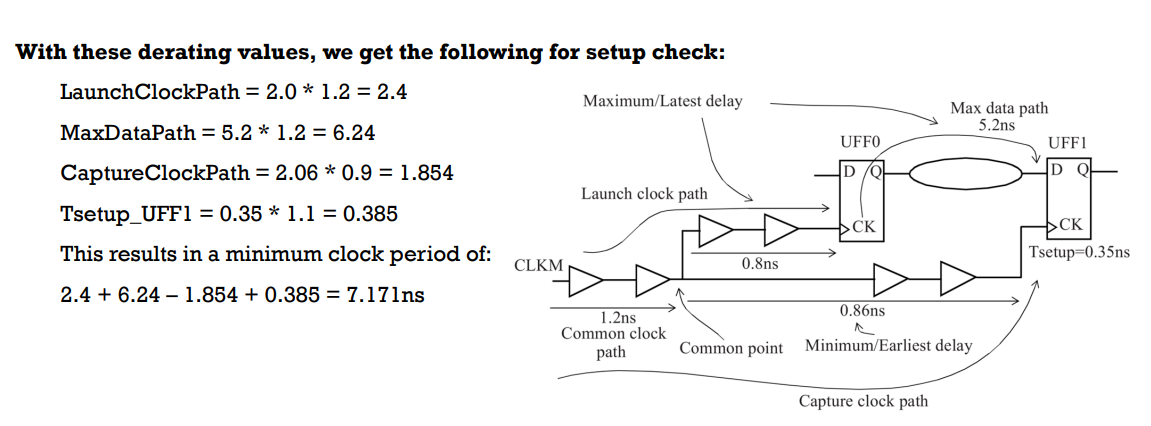

以下以建立時間時序檢查為例子進行說明:

set_timing_derate -early 0.9

set_timing_derate -late 1.2

set_timing_derate -late 1.1 -cell_check

什麼是early?什麼是late?

對於setup Analysis:

- Launch clock: late path

- Data path: late path

- Capture clock: early path

因為 launch clock+Data path 我們都希望為latest(越late OCV越糟糕)

而 capture clock越early越糟糕(越early OCV越糟糕)

對於hold Analysis:

- Launch clock: early path

- Data path: early path

- Capture clock: late path

因為 launch clock+data path 我們都希望越early(越early OCV越糟糕)

而 capture clock 我們都希望為latest(越late OCV越糟糕)

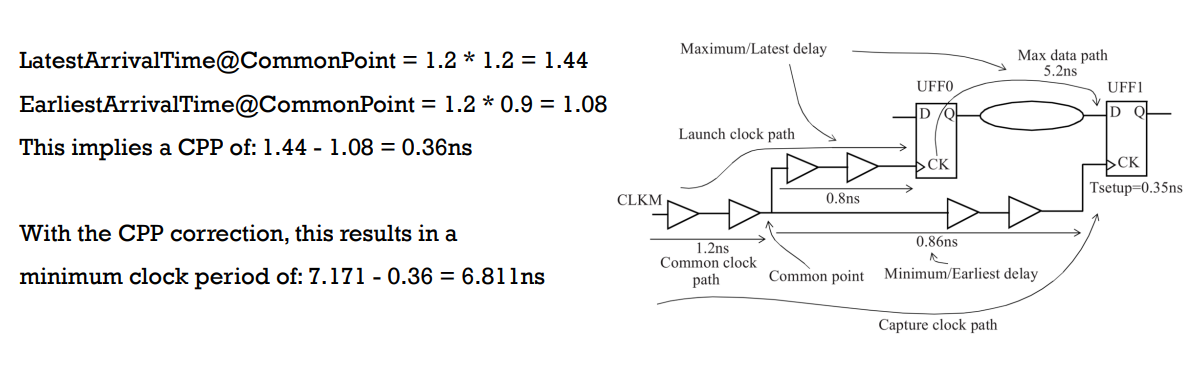

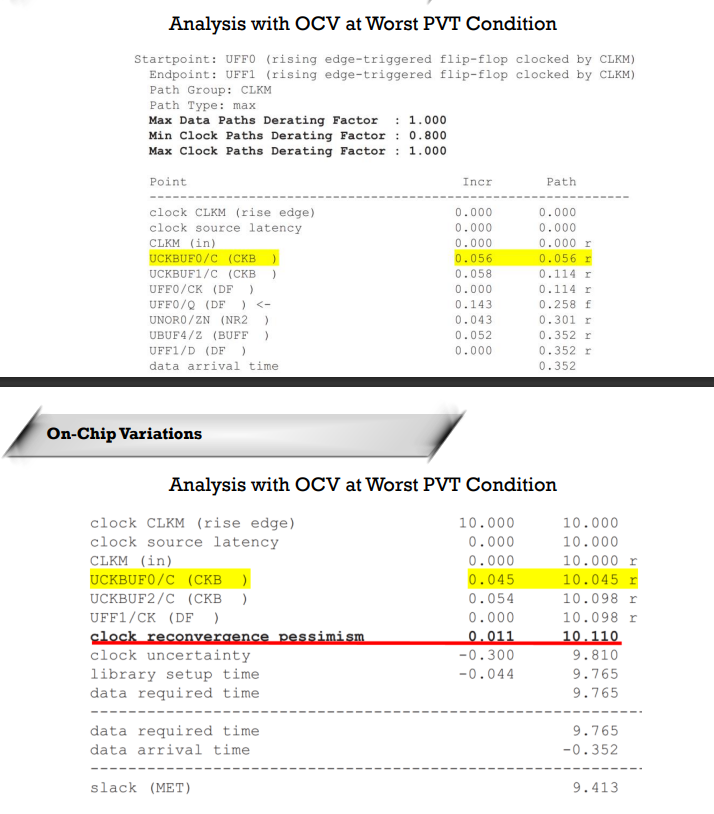

6.1.2 CPPR

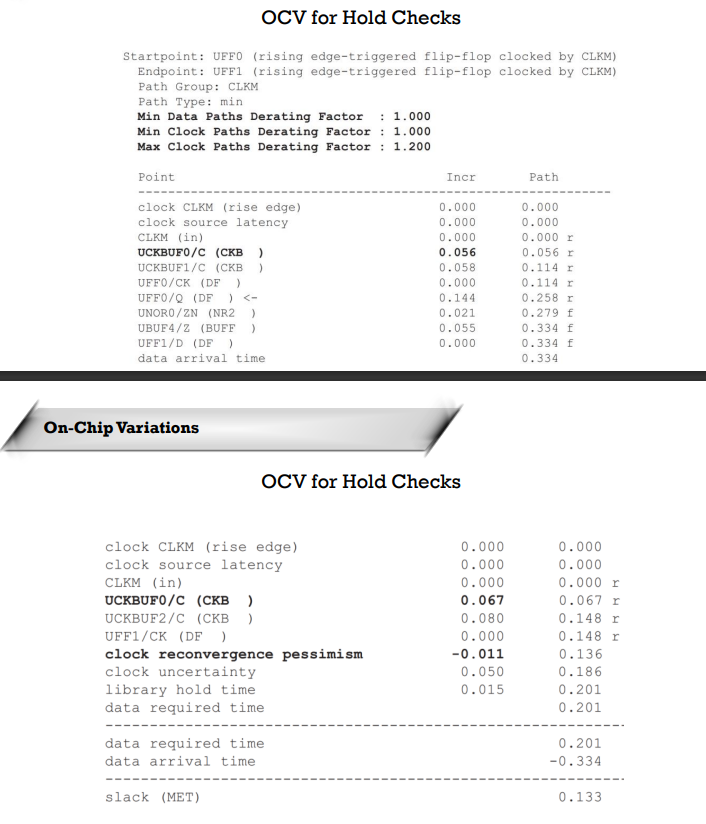

由於對公共路徑進行不同的derate,這明顯是不合規的。CPPR(Common Path Pessimism Removal)表示“公共路徑悲觀度消除”,通常在路徑報告中作為單獨的條目列出。

6.1.3 在最嚴苛的工藝下的建立時間與保持時間時序檢查

1.建立時間時序檢查——最差PVT條件下的OCV分析

如果在最差情況(worst-case)的PVT條件下執行建立時間檢查,則在較晚路徑(late path)上就無需降額了,因為它們已經是最差的情況了。但是,可以通過將特定的降額繫數應用於較早路徑(early path)來使那些路徑更快,例如使較早路徑加速10%。降額約束可能如下所示:

set_timing_derate -early 0.9

set_timing_derate -late 1.0

set_timing_derate -early 0.8 -clock

2.保持時間時序檢查——最佳PVT條件下的OCV分析

通常,保持時間檢查是在最佳情況的快速PVT角下執行的。在這種情況下,較早路徑無需降額,因為這些路徑已經是最快的路徑了。但是,可以通過將特定的降額繫數應用於較晚路徑來使那些路徑更慢,例如使較晚路徑變慢20%。降額約束可能如下所示:

set_timing_derate -early 1.0

set_timing_derate -late 1.2

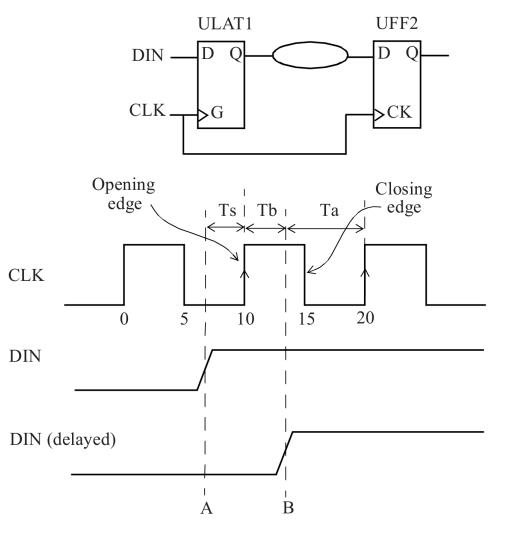

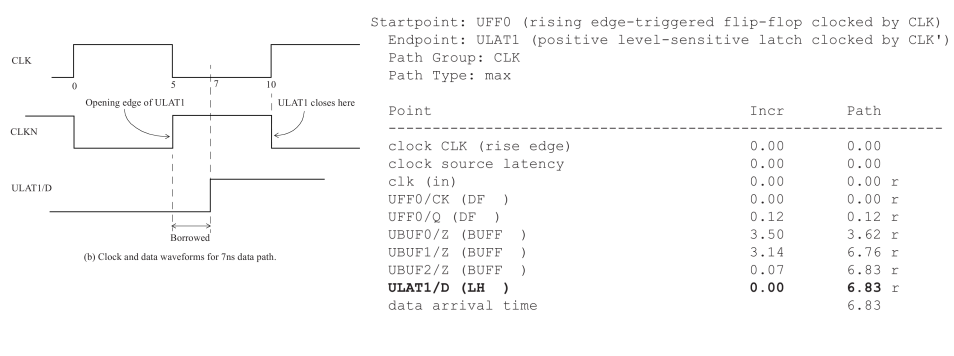

6.2 時間借用(Time Borrowing)

時間借用(Time Borrowing)僅發生在鎖存器中。通常,應在時鐘有效沿之前就在鎖存器輸入處準備好數據。但是,由於鎖存器在時鐘處於有效狀態時是透明的,因此數據可以晚於有效時鐘沿到達,也就是說,它可以從下一個周期借用時間。如果這樣借用了時間,則會減少可用於下一級(鎖存器到另一個時序單元)的時間。如下圖所示:

數據如果在鎖存器有效沿延遲到達,則會減少從鎖存器到下一個觸發器UFF2的可用時間,只有時間Ta可用,而不再是完整的時鐘周期。

鎖存器時序的第一條規則是:如果數據在鎖存器的打開沿之前到達,則寄存器行為將與觸發器完全一樣。在打開沿捕獲數據,而同一時鐘沿又將發起數據,作為下一條時序路徑的起點。

鎖存器時序的第二條規則是:數據在鎖存器為透明狀態時(在打開沿和關閉沿之間)到達。鎖存器的輸出將被用作下一級時序路徑的起點,而不是時鐘引腳。在鎖存器處結束的時序路徑所借用的時間將決定下一級的發起時間。

以下是鎖存器發生time borrowing但沒有時序違例的時序報告:

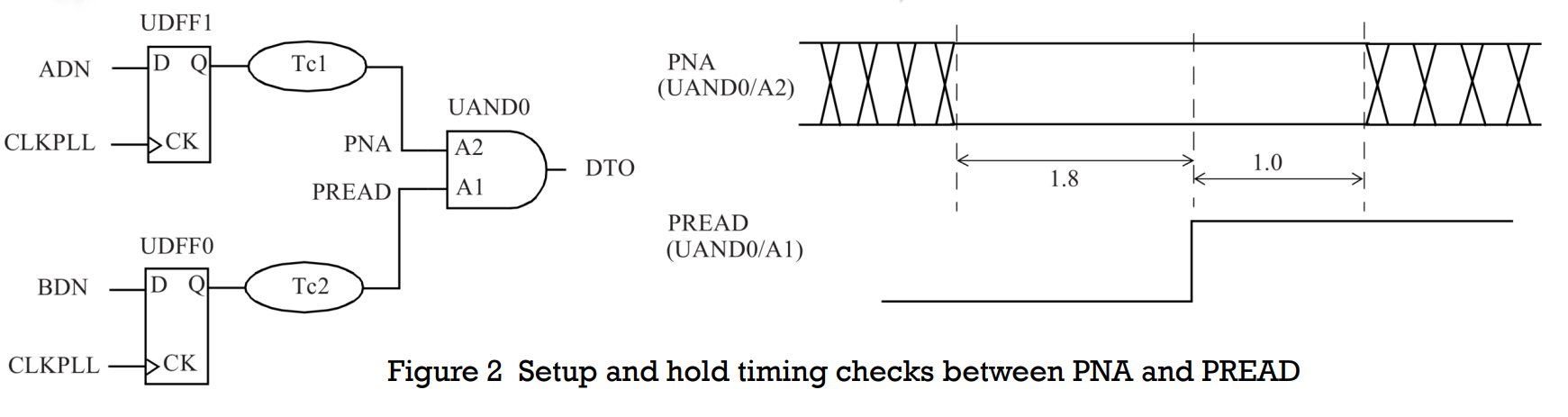

6.3 數據到數據檢查

建立時間和保持時間檢查也可以在任意兩個數據引腳之間進行,這兩個都不是時鐘引腳。關於觸發器建立時間檢查的一個重要區別是,數據到數據的建立時間檢查是在與發起沿相同的沿上執行的(不同於觸發器的常規建立時間檢查,其中捕獲時鐘邊沿通常會距離發起時鐘沿一個周期)。因此,數據到數據的建立時間檢查也稱為零周期檢查(zero-cycle checks)或同周期檢查(same-cycle checks)。

create_clock -name CLKPLL -period 10 -waveform {0 5} [get_ports CLKPLL]

#主時鐘定義

set_data_check -from UAND0/A1 -to UAND0/A2 -setup 1.8

set_data_check -from UAND0/A1 -to UAND0/A2 -hold 1.0

#建立時間與保持時間檢查,建立時間同周期邊沿,保持時間前一個邊沿

set_multicycle_path -1 -hold -to UAND0/A2

#也可以用多周期約束使得保持時間檢查在同一個邊沿

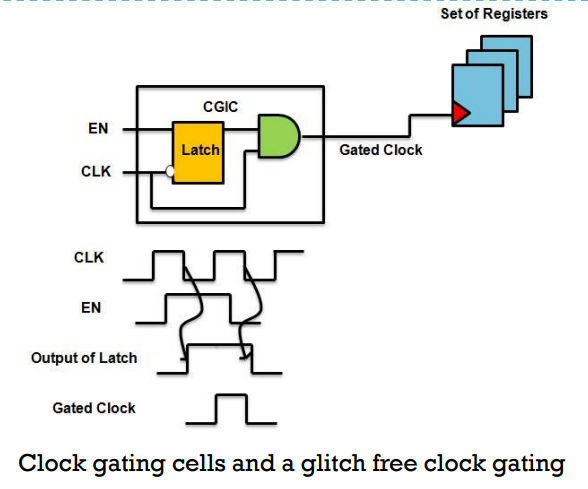

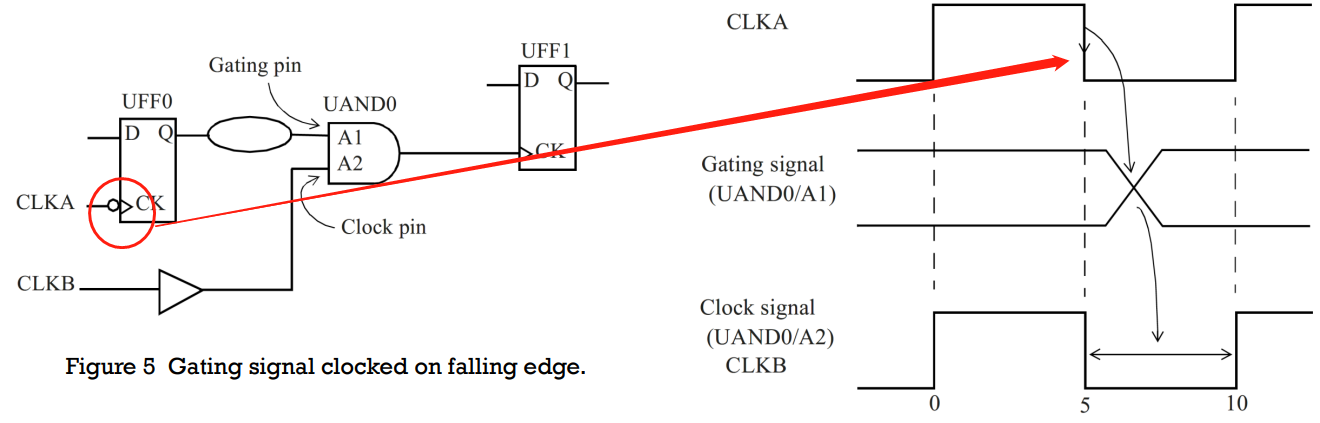

6.4 門控時鐘檢查

瞭解門控時鐘ICG的工作原理,一般由Latch + 與門構成。具體可以細看這篇文章晶元設計進階之路——門控時鐘。

有兩種類型的時鐘門控檢查:

- 高電平有效時鐘門控檢查(Active-high clock gating check):當門控單元具有and 或 nand功能時發生。

- 低電平有效時鐘門控檢查( Active-low clock gating check):當門控單元具有 or或 nor功能時發生。

以高電平有效時鐘門控檢查為例進行說明:

- 由於為高電平有效,CLKA的信號變化必須落在5ns - 10ns。

- 如果觸發器(寄存器)非下邊沿有效,則對於建立時間的時序要求嚴苛(寄存器會有time borrowing)。

- 低電平有效時鐘門控檢查則不需要滿足條件2。

其他幾種門控時鐘不做介紹,因為門控時鐘在工藝庫裡面有現成模塊,重點分析以上ICG模型即可。其餘模型可以查看靜態時序分析聖經翻譯計劃——第十章:魯棒性檢查(中)。

參考資料

強烈推薦去B站過完一遍邸老師的靜態時序分析基礎課

1.B站邸志雄老師的靜態時序分析基礎

2.邸志雄老師主頁

2.Static Timing Analysis for Nanometer Designs: A Practical Approach. J. Bhasker, Rakesh Chadha. Springer Science Business Media, LLC 2009.

3.集成電路靜態時序分析與建模. 劉峰, 機械工業出版社.出版時間:2016-07-01.

4.靜態時序分析聖經中文版翻譯