打算整理彙編語言與介面微機這方面的學習記錄。本部分介紹8086的匯流排。 參考資料 西電《微機原理與系統設計》周佳社 西交《微機原理與介面技術》 課本《彙編語言與介面技術》王讓定 小甲魚《彙編語言》 1. 匯流排定義與分類 講道理這部分學校老師不強調這個,尤其是引腳(說我們記不住),而視頻里老師講得很多 ...

-

打算整理彙編語言與介面微機這方面的學習記錄。本部分介紹8086的匯流排。

-

參考資料

- 西電《微機原理與系統設計》周佳社

- 西交《微機原理與介面技術》

- 課本《彙編語言與介面技術》王讓定

- 小甲魚《彙編語言》

1. 匯流排定義與分類

講道理這部分學校老師不強調這個,尤其是引腳(說我們記不住),而視頻里老師講得很多。

匯流排是電腦系統中傳輸各類信息的公共通道。按照功能層次,有四類:

-

片內匯流排

連接集成電路晶元內部各個功能單元的信息通路。

-

元件級匯流排(板內匯流排)

連接同一個插板內各個元件的匯流排,類似於PCB板上的走線。

-

內匯流排/系統匯流排(版級匯流排)

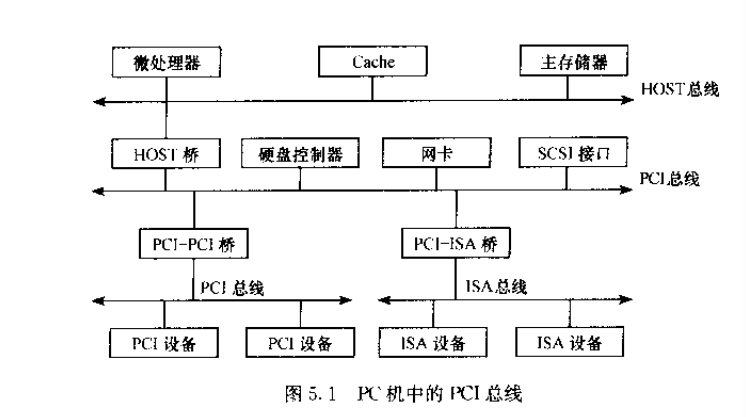

連接各個插件板(微處理之間器、主存儲器、I/O介面)之間的通路。PCI、ISA、STD匯流排就是這一層次。

本章涉及也是這一層次的匯流排。

-

外匯流排/通信匯流排(I/O匯流排)

連接微機主體與I/O設備、儀錶以及其他微機的匯流排。

視頻里老師就講到這裡。課本上後面又講解了幾個系統匯流排,我對PCI比較感興趣,操作系統課程設計也用到了這個匯流排。不過微機角度的PCI主要是結構、時序方面,對編程要求不大。

- 上圖5.1是一個具備PCI匯流排的典型結構,裡面有3個匯流排(HOST PCI ISA)以及3個橋設備

- HOST匯流排也稱存儲匯流排,連接微處理器、Cache、記憶體

- PCI匯流排連接高速I/O介面,因此這些設備也稱為PCI設備

- HOST橋:也叫PCI匯流排控制器,連接HOST和PCI。

- PCI-PCI橋:擴展PCI匯流排。

- PCI-ISA橋:擴展接入標準,符合ISA的設備也可以接入系統。

- 橋設備的用處:

- 地址空間映射

- 數據緩衝,因為PCI匯流排基本是突發事件傳送,沒有緩衝,加上橋設備可以處理時序、流量等更多情況。

- 實現不同層次匯流排的協議和電平轉換。

2. 幾種常用晶元

這塊沒學過,應該電信方面的數電學過,數字邏輯沒有講過。彙編這門課也沒有講(好像),不整理了。總而總之,這幾個晶元是用於匯流排驅動、管理的封裝好的電路。

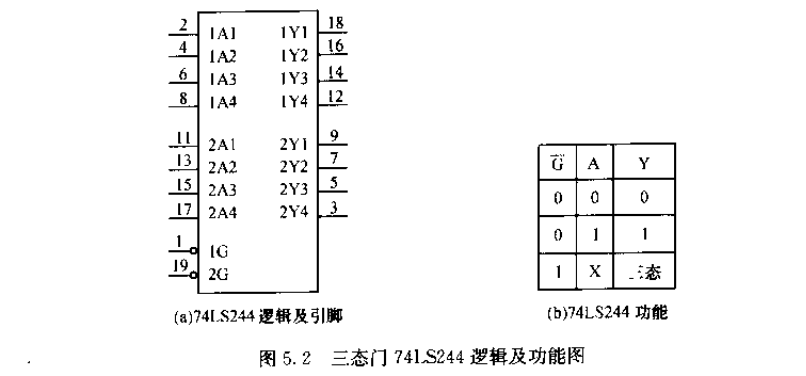

2.1 74LS244

8位數據單向緩衝器。可用作輸入埠的緩衝。

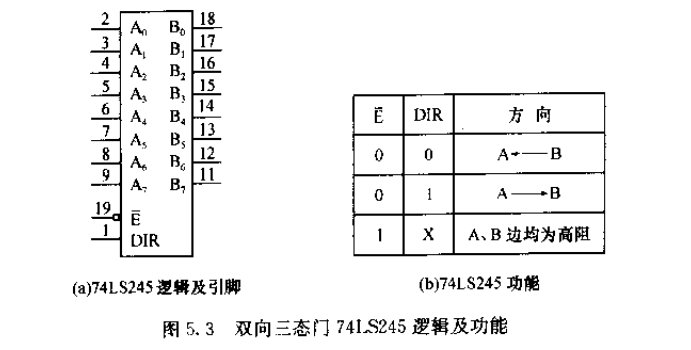

2.2 74LS245

8位數據雙向緩衝器。可以用作匯流排連接的雙向緩衝,也能當做74LS244來用(Dir接地,常0)。工程中也更常使用74LS245。

2.3 74LS373/74LS374

8位鎖存器。常讓OE接地==0。74LS374與之類似,只是G端變為CP時鐘,時鐘上升沿能夠保持數據。

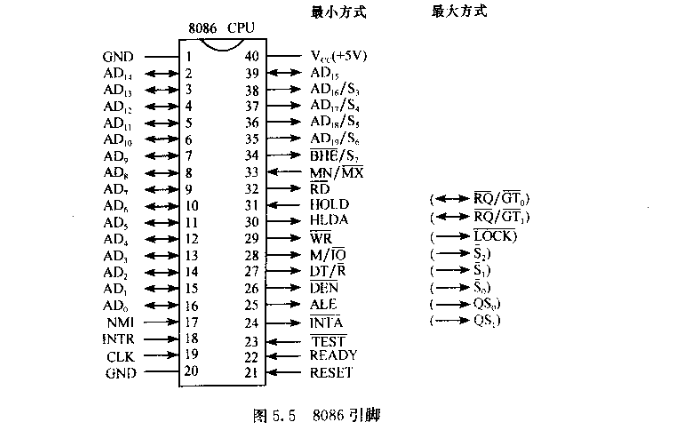

3. 8086引腳功能以及匯流排形成

為什麼又要說引腳呢?引腳就是微處理器級匯流排,微處理器 通過 微處理器級匯流排/引腳 與外面的IO電路連接,組成主機板系統,也就形成了系統級匯流排。

說實話這部分雖然打通數電微機和計組,但是,但這個角度比較難理解。從邏輯設計Verilog角度比較好理解時序,時序是人可以設計出來的,只不過到了8086微機中,Intel規定了一切。

-

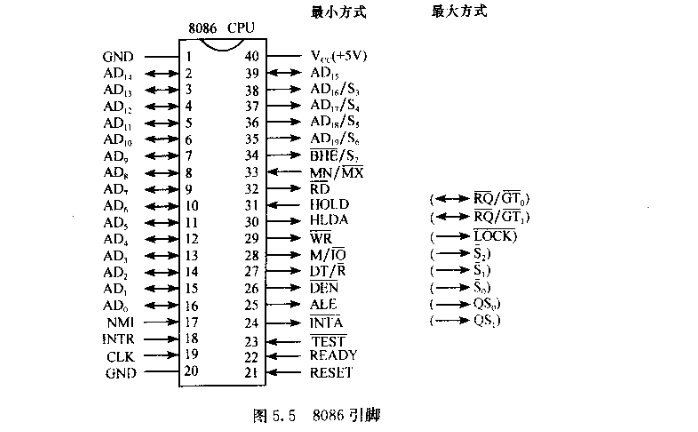

整體上看,8086是40根引腳雙列直插,部分引腳分時復用,有兩種功能。電源電壓為+5V±10%

-

RESET,複位信號,高電平有效。這裡老師講了8254時鐘發生器,使得RESET和時鐘上升沿一起到來(具體實現不關心了)。RESET信號的高電平有效至少要持續4T才能複位。

複位後,DS、ES、SS、IP、PSW、指令隊列寄存器都清0,CS=0FFFFH。所以啟動地址cs:ip是FFFF0H,其他通用寄存器值不確定。

對於FFFF0H,已經在記憶體的很高地址,所以接下來需要遠程跳:

jmp far ptr xxxxh,向低地址跳轉。51單片機的複位中PC寄存器直接置0就沒有這個問題。 -

clk時鐘輸入引腳,8086的工作時鐘<5MHZ。基本的匯流排周期是4個時鐘周期,而非基本匯流排周期則是3個clk+1個等待周期。

-

MN/MX fei:工作模式選擇。加高電平--最小方式;加低電平--最大方式。兩種方式不同的是上圖中24~31腳。

-

最小模式下,CPU對外部存儲器、IO的讀寫等控制信號由CPU直接產生。適合構成單處理器系統。

-

最大模式下,不由CPU直接產生,而由8086CPU外部的匯流排控制器晶元8288產生。CPU通過26、27、28引腳來控制8288,8288來解碼並產生相應控制信號。適合構成多處理器系統。

-

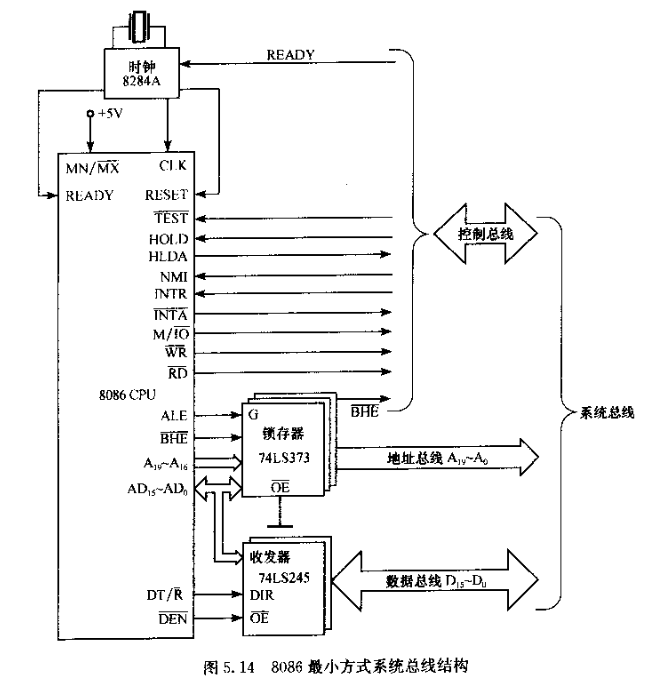

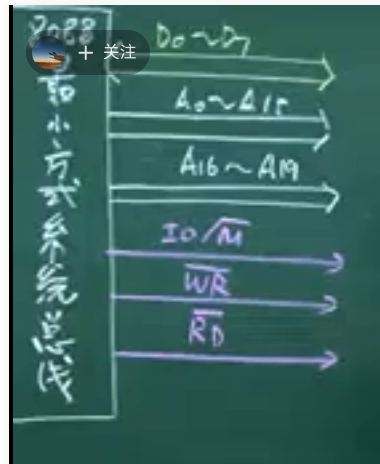

3.1 最小方式(重點)

-

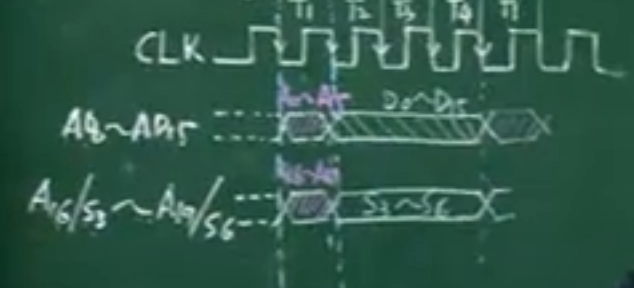

AD0AD15、A16/S3A19/S6:分時復用,地址線和存儲器、IO的數據線;高四位地址線和狀態線。

-

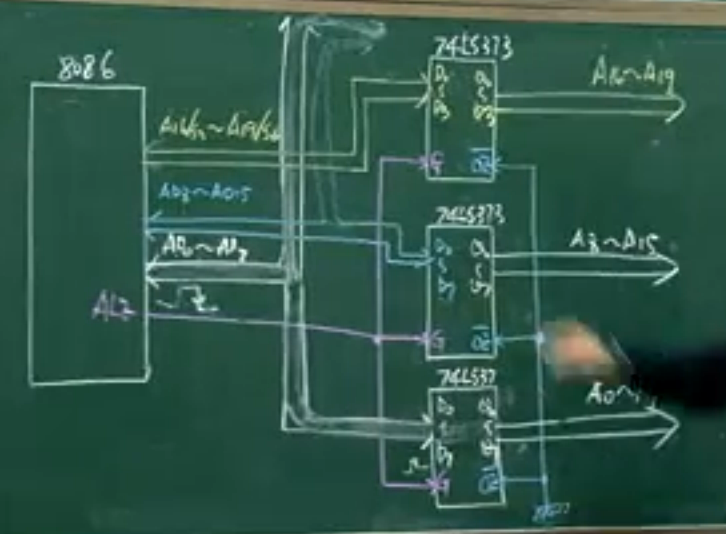

ALE 地址鎖存:在上圖的T1周期內電位變高。變高就知道了上面最重要的T1已經到來。在拿到T1來到的信息後就可以拿到16位地址,可以用74LS373來存儲。

註意,這裡已經開始和5.3節匯流排形成一起講了。

用ALE來作74LS373的G引腳,可以將地址信息鎖存4周期。3片74LS373(匯流排形成電路)輸出的A0~A19就是系統級的匯流排了。

同理,上面介紹的是地址線,數據匯流排與其他控制信號結合(元件級匯流排、微處理器級匯流排),使用74LS245,就能產生數據系統級匯流排。

還有S3~S6。

-

S6沒用

-

S5,狀態寄存器的狀態位IF置1,S5==1。

-

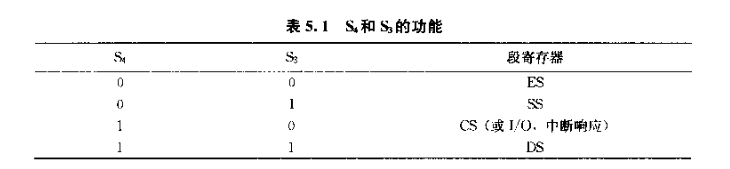

S4和S3反應CPU目前操作使用的是哪個段寄存器。

-

-

DT/(R fei):數據傳輸方向控制信號,CPU向外輸出高電平,向內輸入低電平。

它的時序:比如開始執行

mov [BX],AX,向外輸出,所以T1~T4高電平,之後高或低取決於下一條指令。 -

DEN fei:數據有效信號,數據傳送進出CPU時,該信號低電平。

-

M/(IO fei):高電平為操作存儲器,低電平選擇IO

-

WR fei:數據信號有效後,產生低電平寫信號,併在數據信號有效結束之前,完成寫操作。

存儲器讀是 RD fei

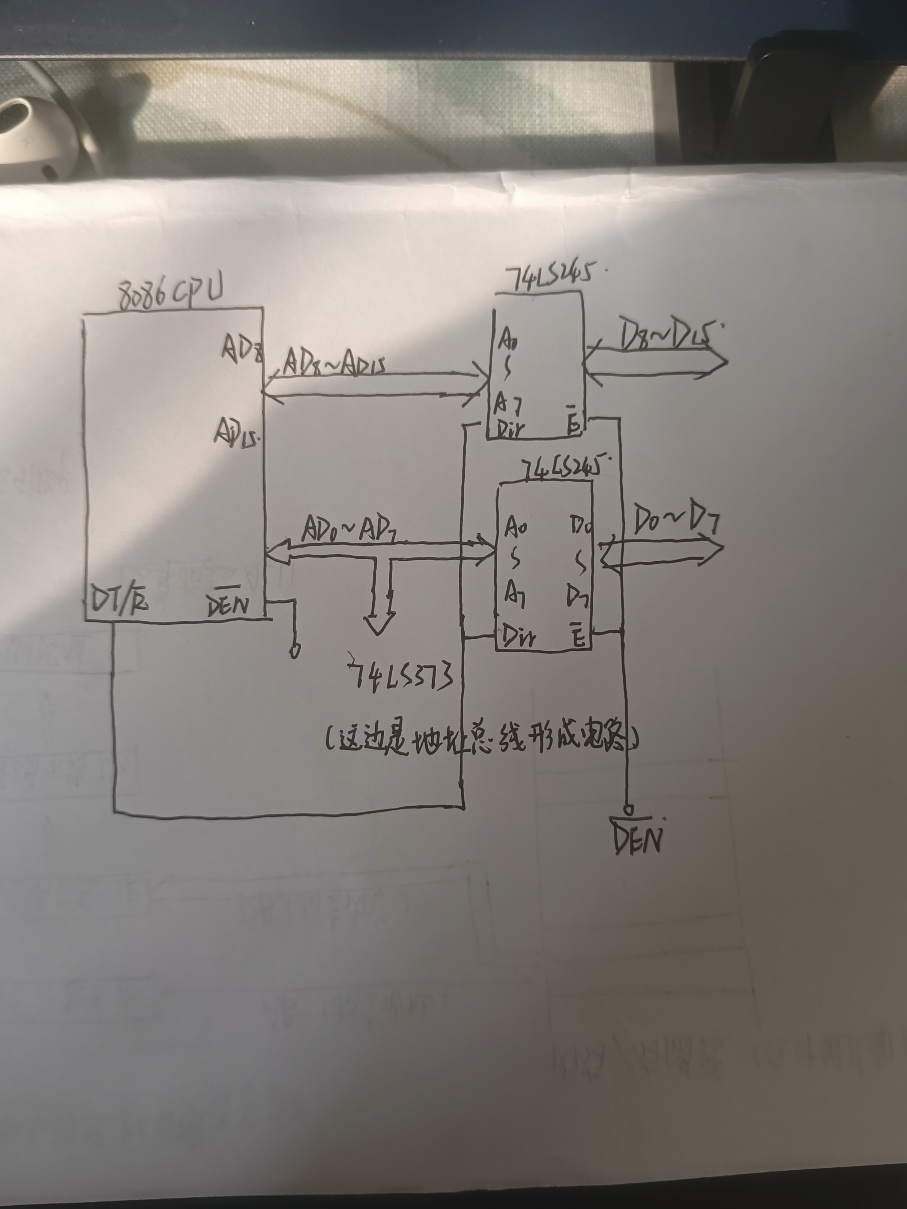

下麵畫8086數據匯流排的形成電路:

-

READY:輸入引腳,上升沿採集,下降沿測試,如果READY為低電平,則CPU就得知設備沒有準備好,在正常匯流排周期的第四個T內進入TW等待周期。實現慢速設備和快速設備之間的同步

READY的下降沿要和CPU時鐘的下降沿同步,設計比較複雜,這個過程會在8284內做,做到同步輸出。

-

TEST fei:測試信號,低電平有效。CPU執行WAIT指令,每隔5個周期對TEST端進行測試,若高電平繼續等待,低電平進入下一條指令。也能達到快慢設備的同步。

-

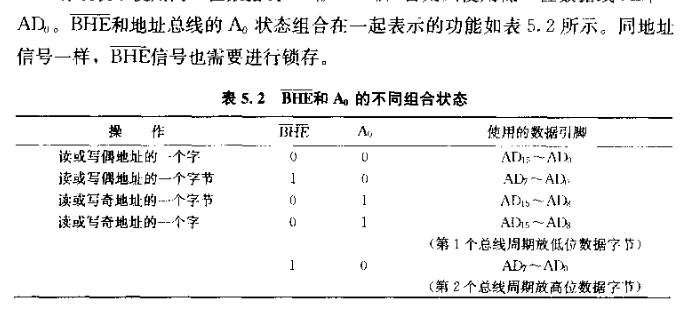

BHEfei/S7:高位元組允許信號。低電平有效。低電平表示使用高8位數據線,高電平低8位數據線。

類似於ALE,註意在上圖5.14中,ALE、BHE也鎖存在74LS373,下圖看看:

補充:8086和8088的區別:

- 內部,指令隊列寄存器8086 6位元組,8088 4位元組

- 外部,8086 20根地址線,8088 16根地址線,最小方式下且8086 M/IOfei,8088 IO/Mfei

-

INTAfei(出,CPU回答是否響應可屏蔽中斷的信號,會連回兩次,第一次回覆可響應中斷,第二次問內容,此後數據線低八位拿數據),INTR(入)和NMI,不提了。

-

HOLD(輸入),其他匯流排主控設備申請信號,高電平有效。

HLDA(輸出),CPU對匯流排使用權的應答,如果讓出匯流排,就高電平,此時CPU的三態引腳全部高阻態,與外界隔離。

控制匯流排的形成。還是參照上圖5.14,相當於直接引出。

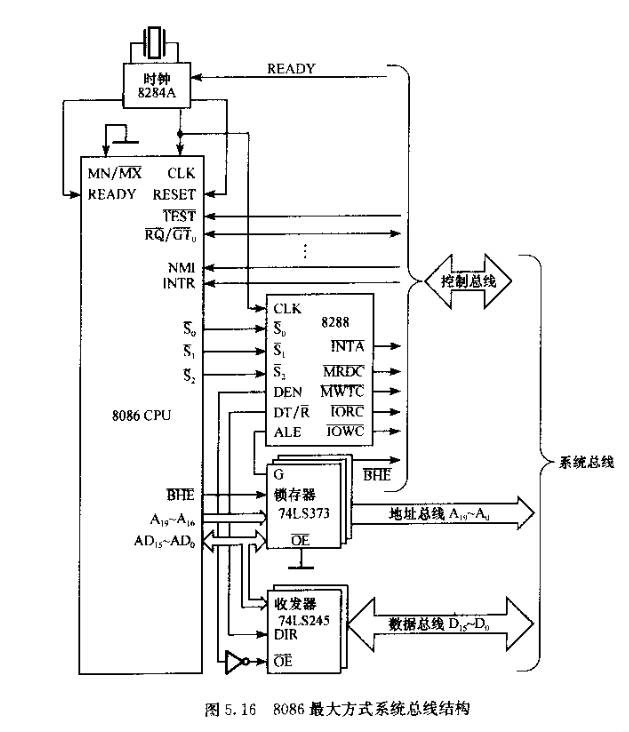

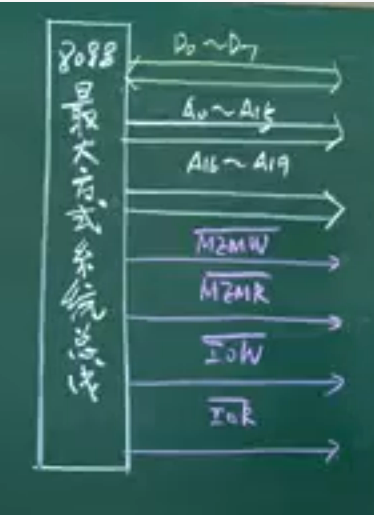

3.2 最大方式

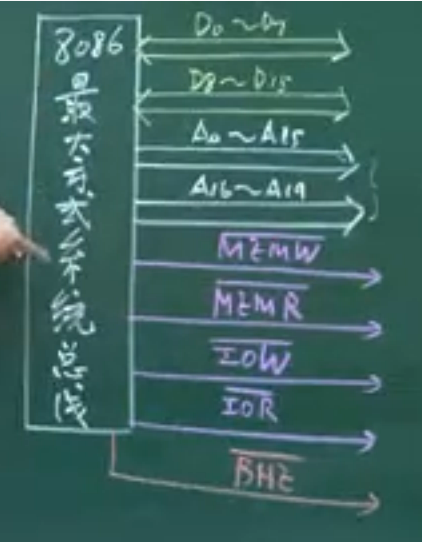

最大方式的匯流排結構如下圖所示,與最小方式引腳功能有一點不一樣,但方法基本一樣:

引腳功能區分有:

-

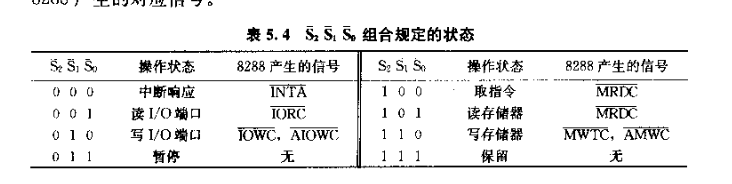

S2 S1 S0,

-

最小模式下,CPU對外部存儲器、IO的讀寫等控制信號由CPU直接產生。適合構成單處理器系統。

-

最大模式下,不由CPU直接產生,而由8086CPU外部的匯流排控制器晶元8288產生。CPU通過26、27、28引腳來控制8288,8288來解碼並產生相應控制信號。適合構成多處理器系統。

-

這裡最大方式的26、27、28就是S2 S1 S0。

見本文3.1之前一段。

-

-

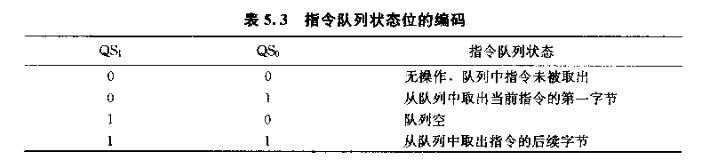

24、25腳:QS1 QS2,表明CPU取指令時的狀態。

-

30、31腳:RQfei/GT1fei,RGfei/GT0fei,等效於HLDA和HOLD。

當處理器以外的匯流排主控設備通過這兩個引腳其中之一向CPU申請匯流排使用權,CPU回覆讓出,當主控設備停止使用讓出匯流排時,再告知CPU自己讓出了匯流排。

31腳的申請優先順序高於30腳。

-

29腳:LOCKfei,如果某條指令,用戶認為非常重要,不允許其他匯流排主控設備向CPU申請匯流排,就在該指令前方加一個<匯流排封鎖首碼指令LOCK>,此時該29引腳就是低電平,通知匯流排主控設備匯流排已經封鎖。

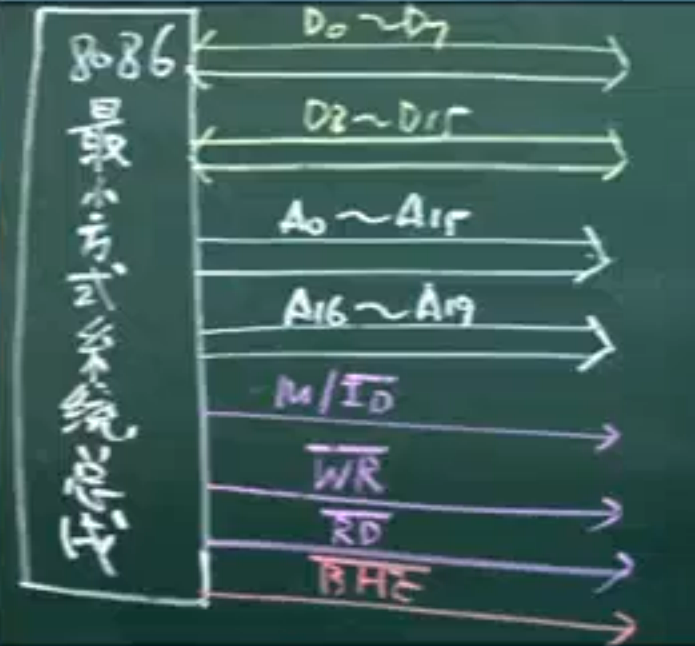

3.3 關於系統級匯流排

註意!之後的存儲器擴展設計和IO擴展設計,都是基於這一章的系統級匯流排進行的。也就是直接展示的三大匯流排,具體分為高八位第八位、最高四位、控制引腳線等。

8086最小方式和8088最大方式都是重點

-

8086最小方式:

-

8086最大方式:

都可以再加上RESET和INTR等。

-

8088最小方式:沒有BHEfei,數據匯流排8位

-

8088最大方式:

3.4 IBM--PC/XT系統

下麵老師講解了IBM--PC/XT系統,使用8088CPU且為多處理器系統(也就是最大模式)。

這個我們老師沒有講,而且年代久遠現在可能也不考了。我只是對PC/XT這個匯流排感興趣,可能對以後深入學習PCI有幫助。

不過講道理,這裡的匯流排,偏向於電路設計,而我想象的匯流排是軟體協議。

這部分先不著急,先考試。

P178,課本。

此外我搜索了一個匯流排提綱:01 微型電腦匯流排 - 最全的介面技術提綱

PC/XT匯流排是將8088 CPU的引腳經過8282鎖存器、8286發送接收器、8288匯流排控制器、8259中斷控制器、8237DMA控制器以及其他邏輯電路的重新驅動和組合控制而形成的。

匯流排信號線共62條

- 8條雙向數據線D7~D0 ;

- 20條單向地址線A19~A0 ;

- 控制線:

- 6條中斷請求線;

- 3對DMA申請線和4條DACK線;

- 4條 存儲器和I/O設備的讀寫命令線;

- 1條系統時鐘信號線、1條I/O奇偶檢測線、1條I/O就緒線及其他聯絡信號線。

- 4種電源(±5V、±12V)共8條線