一、前言 萬物皆有源頭,大家學習單片機的源頭操作就是通過GPIO口點燈,GPIO作為STM32最基礎的外設,也是大家最先接觸的外設。當然,看似基礎的GPIO,不僅僅是簡單的設置好IO口,讓燈亮起就一了百了,瞭解清楚GPIO的使用特性,根本原理、運行機制對我們在涉及到GPIO的相關設計操作上會應用 ...

一、前言

萬物皆有源頭,大家學習單片機的源頭操作就是通過GPIO口點燈,GPIO作為STM32最基礎的外設,也是大家最先接觸的外設。當然,看似基礎的GPIO,不僅僅是簡單的設置好IO口,讓燈亮起就一了百了,瞭解清楚GPIO的使用特性,根本原理、運行機制對我們在涉及到GPIO的相關設計操作上會應用的更加自如。

GPIO就是通用輸入/輸出介面(General-Purpose IO ports),可以配置成輸出模式來控制外部設備,也可以配置成輸入模式來讀取外部信號,是STM32的一種外設,連接晶元外部的引腳,其引腳可以供使用者自由的進行控制。將STM32晶元的GPIO引腳與外部設備連接起來,也可以實現與外部通訊、控制以及數據採集的功能。GPIO最簡單的功能是輸出高低電平;GPIO還可以被設置為輸入功能,用於讀取按鍵等輸入信號;也可以將GPIO復用成晶元上的其他外設的控制引腳。

後續將從以下圖1中所示的幾個方面對GPIO進行詳細的解析。

圖1 GPIO學習框架

二、基本結構概述

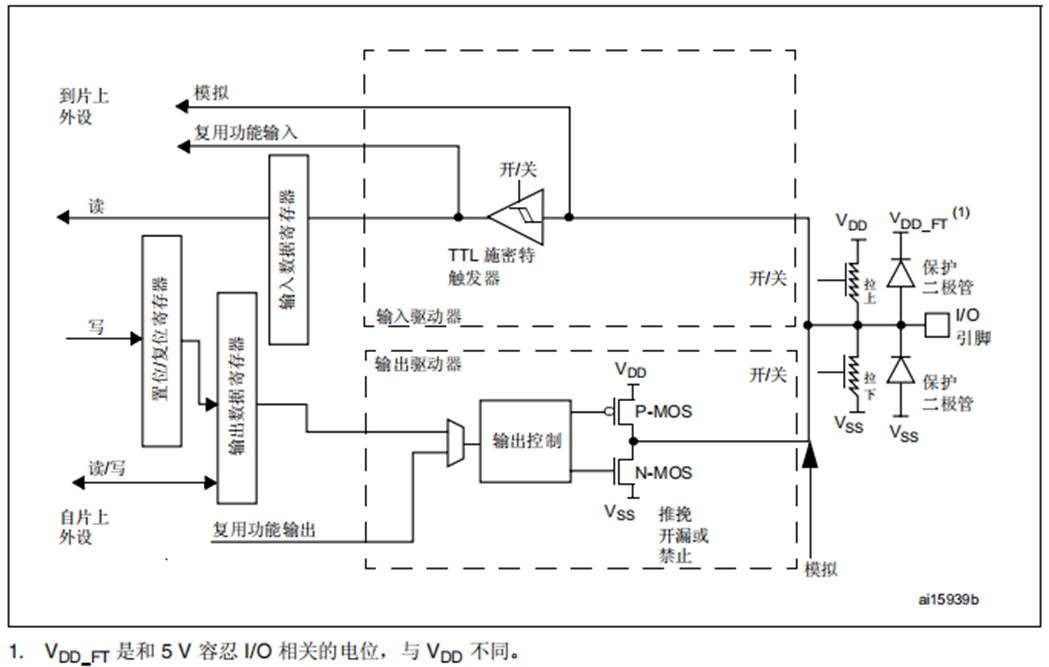

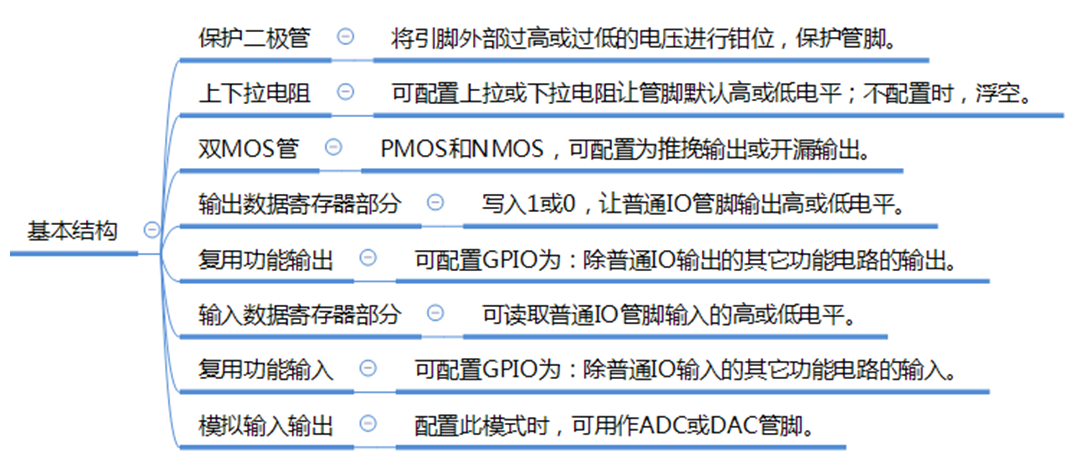

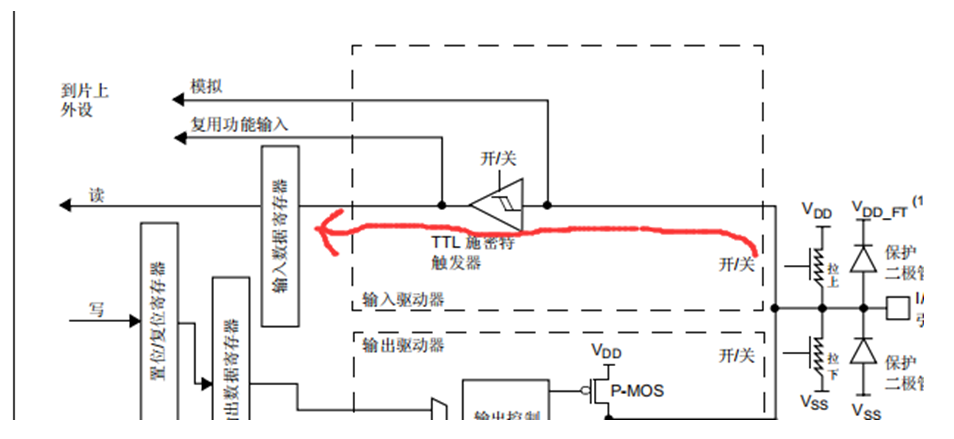

首先對GPIO的基本結構進行詳細分析。瞭解GPIO的基本結構對GPIO的模塊的靜態全貌、運行機理、配置使用有很好的幫助,圖2為STM32的5V容忍的GPIO口內部基本結構圖,圖3為GPIO的基本結構中各個模塊部分的概述。

圖2 STM32的5V容忍的GPIO內部基本結構

圖3 GPIO基本結構包含的功能概述

Q:什麼是5V容忍?

A:在數字電平的規範中,有很多電壓都被設置為邏輯電平,比較典型的有5V,3.3V,2.5V,1.8V,1.2V等等,通常的規律是電路運行的速度越快,使用的邏輯電平電壓越低。

而STM32使用的是3.3V的邏輯電平,各個引腳輸出與輸入的邏輯電平應該是3.3V,ST公司為了增加晶元的相容性,實現了對5V邏輯電平的容忍,意思是可以正常識別5V的邏輯電平信號而不至於因為邏輯電平電壓高於自身的3.3V標準而損壞晶元,這裡的容忍就是正常識別不損壞的意思。

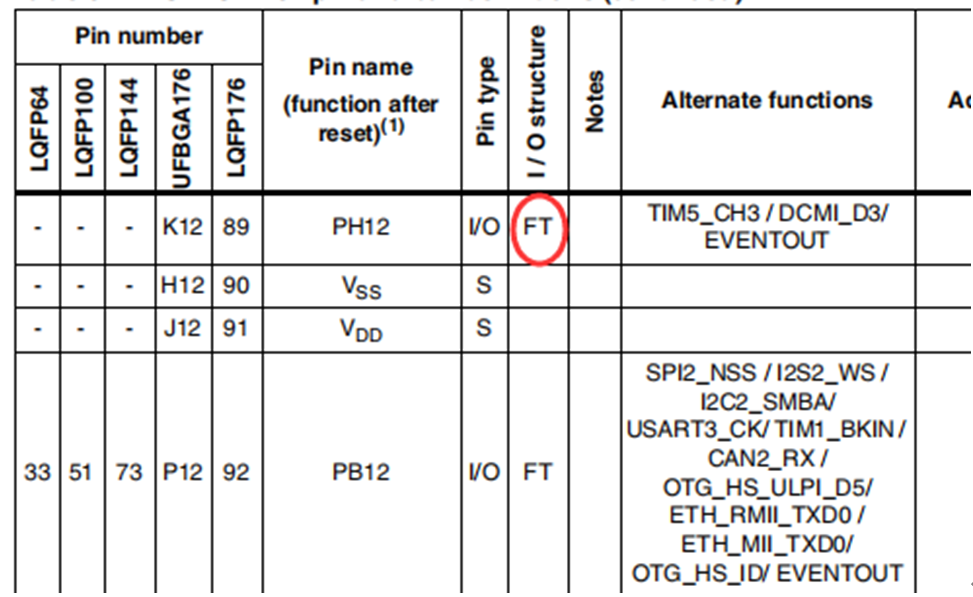

一般而言能夠容忍5V的話都會寫有“FT”兩個字。因此,並不是所有的I/O都是能容忍5V的。註意:如果引腳設置的是模擬輸入模式,則不能接5V!

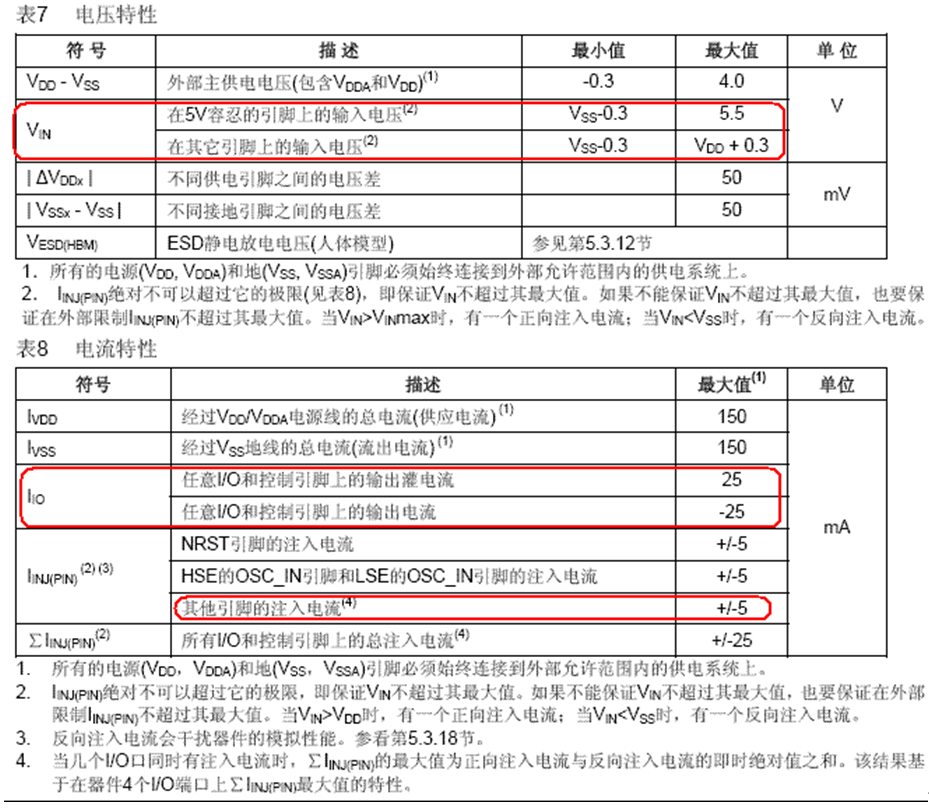

下圖為GPIO引腳電壓特性和電流特性的絕對最大額定值。

圖5 STM32晶元手冊中GPIO的電壓電流特性

加在器件上的電壓或電流如果超過絕對最大額定值,可能會導致器件永久性地損壞。這裡只是給出能承受的最大電壓或電流,並不意味在此條件下器件的功能性操作無誤,器件長期工作在最大值條件下會影響器件的可靠性。

三、基本結構詳述

從圖2中可以看出,從右往左為GPIO在晶元內部的連接通路。各個模塊描述如下:

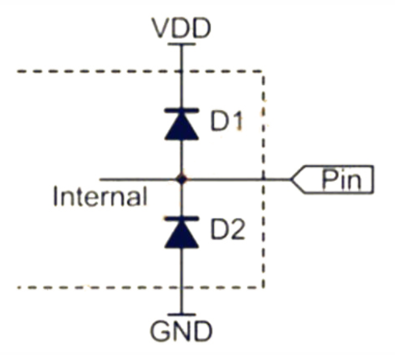

(1)保護二極體

引腳上的這兩個保護二極體可以將引腳外部過高或過低的電壓進行鉗位,當引腳電壓高於VDD_FT 或VDD 時,上方的二極體導通吸收這個高電壓,當引腳電壓低於VSS 時,下方的二極體導通,防止不正常電壓引入晶元導致晶元燒毀。水平的檢測管腳Pin是受保護的節點。當該點電壓超過VDD+VD1(0.7V)時,上面的二極體導通。而當該點電壓小於-VD2(-0.7V)時,下麵的二極體導通。因此,該點電壓被鉗制在VDD+VD1到-VD2間。

儘管STM32 晶元內部有這樣的保護,但並不意味著STM32 的引腳就無所不能,從之前的電流特性表中可知,IO口的電流很小,如果直接將引腳連接大功率器件,比如電機,那麼要麼電機不轉,要麼燒壞晶元。因此若要驅動一些大功率器件,必須要加大功率及隔離電路驅動。也可以說STM32引腳是用來做控制,而不是做驅動使用的。

圖6 鉗位二極體圖(2)上下拉電阻

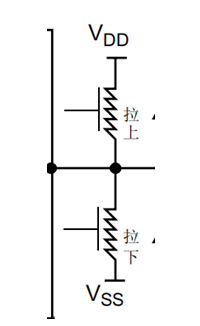

上拉和下拉電阻上都有一個開關,通過配置上下拉電阻開關,可以控制引腳的預設狀態電平。當開啟上拉時引腳預設電壓為高電平,開啟下拉時,引腳預設電壓為低電平,這樣就可以消除引腳不定狀態的影響。當然也可以將上拉和下拉的開關都關斷,這種狀態我們稱為浮空模式,一旦配置成這個模式,引腳的電壓是不確定的,如果用萬用表測量此模式下管腳電壓時會發現只有1 點幾伏,而且還不時改變,所以一般情況下我們都會給引腳設置成上拉或者下拉模式,使它有一個預設狀態。STM32 上下拉及浮空模式的配置是通過GPIOx_CRL 和GPIOx_CRH 寄存器控制的。STM32 內部的上拉其實是一個弱上拉,也就是說通過此上拉電阻輸出的電流很小,如果想要輸出一個大電流,那麼就需要外接上拉電阻了。

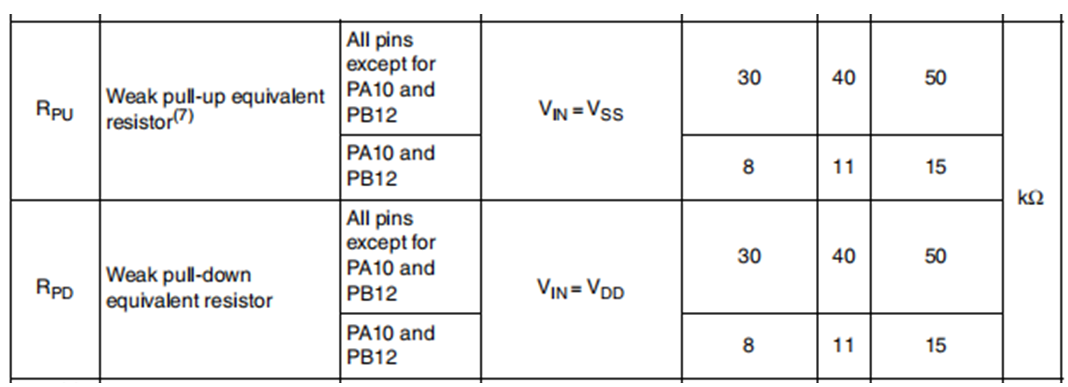

圖7 上下拉電阻圖下圖可以知曉STM32晶元的GPIO口上下拉電阻的最小值,典型值和最大值。

圖8 STM32晶元手冊給定的GPIO上下拉電阻值(3)P-MOS 和N-MOS 管

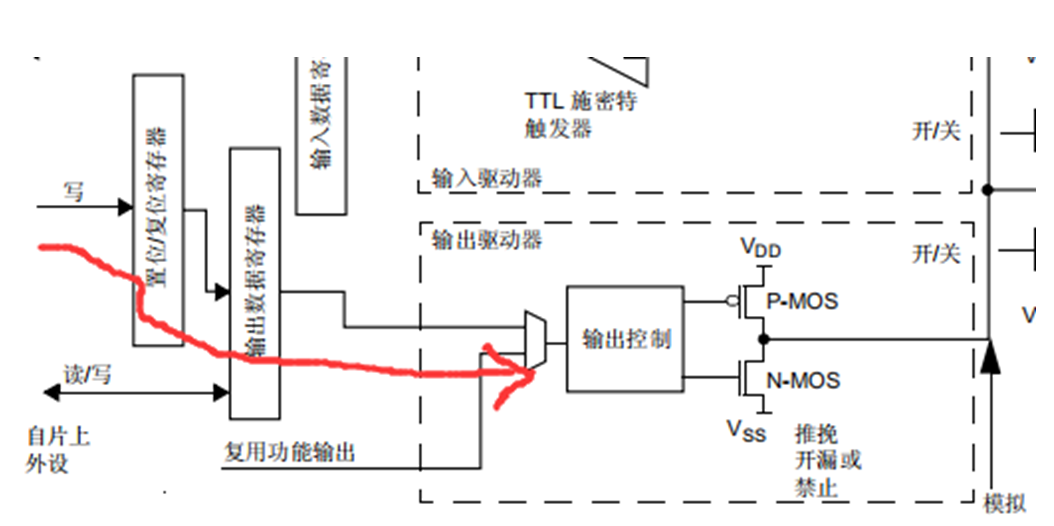

圖2中GPIO 引腳經過兩個保護二極體後就分成兩路,上面一路是經過輸入驅動器為“輸入模式”,下麵一路經過輸出驅動器為“輸出模式”。

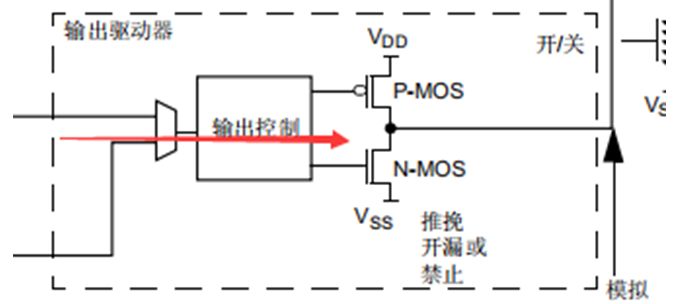

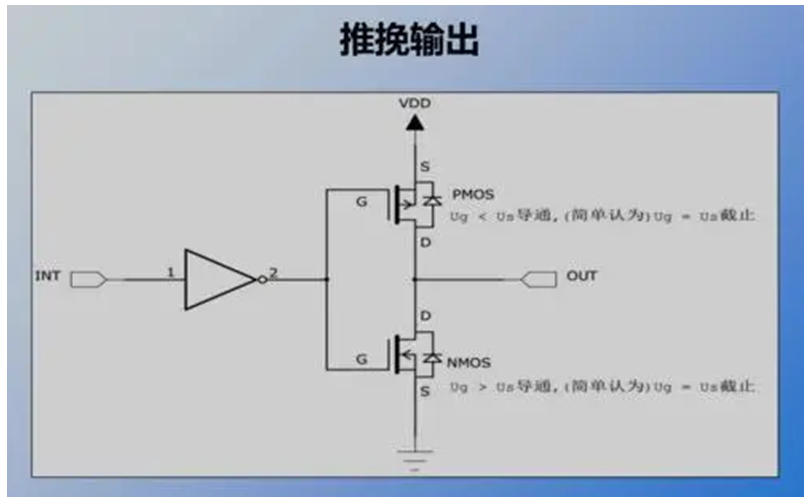

當為輸出模式時,線路經過輸出控制緩衝器到一個由P-MOS 和N-MOS管組成的雙MOS電路,因此GPIO 引腳可以配置成推輓和開漏兩種輸出模式。

圖9 雙MOS電路圖推輓輸出模式,是根據P-MOS 和N-MOS 管的工作方式命名的。在該結構單元輸入一個高電平時,P-MOS 管導通,N-MOS 管截止(可以將P-MOS 看作NPN三極體,N-MOS看作PNP 三極體),對外輸出高電平(3.3V)。在該單元輸入一個低電平時,P-MOS 管截止,N-MOS 管導通,對外輸出低電平(0V)。如果當切換輸入高低電平時,兩個MOS 管將輪流導通,一個負責灌電流(電流輸出到負載),一個負責拉電流(負載電流流向晶元),使其負載能力和開關速度都比普通的方式有很大的提高。

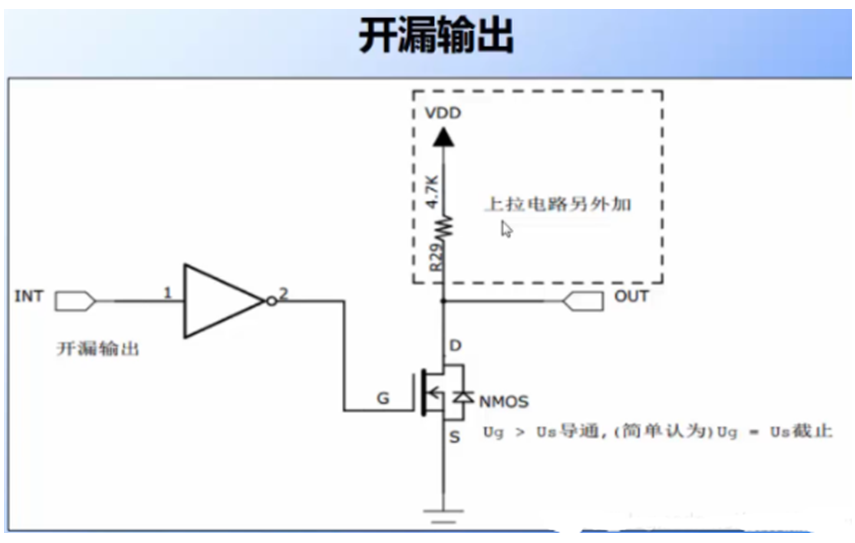

圖10 推輓輸出開漏輸出模式時,不論輸入是高電平還是低電平,P-MOS 管總處於關閉狀態。當給這個單元電路輸入低電平時,N-MOS 管導通,輸出即為低電平。當輸入高電平時,N-MOS 管截止,這個時候引腳狀態既不是高電平,又不是低電平,我們稱之為高阻態。如果想讓引腳輸出高電平,那麼引腳必須外接一個上拉電阻,由上拉電阻提供高電平。開漏輸出模式等效電路圖如圖所示。

圖11 開漏輸出在開漏輸出模式中還有一個特點,引腳具有“線與”關係。就是說如果有很多個開漏輸出模式的引腳接在一起,只要有一個引腳為低電平,其他所有管腳都為低,即把所有引腳連接在一起的這條匯流排拉低了。只有當所有引腳輸出高阻態時這條匯流排的電平才由上拉電阻的VDD 決定。如果VDD 連接的是3.3V,那麼引腳輸出的就是3.3V,如果VDD 連接的是5V,那麼引腳輸出的就是5V。因此如果想要讓STM32 管腳輸出5V,可以選擇開漏輸出模式,然後在外接上拉電阻的電源VDD 上連接5V 即可,前提是這個STM32引腳是容忍5V的。

開漏輸出模式一般應用在I2C、SMBUS 通訊等需要“線與”功能的匯流排電路中。還可以用在電平不匹配的場合中,就如上面說的輸出5V 一樣。推輓輸出模式一般應用在輸出電平為0-3.3V 而且需要高速切換開關狀態的場合。除了必須要用開漏輸出模式的場合,我們一般選擇推輓輸出模式。要配置引腳是開漏輸出還是推輓輸出模式可以使用GPIOx_CRL 和GPIOx_CRH 寄存器。

(4)輸出數據寄存器

前面提到的雙MOS 管結構電路的輸入信號,由GPIO“輸出數據寄存器GPIOx_ODR”提供,因此通過修改圖12中輸出數據寄存器的值就可以修改GPIO 引腳的輸出電平,同時“輸出數據寄存器GPIOx_ODR”的數值狀態也是可讀的。

而如果需要對輸出電平信號進行原子操作,可以通過圖12中“置位/複位寄存器GPIOx_BSRR”修改輸出數據寄存器的值從而改變GPIO的輸出。該寄存器是只寫寄存器,通過寫入 “置位/複位寄存器GPIOx_BSRR”狀態,可分別對 “輸出數據寄存器GPIOx_ODR” 進行置位和複位。

剛開始或許你跟我一樣有以下疑惑:既然ODR 能控制管腳高低電平,為什麼還需要BSRR寄存器?

意法半導體給的答案就是用BSRR去改變管腳狀態的時候是原子操作置位/複位,沒有被中斷打斷的風險。也就不需要關閉中斷,關閉中斷明顯會延遲或丟失一事件的捕獲,所以控制GPIO的狀態最好可以用BSRR。

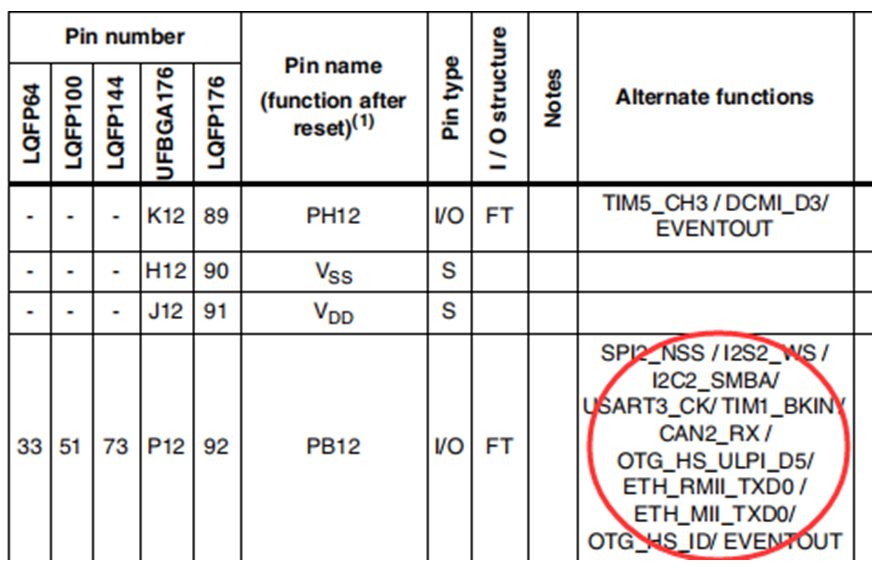

(5)復用功能輸出

STM32 的GPIO 引腳不僅僅可以用作普通IO輸出電平進行控制,還可以用作晶元上其他外設的復用功能引腳。因此當使用復用功能的時候,也就是其他外設復用功能輸出信號將直接經過圖12中輸出控制緩衝器後,作為雙MOS 管電路的輸入,其中信號在進入輸出控制緩衝器之前,需要選擇使用復用功能還是普通IO 口功能。例如,我們使用USART 串口通訊時,需要用到某個GPIO 引腳作為通訊發送引腳,這個時候就可以把該GPIO 引腳配置成USART 串口復用功能,由晶元上的串口外設控制該引腳,發送數據。具體使用的GPIO口具備哪些復用功能,可以查閱具體的晶元手冊得到。

圖13 STM32晶元手冊中GPIO復用功能定義(6)輸入數據寄存器

輸入數據寄存器是由IO口經過上下拉電阻、TTL施密特觸發器引入。當信號經過TTL施密特觸發器,模擬信號將變為數字信號0 或1,然後存儲在輸入數據寄存器中,通過讀取“輸入數據寄存器GPIOx_IDR” 就可以知道IO 口的電平狀態。

施密特觸發器:簡單來說,就是當輸入電壓高於正向閾值電壓,輸出為高;當輸入電壓低於負向閾值電壓,輸出為低;當輸入在正負向閾值電壓之間,輸出不改變。因此只有當輸入電壓發生足夠的變化時,輸出才會變化,因此將這種元件命名為觸發器。這種雙閾值動作被稱為遲滯現象,表明施密特觸發器有記憶性。從本質上來說,施密特觸發器是一種雙穩態多諧振蕩器。

施密特觸發器可作為波形整形電路,能將模擬信號波形整形為數字電路能夠處理的方波波形,而且由於施密特觸發器具有滯回特性,所以可用於抗干擾。

圖14 輸入數據寄存器部分圖(7)復用功能輸入

復用功能輸入和復用功能輸出類似。在復用功能輸入模式時,GPIO 引腳的信號傳輸到STM32晶元上 其它外設,由該外設讀取引腳的狀態。同樣,如我們使用USART 串口通訊時,需要用到某個GPIO 引腳作為通訊接收引腳,這個時候就可以把該GPIO 引腳配置成USART 串口復用功能,使USART 可以通過該通訊引腳的接收外部通信線上的數據。

(8)模擬輸入輸出

當GPIO 引腳用於ADC 採集電壓的輸入通道時,用作“模擬輸入”功能,如圖14所示,此時信號是不經過施密特觸發器的,因為經過施密特觸發器後信號只有0或1 兩種狀態,ADC 外設要採集到原始的模擬信號,信號源輸入必須在施密特觸發器之前。類似地,當GPIO 引腳用於DAC 作為模擬電壓輸出通道時,此時作為“模擬輸出”功能,如圖12所示,DAC 的模擬信號輸出就不經過雙MOS 管結構了,模擬信號直接通過管腳輸出。

四、總結

以上針對STM32晶元的GPIO基本結構中各個模塊的原理和作用分別進行了介紹,可以對GPIO的靜態全貌有一個初步的瞭解,在下一篇將繼續介紹GPIO基礎知識篇之工作模式。

更多技術內容和書籍資料獲取,入群技術交流敬請關註公眾號“明解嵌入式”

本文來自博客園,作者:Sharemaker,轉載請註明原文鏈接:https://www.cnblogs.com/Sharemaker/p/17107060.html