APB匯流排信號: APB匯流排狀態機與讀寫Timing IDIE是初始化態; SETUP是從機被PSELx選中以後進入的狀態,只維持一個cycle,下一個周期的上升沿到ENABLE態; ENABLE要使PENABLE HIGH,同時如果沒有繼續transfer那麼從ENABLE跳到IDIE,如果有繼續 ...

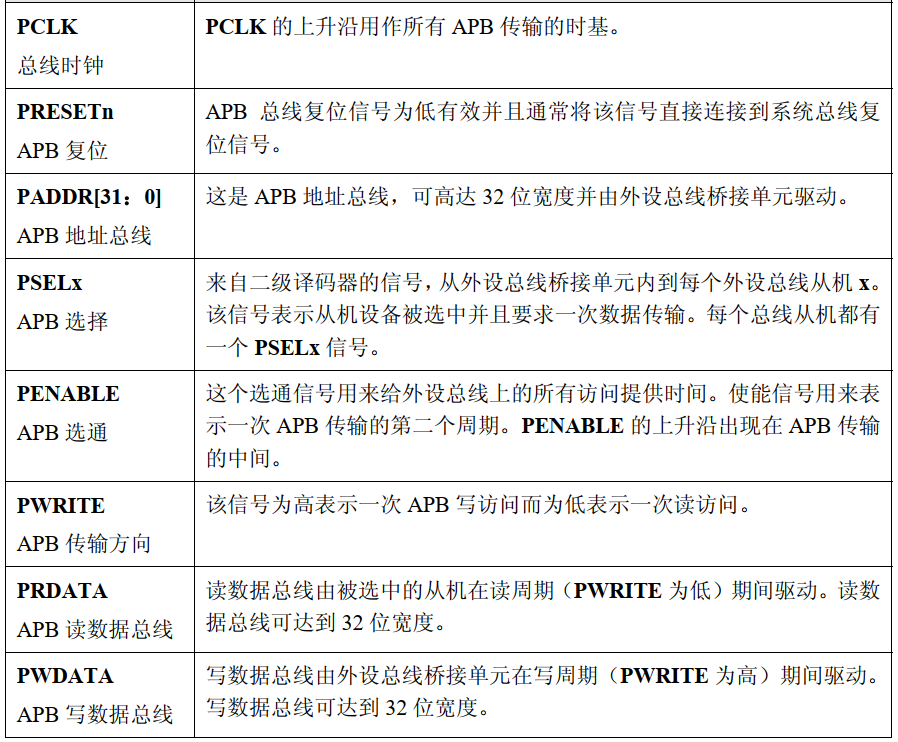

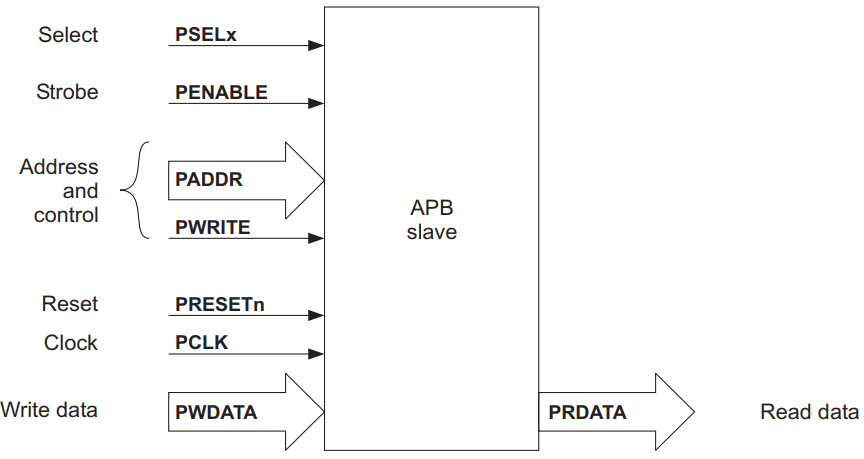

APB匯流排信號:

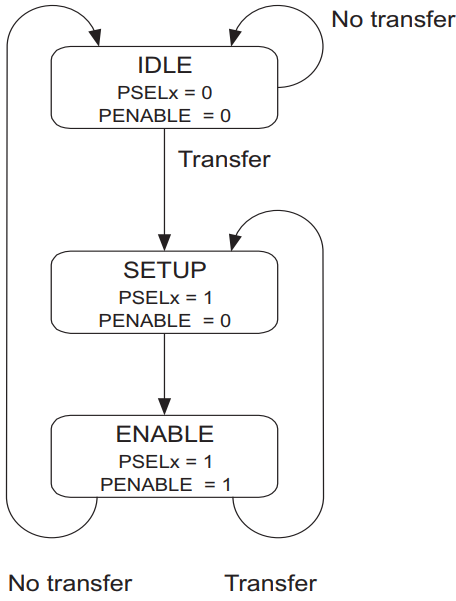

APB匯流排狀態機與讀寫Timing

- IDIE是初始化態;

- SETUP是從機被PSELx選中以後進入的狀態,只維持一個cycle,下一個周期的上升沿到ENABLE態;

- ENABLE要使PENABLE HIGH,同時如果沒有繼續transfer那麼從ENABLE跳到IDIE,如果有繼續transfer從ENABLE跳到SETUP(有點glitch可以接受);從SETUP到ENABLE調整期間所有信號(地址數據控制)都要保持穩定

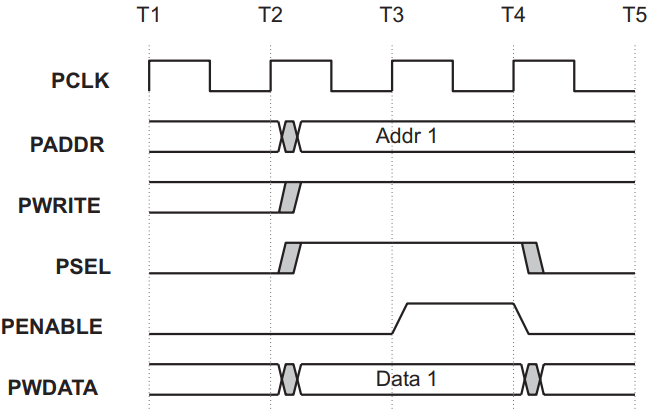

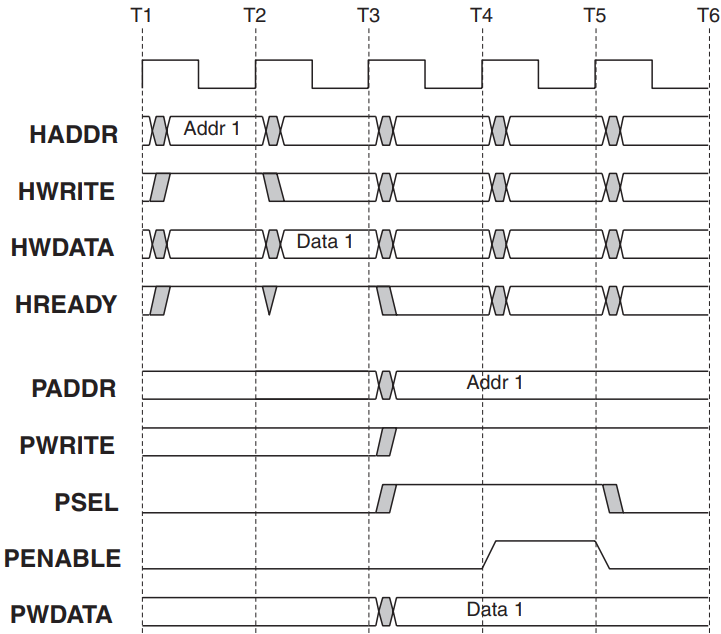

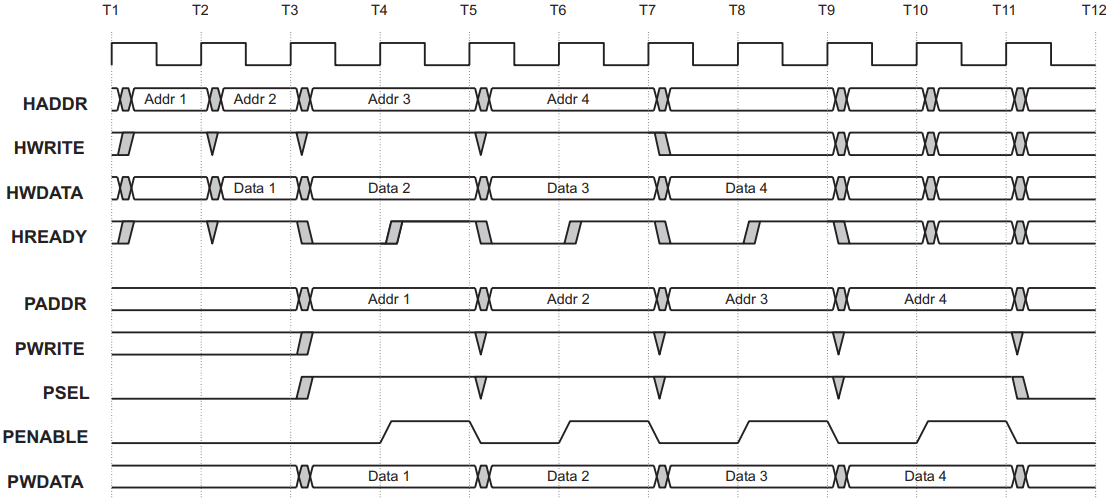

寫

寫

2個cycle進行一次transfer的timing;為了減低功耗,transfer結束後不會改變地址數據信號,除非下一次transfer開始。這實際上只要求clean PSELx信號(transfer結束回到LOW),但背靠背(back to back,讀寫交替的)傳輸中,PWRITE和PSEL可能會有glitch。

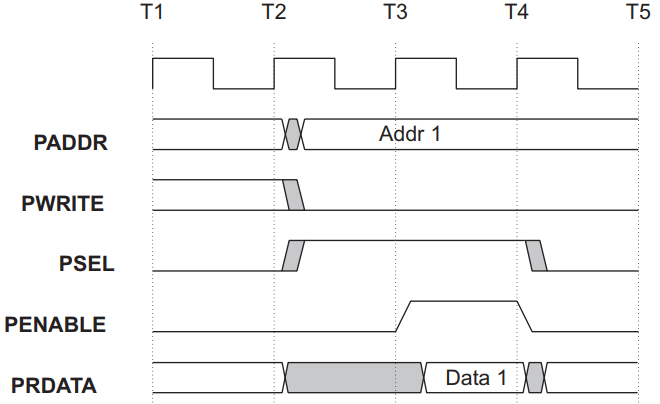

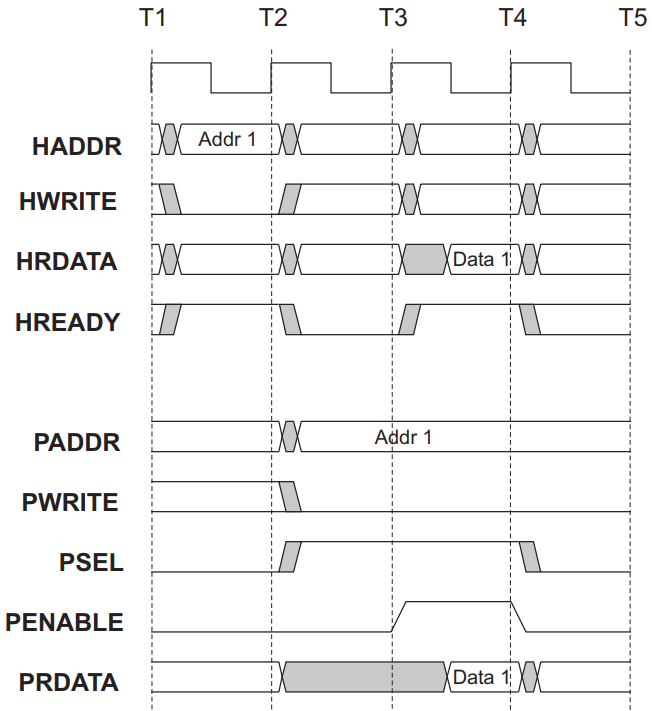

讀

讀

APB從機讀取timing和寫基本一致,地址和PSEL,PENABLE無差異。PWRITE LOW表示讀,並且從機要在ENABLE狀態保持有效的PRDATA,該數據在ENABLE state的上升沿被採樣。

APB bridge

APB橋是APB架構中唯一的主機,同時APB也是AHB或ASB匯流排中的從機。

APB從機

從機WDATA可以在PSELx HIGH的時候,在1 PCLK的上升沿 或 PENABLE的上升沿被 latched。

從機RDATA要在PWRITE LOW並且PSELx 和 PENABLE 都HIGH時輸出。

APB到AHB

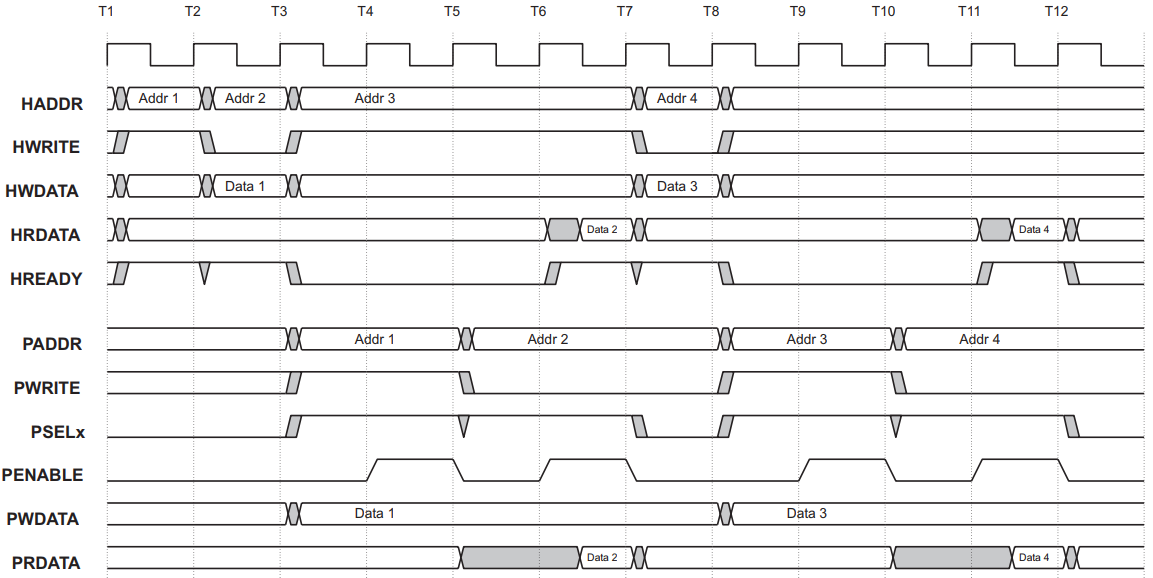

讀

主機發起對APB從機的讀,T1時候AHB主機輸出了有效address;APB bridge採樣到address在T2上升沿,同時立即進行解碼decoding, 生成了PSELx選擇信號置為HIGH,PSELx對應的APB從機進入SETUP state;在下一個周期ENABLE state時APB從機必須提供有效的RDATA。而APB的RDATA通常直接給AHB匯流排;在ENABLE state時,在T4上升沿AHB採樣到RDATA。一次讀transfer完成。

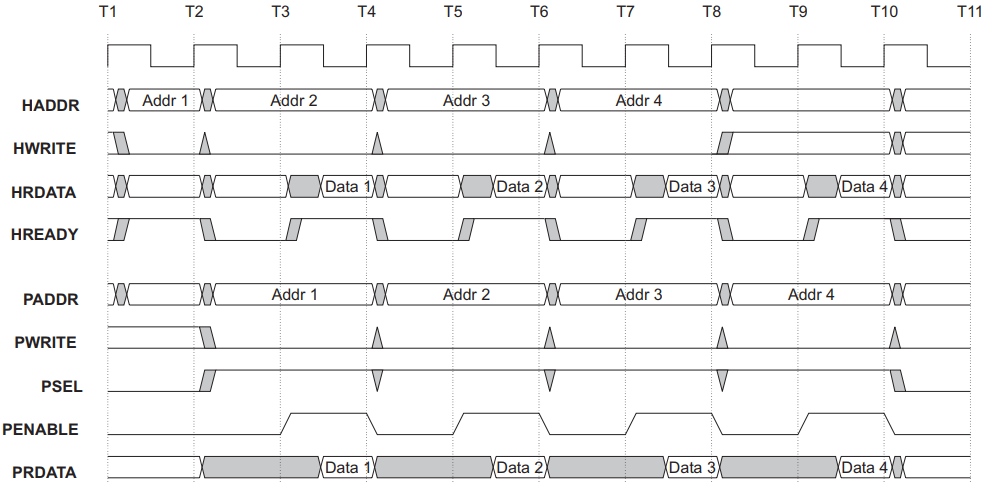

burst read

burst read

AHB對APB從機進行高頻讀取操作。一旦接受到RDATA,AHB HREADY為HIGH就進行下一個data的address更新,APB bridge開始新的一個APB從機的讀取操作。這樣在高頻操作中同樣是2個cycle完成一次讀取,APB bridge(作為AHB的從機)因此需要在第1個cycle置HREADT為LOW(插入1個 wait state),下1個cycle接受RDATA置HREADY為HIGH;但提高了AHB的工作頻率。

寫

APB bridge要採樣AHB主機輸出的HWDATA(還有地址,以及解碼生成PSELx),並且保持給APB從機2個cycle。

在burst write中,只有AHB的第一個寫transfer是zero-wait state,由於APB匯流排需要2個cycle進行操作,因此burst中除了第一個transfer後續每個WDATA都要插入1個wait state。APB bridge必須要有2個address reg,確保在採樣更新AHB主機address的時候,同時也能把之前的address保持給APB從機。

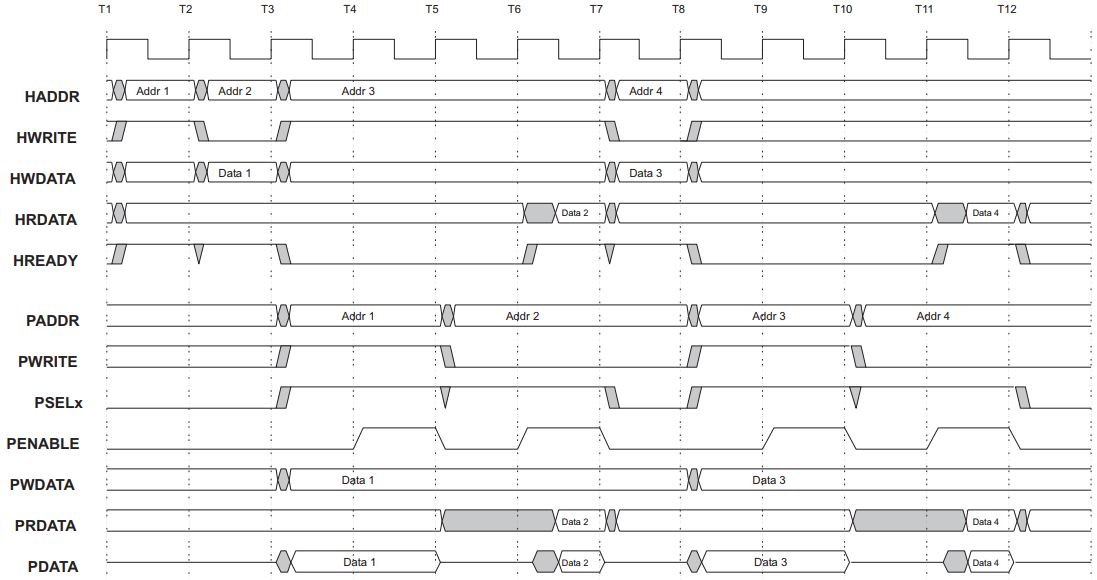

back to back 傳輸,讀寫交替的

在T7-T8,顯然APB匯流排進入了IDIE state(但實際上我認為可以到setup,開始Addr3 的APB寫操作)

三態實現

APB匯流排推薦進行讀寫通道分離的機制。但允許通過三態合併讀寫為1路數據通道。

在APB匯流排以三態實現時,進行讀操作中:,SETUP state和IDIE state要有一個整個cycle的turnaround。圖中T5-6,T7-8,T10-11分別是APB的讀取SETUP,IDIE,讀取SETUP,PDATA都出現了turnaround。