普通的存儲器器件為單埠,也就是數據的輸入輸出只利用一個埠,設計了兩個輸入輸出埠的就是雙埠sram。雖然還具有擴展系列的4埠sram,但雙埠sram已經非常不錯了。雙埠sram經常應用於cpu與其周邊控制器等類似需要直接訪問存儲器或者需要隨機訪問緩衝器之類的器件之間進行通信的情況。從存儲 ...

普通的存儲器器件為單埠,也就是數據的輸入輸出只利用一個埠,設計了兩個輸入輸出埠的就是雙埠sram。雖然還具有擴展系列的4埠sram,但雙埠sram已經非常不錯了。雙埠sram經常應用於cpu與其周邊控制器等類似需要直接訪問存儲器或者需要隨機訪問緩衝器之類的器件之間進行通信的情況。

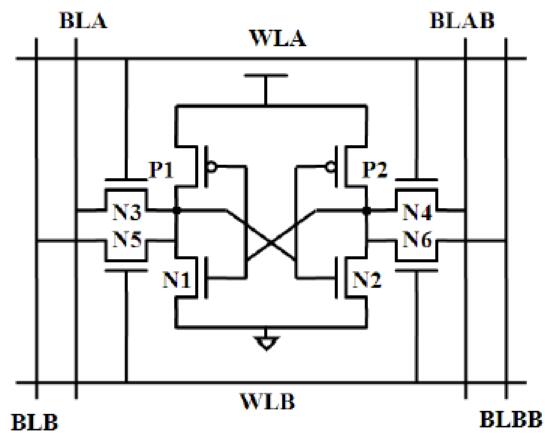

從存儲單元來看,雙埠SRAM只是在單埠SRAM的基礎上加上了兩個存取管(見圖1),但要實現兩個埠對存儲單元的獨立讀寫,還要對新增的埠複製一套單埠SRAM的讀寫外圍電路。然而這樣雖然增強了存儲器的讀寫能力,但卻是以降低存儲單元的穩定性為代價的,具體表現為雙埠SRAM的兩個埠進行同行存取時發生的讀寫干擾(Read/WriteDisturbance)問題;並且當兩個埠進行非同步存取時,讀寫干擾會表現出一定的規律性;對讀寫干擾問題目前尚未找到完美的解決方法,現有的各個方法都具有一定的側重方向。

圖1雙埠SRAM單元

讀干擾的原理分析

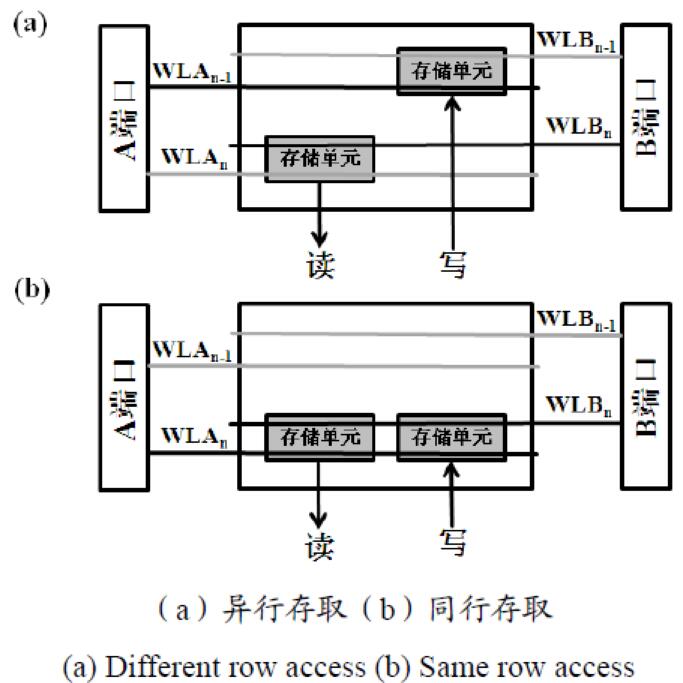

如圖2(a)所示,當雙埠SRAM的兩個埠對不同的行進行操作時,只有連接在WLAn-1和WLBn上的存取管才會被打開,即一個雙埠SRAM存儲單元只有兩個存取管被打開,所以此時雙埠SRAM單元可以像單埠SRAM單元一樣工作。但是如果兩個埠對同一行進行操作時,如圖2(b),由於半選擇問題該行所有存儲單元的所有存取管都將被打開。當一個進行讀操作的存儲單元的所有存取管都被打開時,和單埠SRAM讀操作時存取管降低RSNM同理,該單元的RSNM將有更大幅度的下降,這稱為讀干擾;此外,偽讀取操作對執行寫操作的存儲單元的數據寫入也會造成困難,這稱為寫干擾。現在假設A埠在進行讀操作,B埠在進行寫操作,下麵分別分析讀干擾。

圖2埠SRAM的兩種存取情形

讀干擾

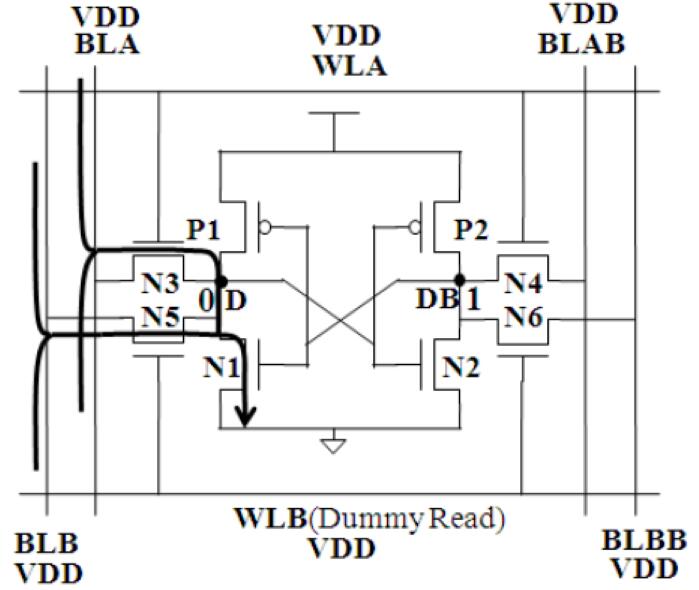

圖3是圖2(b)中左邊進行讀操作的存儲單元的具體情形,可以看到,B埠的寫操作使WLB為高電平,此高電平對該單元產生了偽讀取操作。與單埠SRAM的讀取操作相比,下拉管N1將同時對BLA和BLB放電,這將導致兩個結果:第一,對BLA的放電電流減小,造成讀取時間增加;第二,D點電壓將會比單埠SRAM中讀取操作升高得更高,從而進一步降低RSNM,甚至直接使單元翻轉。對於後者可以這樣簡單地分析:N3和N5同時打開後,二者並聯,若將其看成整體,則存取管的寬度將增加一倍,其“電阻”減半,而N1的電阻不變,故在放電通路上D點的分壓變得更高;對於前者,雖然放電通路的電阻減小,N1的下拉電流增大,但其還沒有增大到原來的兩倍(其寬度加倍電流才會加倍),而N3和N5的電流相等,故N3分得的電流較之單埠SRAM將減小。

圖3雙埠SRAM單元中的讀干擾