SDRAM有一個同步介面,在響應控制輸入前會等待一個時鐘信號,這樣就能和電腦的系統匯流排同步。時鐘被用來驅動一個有限狀態機,對進入的指令進行管線(Pipeline)操作。這使得SDRAM與沒有同步介面的非同步DRAM相比,可以有一個更複雜的操作模式。下麵宇芯電子介紹關於靜態SDRAM和動態SDRAM的 ...

SDRAM有一個同步介面,在響應控制輸入前會等待一個時鐘信號,這樣就能和電腦的系統匯流排同步。時鐘被用來驅動一個有限狀態機,對進入的指令進行管線(Pipeline)操作。這使得SDRAM與沒有同步介面的非同步DRAM相比,可以有一個更複雜的操作模式。下麵宇芯電子介紹關於靜態SDRAM和動態SDRAM的區別。

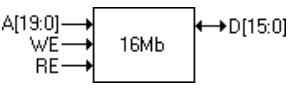

靜態記憶 假設我們要將16Mb存儲器連接到FPGA。 16Mb表示記憶體可容納1600萬位(準確地說是16777216位)。現在,很少對比特進行單獨定址,而是通常以8或16的數據包(我們稱其為字)進行定址。因此,如果我們的16Mb存儲器被組織為16位的1M字,則需要20位地址匯流排和16位數據匯流排,以及一些可寫和可讀信號。

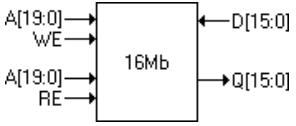

實際的存儲器也將具有CS(片選),如果存儲器是同步的,則為時鐘(為清晰起見,在圖片中將其省略)。 現在,如果該記憶體是一個Blockram(在FPGA內部),它將看起來有所不同(假設存在如此大的16Mb Blockram ...典型的Blockram要小得多)。

如您所見,它仍然是一塊記憶體,但是有兩條地址匯流排。那是因為現代FPGA中的Blockram是雙埠的……這意味著兩個代理可以同時訪問存儲器。通常,一個代理寫入記憶體,而另一個則讀取。因此,每個代理的記憶體都有獨立的地址和數據匯流排。上面的圖片在頂部顯示了第一個(寫)代理,在底部顯示了第二個(讀)代理。更高級的Blockram允許每個代理讀取和寫入,但是上面顯示的體繫結構是最常用的。同樣,blockram通常也被同步使用,因此每個代理都必須提供一個時鐘(未在圖片中顯示)。

到目前為止,所顯示的記憶體是靜態的,這意味著僅通過對其施加電源即可保存其內容。另外,靜態存儲器可以看作是一個長字形的線性數組(您只需提供一個地址即可訪問匹配的數據...無需複雜)。需要權衡的是每比特成本要比...高得多。

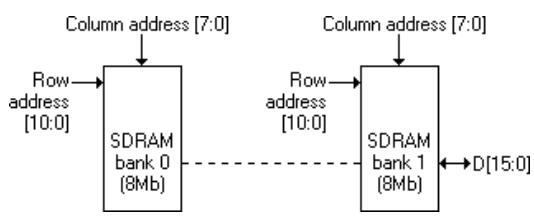

動態記憶 我們將使用SDRAM,它是動態記憶體(SDRAM中的“ D”)。在動態記憶體中,記憶體不被視為單詞的長線性數組,而是被組織為單詞的矩陣(行/列)。

上圖顯示行的12位和列的8位,如前所述總共有20個地址位...很容易。

有一種複雜性:為了提高性能,將記憶體分成相等的塊(稱為“存儲體”)。那是因為某些動態記憶體操作速度很慢,因此擁有存儲體可以在等待另一個存儲體的同時使用它。

因此,如果我們的16Mb SDRAM有2個存儲區,則每個存儲區擁有8Mb。

訪問SDRAM時,FPGA必須選擇存儲體(1位),行(現在只有11位)和列(8位),總共需要20位。但這是一個兩步過程:首先是行+庫,然後是列:

•FPGA選擇一個存儲區並激活其行之一。然後它等待幾個時鐘(等待行準備就緒)。

•現在,該行處於活動狀態,FPGA只需提供列地址即可訪問(讀取和/或寫入)該行中所需的任何數據。

•FPGA處理完該行後,必須先關閉該行,然後再打開新行。

為了獲得最佳性能,用戶(= FPGA)希望避免過多地打開和關閉行,而是在關閉行之前儘可能多地完成工作,併在不同存儲體中進行交錯操作,以免浪費時鐘周期。大多數SDRAM實際上有4或8個存儲體,每個存儲體都是獨立的,因此可以激活自己的行。