靜態RAM的基本構造塊是SRAM存儲單元。通過升高字線的電平觸發存儲單元,再通過位線對所觸發的存儲單元進行讀出或寫入。在靜態CMOS存儲器中,存儲單元陣列將會占去整個存儲器晶元面積的一半以上,在一些大容量的SRAM中,這個比例還要更大一些。因而減小存儲單元出的面積變得尤為重要。一方面我們希望單元面積 ...

靜態RAM的基本構造塊是SRAM存儲單元。通過升高字線的電平觸發存儲單元,再通過位線對所觸發的存儲單元進行讀出或寫入。在靜態CMOS存儲器中,存儲單元陣列將會占去整個存儲器晶元面積的一半以上,在一些大容量的SRAM中,這個比例還要更大一些。因而減小存儲單元出的面積變得尤為重要。一方面我們希望單元面積越小越好;而另一方面隨著存儲單元面積的減小,單元的穩定性又會逐漸變差。那麼所謂的存儲器它是靠什麼原理來存儲數據的呢?宇芯來解答。

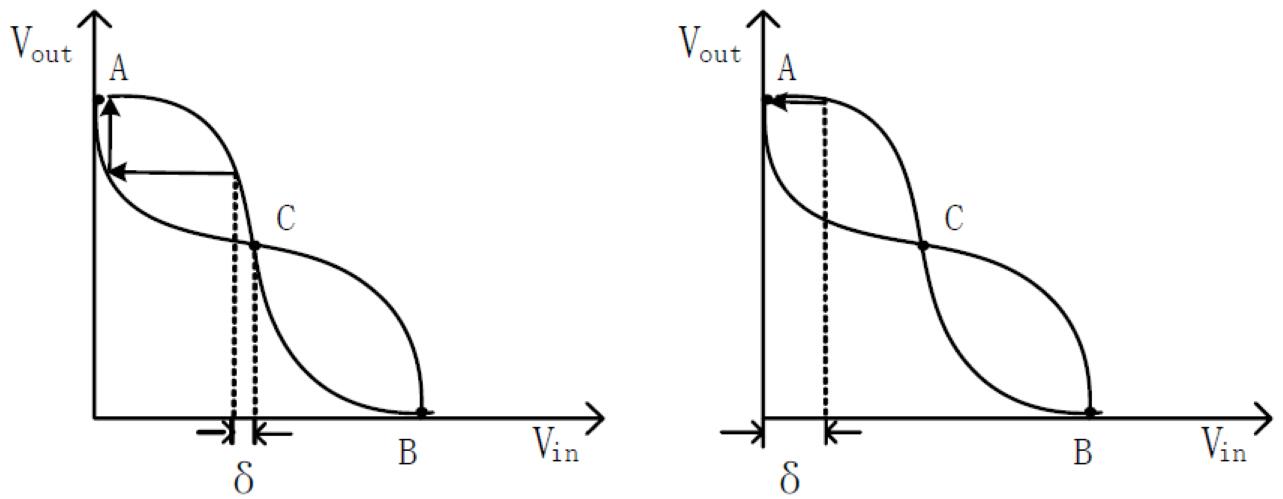

圖1(a)存儲單元偏置在轉折電壓 圖1(b)存儲單元工作在穩態

我們可以在同一坐標系中做出兩個反相器的電壓傳輸特性曲線,如圖1所示。兩條曲線共有三個交點:A、B與C,其中A、B兩點表示電路工作在穩態,而C點則意味著電路處於亞穩態(C點代表反相器電壓傳輸特性曲線上的轉折電壓)。假設此時電路偏置在C點,若雜訊使得Vin的電位值有一個很小的變化δ,由於在轉折電壓附近反相器的電壓增益大於1,這個變化值經過兩個反相器的不斷放大,會導致電路逐漸偏離C點而最終穩定在A點(或B點)。當電路處在A點(或B點)所對應的穩態時,由於電壓增益小於1,即使有很大的電位偏移,這種偏移也會逐漸減小而消失。其變化過程如圖1(b)所示。由上面的分析我們可以看出,交叉耦合的反相器構成了一個雙穩態的電路,兩個穩定狀態正好與邏輯“1”、邏輯“0”相對應。因此這種電路結構被用作數據存儲電路。它完全可以實現對數字信號的存儲與非破壞性讀出。