一、S5PV210時鐘系統 時鐘:一定頻率的電信號。 時鐘系統:基於CMOS工藝的高性能處理器時鐘系統,集成PLL可以從內部觸發,比從外部觸發更快且更準確,能有效地避免一些與信號完整性相關的問題。 S5pv210時鐘系統,參考s5pv210手冊第三章,CLOCK CONTROLLER S5pv210 ...

一、S5PV210時鐘系統

時鐘:一定頻率的電信號。 時鐘系統:基於CMOS工藝的高性能處理器時鐘系統,集成PLL可以從內部觸發,比從外部觸發更快且更準確,能有效地避免一些與信號完整性相關的問題。

S5pv210時鐘系統,參考s5pv210手冊第三章,CLOCK CONTROLLER

S5pv210時鐘管理單元(CMU)主要瞭解了以下信息

1、時鐘域:s5pv210主要由三個時鐘域組成

a:MSYS域:Cortex A8處理器、DRAM記憶體控制器(DMC0和DMC1)、3D、內部SRAM(IRAM和IROM)、INTC和配置介面(SPERI)。Cortex A8僅支持同步模式,因此必須與200MHz軸匯流排同步運行。

b:DSYS域:與顯示相關的模塊,包括FIMC、FIMD、JPEG和多媒體IP(X、L和T塊中提到的所有其他IP)。都是和視頻顯示、編解碼等有關的模塊

c:PSY域:安全、I/O外圍設備和低功耗音頻播放。如串口、SD介面、I2C、AC97、USB等

每個匯流排系統分別以200兆赫(最大)、166兆赫和133兆赫運行。在兩個不同的域之間有非同步匯流排橋(BRG)。

S5Pv210由三個時鐘域組成,即主系統(MSY)、顯示系統(DSY)和外圍系統(PSY)

2、時鐘的聲明

S5pv210的時鐘包括兩種:來自clock pads的時鐘,來自CMU的時鐘,跟來自USB PHY的時鐘

a:來自CLOCK PADS的時鐘包括幾個晶振介面

•xrtcxti:使用xrtcxti和xrtcxto管腳指定32.768 kHz晶體板的時鐘

•xxti:指定從帶xxti和xxto針的水晶板的時鐘

•xusbxti:指定帶有xusbxti和xusbxto引腳的水晶板上的時鐘

•xhdmixti:使用xhdmixti和xhdmixto管腳指定27MHz晶體板的時鐘

b:來自時鐘管理系統(CMU)的時鐘

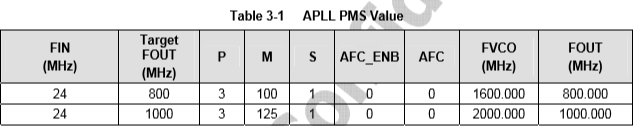

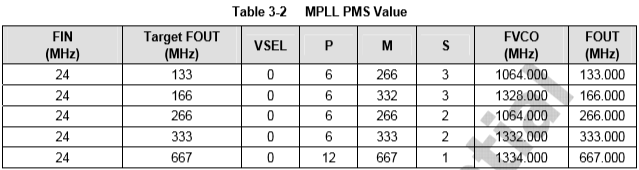

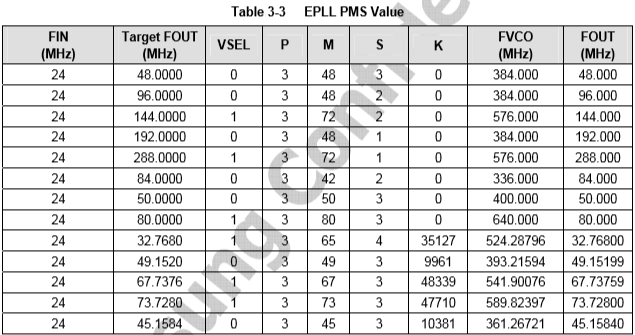

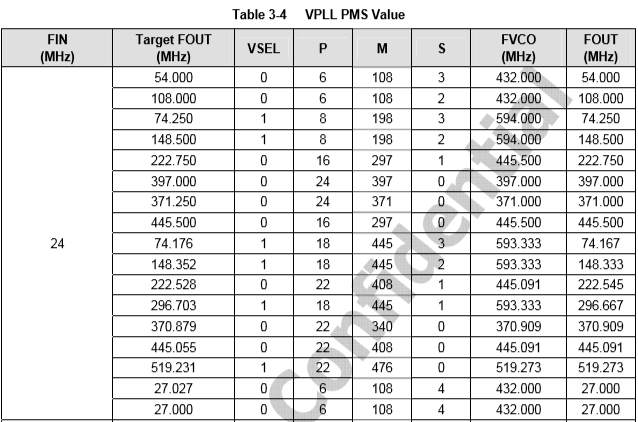

主要分為不同頻段的控制輸入,在典型的S5Pv210應用中,•Cortex A8和MSys時鐘域使用APLL(即,ARMCLK、HCLK-MSY和PCLK-MSY)。

3、時鐘的關係

三個時鐘域(MSYS時鐘域、DSY時鐘域、PSY時鐘域)對應都有不同對應的取值範圍,每個高性能操作的值都對應不同的頻率

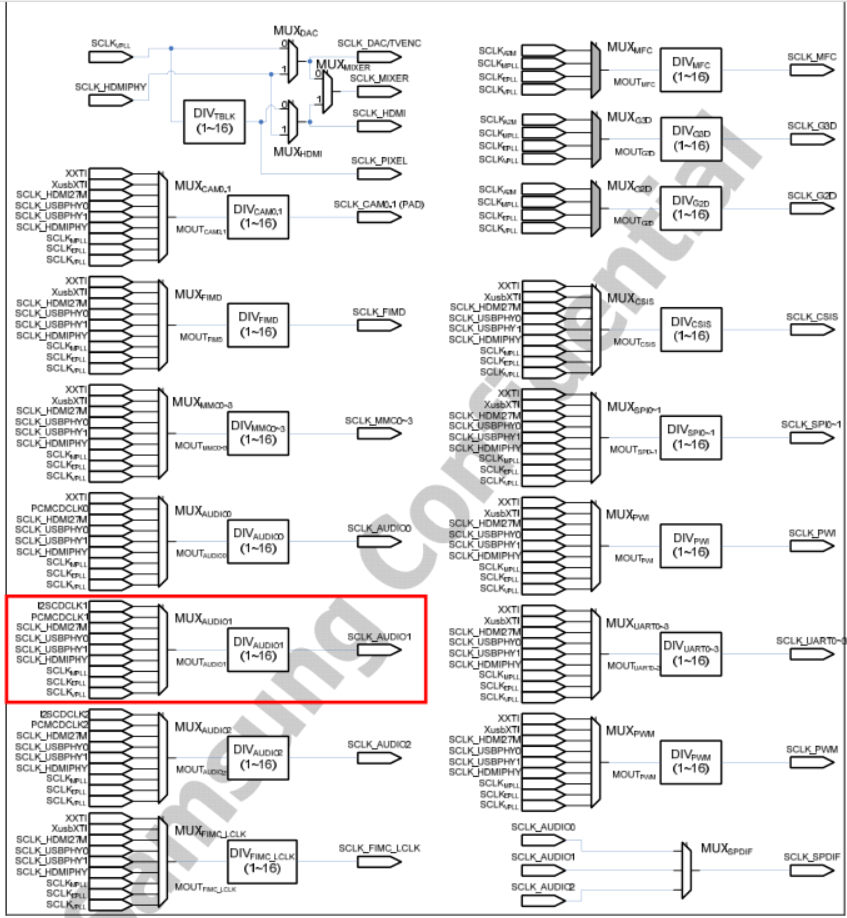

4、時鐘的生成

s5pv210時鐘生成的邏輯框圖如下

時鐘生成器塊還包括內置邏輯,用於在每次系統重置後穩定時鐘頻率,因為時鐘在穩定之前需要時間。

s5pv210的兩種類型MUX時鐘開關:灰色時鐘mux表示無故障時鐘mux,如果更改時鐘選擇,則無故障時鐘mux。白色的時鐘mux代表非無故障時鐘mux,在改變時鐘源時可能會出現故障。

對於無故障多路復用器,應確保當時鐘選擇從一個更改為另一個時,兩個時鐘源都在運行。如果沒有同時使用,對於非無故障時鐘MUX,在更改時鐘時可能會出現故障。時鐘更改完成後,用戶可以重新啟用非無故障時鐘MUX的輸出,這樣就不會因時鐘更改而出現故障。非無故障多路復用器的屏蔽輸出由時鐘源控制寄存器處理。(下麵還有時鐘源控制寄存器的一些瞭解)

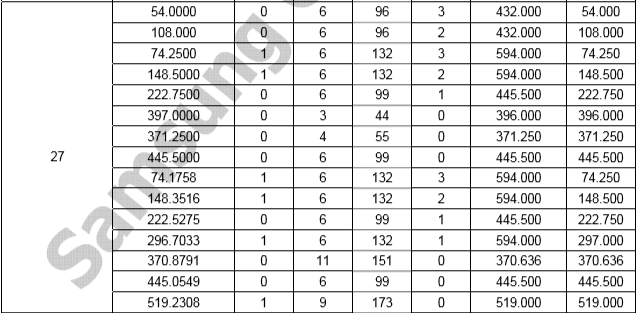

5、時鐘配置程式

基本SFR配置流程:

打開PLL(A、M、E、V)PLL U CON[31]=1;//打開PLL(參考(A、M、E、V)PLL U CON SFR)

wait_lock_time;//等待PLL鎖定

(a,m,e,v)pll_sel=1;//在pll輸出時鐘穩定後,選擇pll輸出時鐘而不是輸入參考時鐘。

更改系統時鐘分頻器值clk_div0[31:0]=目標值0;

更改特殊時鐘的除法器值clk_div1[31:0]=目標值1;

clk_div2[31:0]=目標值2;

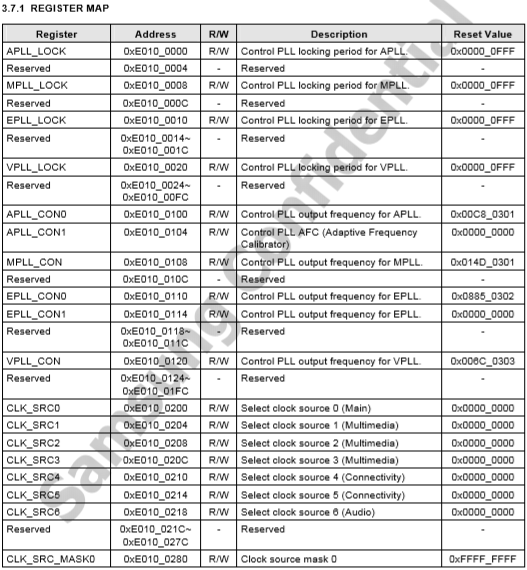

6、S5PV210時鐘設置寄存器

-xPLL_LOCK:控制PLL鎖定頻率的周期,譬如24MHZ變為1GHZ這段是需要一段時間的,通過一個鎖相環使得把24MHZ鎖定為1GHZ,所以就需要鎖定頻率的周期了。(鎖定頻率)

-xPLL_CON:打開/關閉PLL電路,設置PLL的倍頻參數,查看PLL鎖定狀態等。(決定倍頻到多少)

-CLK_SRCn(n:0~6):用來設置時鐘來源的,對應時鐘框圖中的mux開關。(決定時鐘來源)

-CLK_SRC_MASKn:打開關閉時鐘源。(開頭部分)

-CLK_DIV_STATn:各模塊的分頻參數配製。(決定分頻多少)

-CLK_SRC_GATE_x:打開關閉時鐘門。(結尾部分)

-CLK_DIV_STATn:分頻狀態寄存器,確保是否已經分頻完成。

-CLK_MUX_STATn:選擇開關狀態寄存器,確保是否已經選擇開關完畢。

7、時鐘源控制寄存器

S5Pv210有許多時鐘源,包括四個PLL輸出、外部振蕩器、外部時鐘和來自GPIO的其他時鐘源。CLK U SRCN寄存器控制每個時鐘分頻器的源時鐘。

以此來設置時鐘開關

時鐘源寄存器(CLK U SRC0,R/W,地址=0XE010 U 0200)

在s5pv210手冊中可以看到,所有的寄存器都是按塊分的。我們可以找到一個寄存器的基地址,再通過基址加編址定址的方式在找到寄存器。

8、後面還有s5pv210時鐘的MUX狀態SFR 以及各種時鐘源開關太多了還沒看完

二、s5pv210的記憶體初始化

1、SDRAM定義和特性

SDRAM:Syncronized Dynamic Ramdam Access Memory,同步動態隨機存儲器

DDR:DDR就是DDR SDRAM,是SDRAM的升級版。(DDR:double rate,雙倍速度的SDRAM)

DDR有好多代:DDR1 DDR2 DDR3 DDR4 LPDDR

SDRAM的特性:容量大、價格低、掉電易失性、隨機讀寫、匯流排式訪問。

SDRAM在整個硬體系統中是屬於外部設備,通過地址匯流排和數據匯流排介面與SoC通信

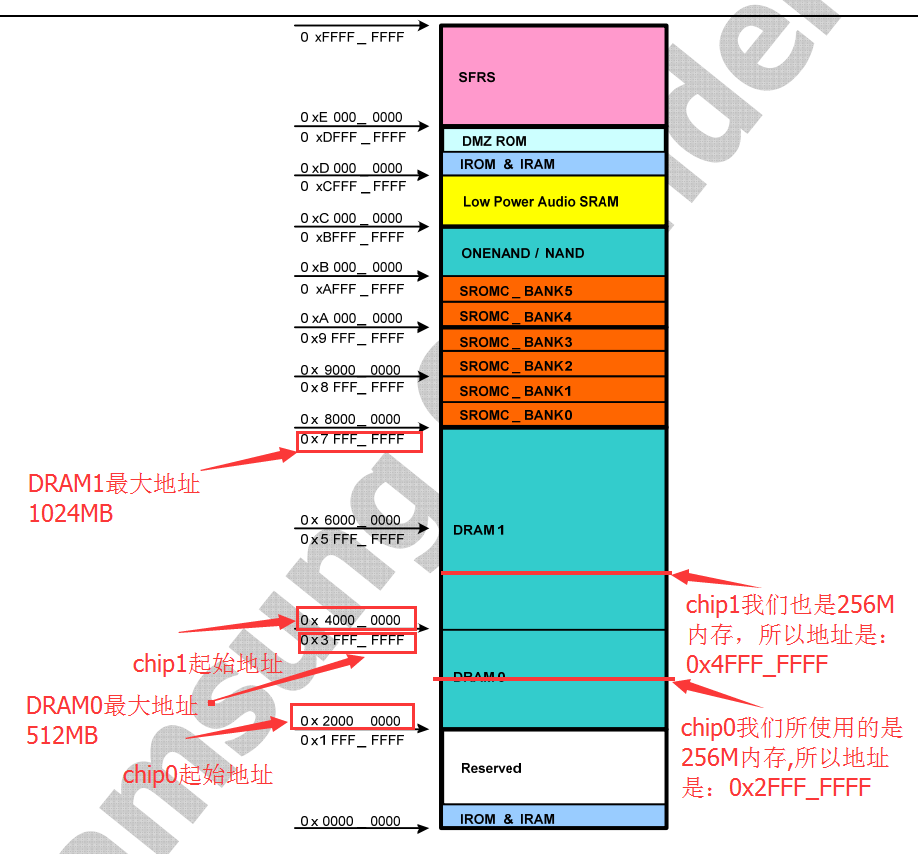

2、記憶體地址詳解

3:定址詳解

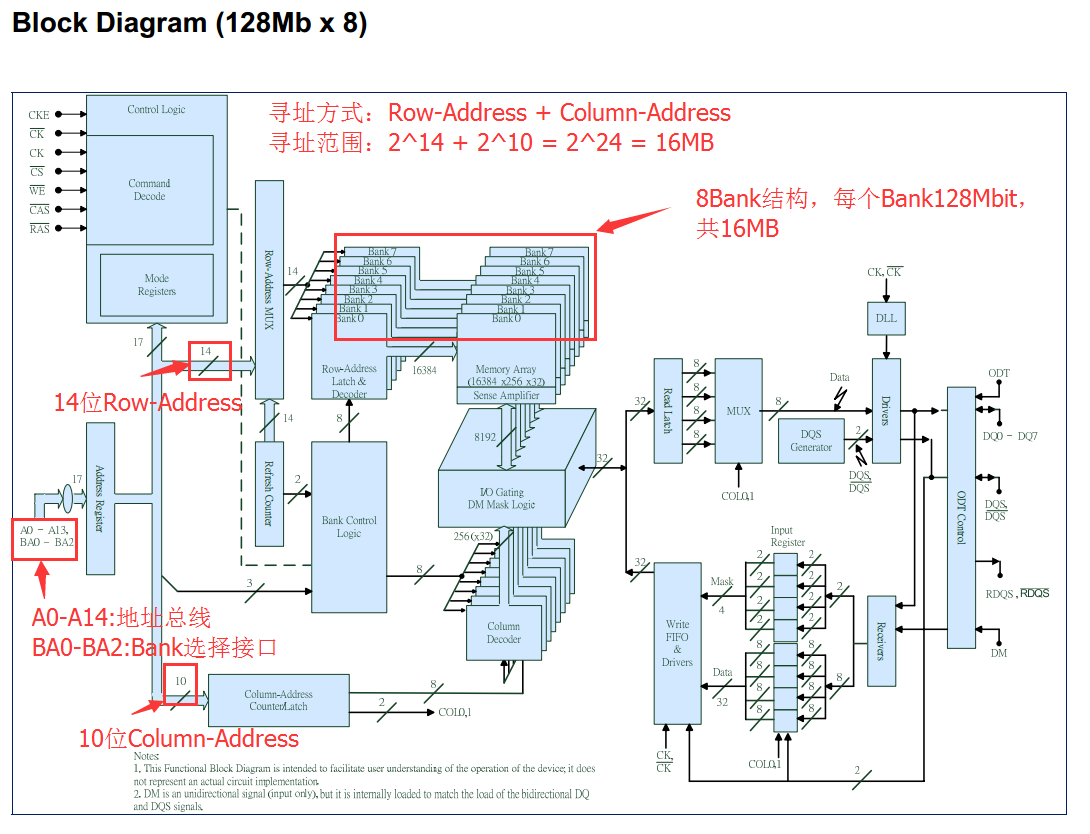

在數據手冊《NT5TU64M16GG-DDR2-1G-G-R18-Consumer》第10頁的block diagram中,詳解如上。

採用128Mb * 8 結構,每個Bank可定址的大小是16MB,BA0-BA2用來選擇8個Bank,定址的方式:Row-Address+Column-Address。

故單記憶體晶元可定址的大小為:16MB * 8 = 128MB

兩片單晶元記憶體並聯組合成32位數據匯流排,可與SoC進行匯流排通信,可定址的記憶體大小便為:128MB+128MB= 256MB,在九鼎的開發板上採用了DRAM0+DRAM1分配記憶體地址,所以DRAM0和DRAM1都是256MB記憶體大小,合起來就是512MB記憶體大小。

所以開發板上DRAM0和DRAM1可定址的有效範圍分別為:

DRAM0:0x20000000 - 0x2FFFFFFF (256MB)

DRAM1:0x40000000 - 0x4FFFFFFF (256MB)

其他地址為非法地址,比如:0x30000000

初始化過程包括phy dll初始化、設置控制器寄存器和記憶體初始化。記憶體初始化請參考JEDEC規範和記憶體設備數據表。有三種不同的記憶體類型,即lpddr、lpddr2和ddr2。根據記憶體類型,初始化順序如下

1)、Lpddr記憶體初始化順序:

1、為了給控制器和存儲設備提供穩定的電源,控制器必須斷言和保持CKE到邏輯的高水平。然後應用穩定時鐘。註:xddr2sel應為低電平,以將CKE保持在高電平。

2、根據時鐘頻率將phycontrol0.ctrl_start_point和phycontrol0.ctrl_inc位欄位設置為正確的值。將phycontrol0.ctrl_dll_on位欄位設置為“1”以激活phy dll。

3、DQS清洗:根據時鐘頻率和記憶體TAC參數,將phycontrol1.ctrl_shiftc和phycontrol1.ctrl_offsetc位欄位設置為正確的值。

4、將phycontrol0.ctrl_開始位欄位設置為“1”。

5、設置控制器。此時,應關閉自動刷新計數器。

6、設置memcontrol。此時,所有斷電模式都應關閉。

7、設置memconfig0寄存器。如果有兩個外部記憶體晶元,也可以設置memconfig1寄存器。

8、設置prechconfig和pwrdconfig寄存器。

9、根據存儲器交流參數設置正時參考、正時行、正時數據和正時功率寄存器。

10、如果需要QoS方案,請設置QosControl0~15和QosConfig0~15寄存器。

11、等待phystatus0.ctrl_locked位欄位更改為“1”。檢查phy dll是否被鎖定。

12、phy dll可以補償在記憶體操作過程中由進程、電壓和溫度(pvt)變化引起的延遲量的變化。因此,不應為可靠運行而關閉。如果頻率低,phy dll可以關閉。如果使用關閉模式,請根據phystatus0將phycontrol0.ctrl_force位欄位設置為正確的值。ctrl_lock_value[9:2]位欄位用於固定延遲量。清除phycontrol0.ctrl_dll_on bit-欄位以關閉phy dll。

13、確認

14、通電後穩定時鐘是否至少發出200us。使用directCmd寄存器發出pall命令。

15、使用directCmd寄存器發出兩個自動刷新命令。

16、使用directcmd寄存器發出mrs命令以編程操作參數。1-3 S5Pv210_M 1 DRAM控制器

17、使用directcmd寄存器發出emrs命令以編程操作參數。

18、如果有兩個外部存儲晶元,則對Chip1存儲設備執行步驟14~17。

19、將控制器設置為打開自動刷新計數器。

20、如果需要斷電模式,請設置MEMControl寄存器。

2)lpddr2記憶體類型的初始化順序:

1、為了給控制器和存儲設備提供穩定的電源,控制器必須斷言並將CKE保持在邏輯低水平。然後應用穩定時鐘。註:xddr2sel應為高電平,以將CKE保持在低電平。

2、根據時鐘頻率將phycontrol0.ctrl_start_point和phycontrol0.ctrl_inc位欄位設置為正確的值。將phycontrol0.ctrl_dll_on位欄位設置為“1”以激活phy dll。

3、DQS清洗:根據時鐘頻率和記憶體TAC參數,將phycontrol1.ctrl_shiftc和phycontrol1.ctrl_offsetc位欄位設置為正確值。

4、將phycontrol0.ctrl_開始位欄位設置為“1”。

5、設置控制器。此時,應關閉自動刷新計數器。

6、設置memcontrol。此時,所有斷電模式都應關閉。

7、設置memconfig0寄存器。如果有兩個外部存儲器晶元,則設置memconfig1寄存器。

8、設置prechconfig和pwrdconfig寄存器。

9、根據存儲器交流參數設置正時參考、正時行、正時數據和正時功率寄存器。

10、如果需要QoS方案,請設置QosControl0~15和QosConfig0~15寄存器。

11、等待phystatus0.ctrl_locked位欄位更改為“1”。檢查phy dll是否被鎖定。

12、phy dll可以補償在記憶體操作過程中由進程、電壓和溫度(pvt)變化引起的延遲量的變化。因此,phy dll不應關閉以實現可靠的操作。除低頻運行外,它可以關閉。如果使用關閉模式,請根據phystatus0將phycontrol0.ctrl_force位欄位設置為正確的值。ctrl_lock_value[9:2]位欄位用於固定延遲量。清除phycontrol0.ctrl_dll_on位欄位以關閉phy dll。

13、將phycontrol1.fp_resync位欄位設置為“1”以更新dll信息。

14、確認在通電後,CKE仍保持邏輯低電平至少100ns。

15、發出一個nop命令,使用directcmd寄存器斷言和保持CKE到一個邏輯高級。

16、至少等待200us。 1-4 S5Pv210_M 1 DRAM控制器

17、使用directCmd寄存器發出mrs命令以重置記憶體設備並編程操作參數。

18、等待至少1us。

19