其實之前也有提及過,Cypress公司提供的官方文件和應用手冊真的可以解決很多問題。做的也很人性化,操作也及其簡單,幾乎只要在 TD_int()裡面配置一些常用的參數即可,其他都可以不用操作。 作為一個常用查詢手冊吧!!!! 《EZ-USB一些重要寄存器的配置》博客中已經提及過相關寄存器的配置,那麼 ...

其實之前也有提及過,Cypress公司提供的官方文件和應用手冊真的可以解決很多問題。做的也很人性化,操作也及其簡單,幾乎只要在 TD_int()裡面配置一些常用的參數即可,其他都可以不用操作。

作為一個常用查詢手冊吧!!!!

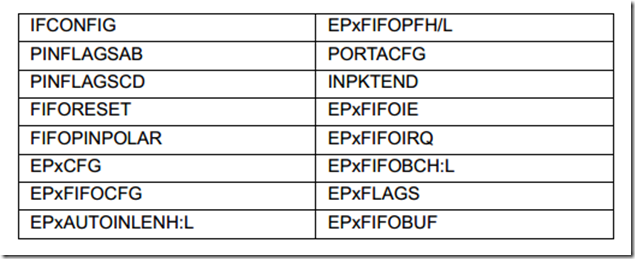

《EZ-USB一些重要寄存器的配置》博客中已經提及過相關寄存器的配置,那麼對於slave fifo模式需要配置的寄存器如下所示:

REVCTL

CPUCS

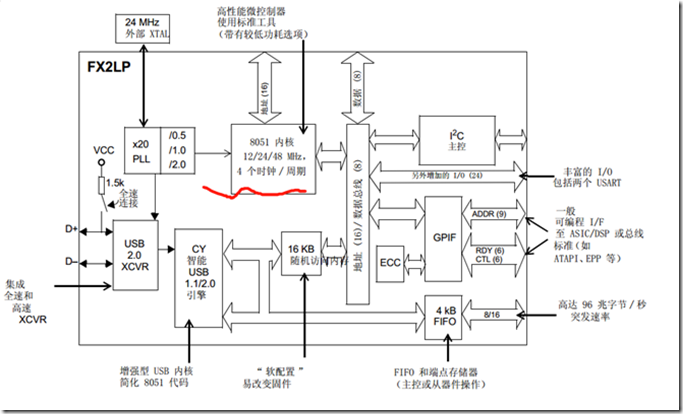

接下來對上述寄存器的配置,都要根據上述原理圖來進行,一定要配置時查看此原理圖,很有幫助。當然更多的配置信息請參考之前的博客《EZ-USB一些重要寄存器的配置》,這裡講解為什麼這麼配置。

1.CPUCS(TRM手冊page338)

針對CY原理圖,可以有12MHz,24Mhz,以及48MHz可以進行配置,CY的工作輸入時鐘是24MHz ,經過內部的PLL電路然後進行倍頻和分頻。

針對CY原理圖,可以有12MHz,24Mhz,以及48MHz可以進行配置,CY的工作輸入時鐘是24MHz ,經過內部的PLL電路然後進行倍頻和分頻。

參考AN61453,設置為48MHz,當然也可以設置為其他頻率,這個主要影響8051內核工作頻率。

設置 CPUCS = 0x12

2.IFCONFIG

若要將CY配置成slave fifo模式,那麼需要 IFCONFIG[1:0]為 11.同步模式下IFCONFIG.3為1.

若要將CY配置成slave fifo模式,那麼需要 IFCONFIG[1:0]為 11.同步模式下IFCONFIG.3為1.

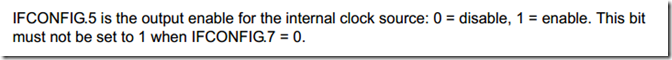

b7選擇時鐘源,為0時,設置為外部時鐘,設為1時,內部時鐘(30~48MHz) ;此外若是使用外部ifclk,在固件設置b7等於0之前,ifclk必須達到。

b6選擇30M還是48M,1為48MHz,0為30MHz。

b5是設置ifclk引腳的輸出使能,0為三態,1為驅動。(當使用外部時鐘時,此位必須設置為1)

b4設置時鐘是否反向,0為不反向,1為反向。

b3設定工作在同步狀態還是非同步狀態。0為同步,1為非同步。

b2是設置port E,筆者使用的是56pin,沒有port E埠。

b1:0設為11,為slave模式

IFCONFIG =0x43; //選擇為外部時鐘,且時鐘頻率為48MHz,且為同步slaveFIFO模式,輸入IFCLK(5~48MHz)(0000_0011)。

3.FD控制

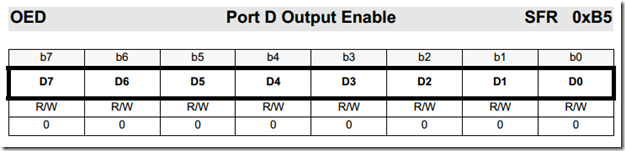

可以配置為8bit或者16bit,若是配置為8bit,port D可以作為普通的IO,但是若是配置為16bit,則port D就不能作為普通的IO使用,上電覆位預設是16bit。

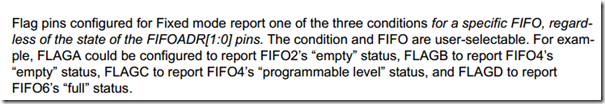

fifo 的flag工作在兩種模式:indexed 和 fixed模式,通過pinflagADCD來控制。

5.sloe,slrd,slwr,pktend,fifoadr[1:0]

5.sloe,slrd,slwr,pktend,fifoadr[1:0]

註意上述的描述,在同步狀態下,是伴隨ifclk的上升沿改變而改變,在非同步狀態下,是伴隨 slwr或者slrd的變化而變化。

註意上述的描述,在同步狀態下,是伴隨ifclk的上升沿改變而改變,在非同步狀態下,是伴隨 slwr或者slrd的變化而變化。

註意下麵關於pktend的說法,這個是主機箱發送一個短的數據包時,使用此功能。PKTEND預設是低電平,且PKTEND可以在任何時候設置,但是需在SLWR或者SLRD之後執行。

b6控制方向,0是輸出,1是輸入;

b5-4模式選擇:

b3緩衝區大小,0是512, 1是1024bytes;其中4和8只能是512, 2和6可選。

b3緩衝區大小,0是512, 1是1024bytes;其中4和8只能是512, 2和6可選。

b1-0是幾個緩衝區:

此參數,若是對於out,設置為0x10,若是對於in,設置為0x08;設為自動模式。

此參數,若是對於out,設置為0x10,若是對於in,設置為0x08;設為自動模式。

7.2 EPXAUTOINLENH:L

註意,這個和上述的EPXCFG,假定端點2緩衝區設置為512位元組,4倍緩衝,儘管這一端點占有了2048位元組RAM,但CPU只認識“激活的”512位元組緩衝區。這可以從寄存器長度看得出來,比如,EP2BCH:L是11位,可對1024位元組的最大緩衝區長度進行計數,EP4BCH:L是10位,可對512自己的最大緩衝區長度進行計數。

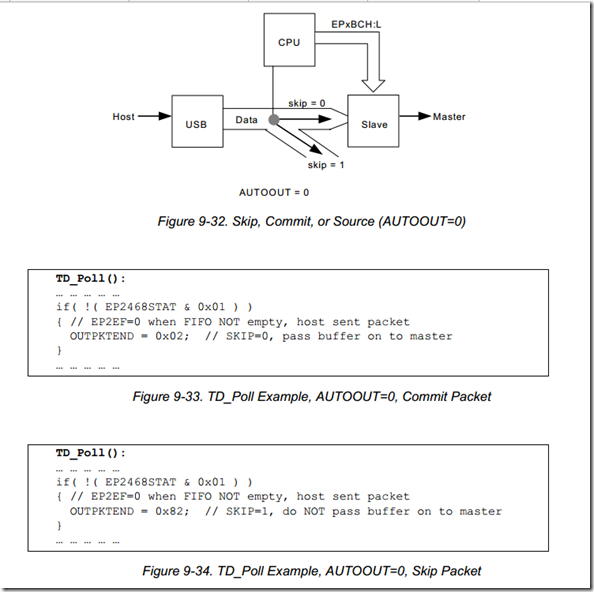

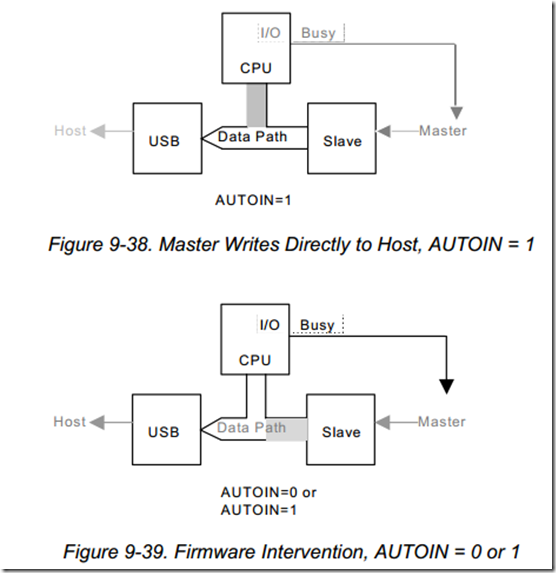

8.CPU是否獲取輸入輸出包

當設定為AUTOIN = 1時,如下圖所示,就不需要CPU參與,直接寫給host。

對於下麵埠,如果使用SLCS功能,則需要將b6設置為1.

0~7對應 A,B,C的7個埠

14.pinflagABCD

14.pinflagABCD

通過下麵的幾個編程,可以實現對端點那個是空,哪個是滿,PF空,FF滿。

在硬體設計中,將SLRD直接拉高處理;PKEND也直接拉高,不做包處理;

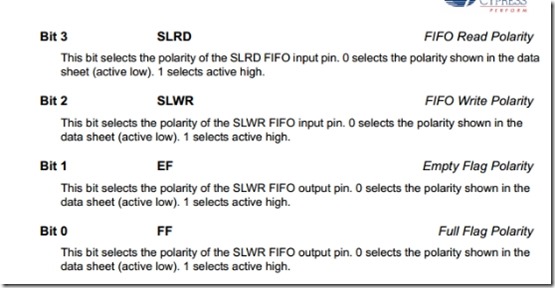

FIFOPINPOLAR = 0x04; //BIT[5:0] = {PKTEND, SLOE, SLRD, SLWR, EMPTY, FULL}

//Set SLWR High Valid; PKTEND,SLOE,SLRD EMPTY, FULL Low Active

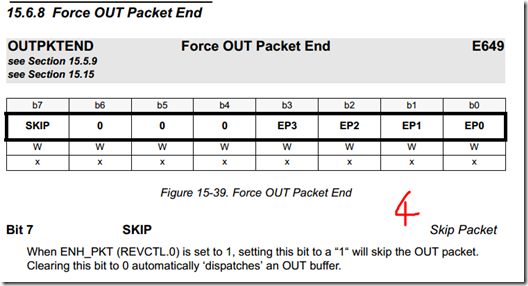

17.INPKTEND/OUTPKTEND