工欲善其事,必先利其器。在使用Vivado自帶的模擬軟體模擬的時候,相對於更優秀的模擬工具Modelsim,效率低了很多,為了更高效的開發,我嘗試著用Vivado級聯Modelsim模擬,但是級聯後還是有一些不方便,所以我便直接使用Modelsim獨立模擬,但是對於IP Core的話,就需要添加Vi ...

工欲善其事,必先利其器。在使用Vivado自帶的模擬軟體模擬的時候,相對於更優秀的模擬工具Modelsim,效率低了很多,為了更高效的開發,我嘗試著用Vivado級聯Modelsim模擬,但是級聯後還是有一些不方便,所以我便直接使用Modelsim獨立模擬,但是對於IP Core的話,就需要添加Vivado IP Core的庫文件,本人查閱了很多資料,最終實現了使用Modelsim模擬Vivado Clocking Wizard IP Core,軟體版本,Vivado 2017.3、Modelsim SE10.4。具體流程如下,實測記錄。

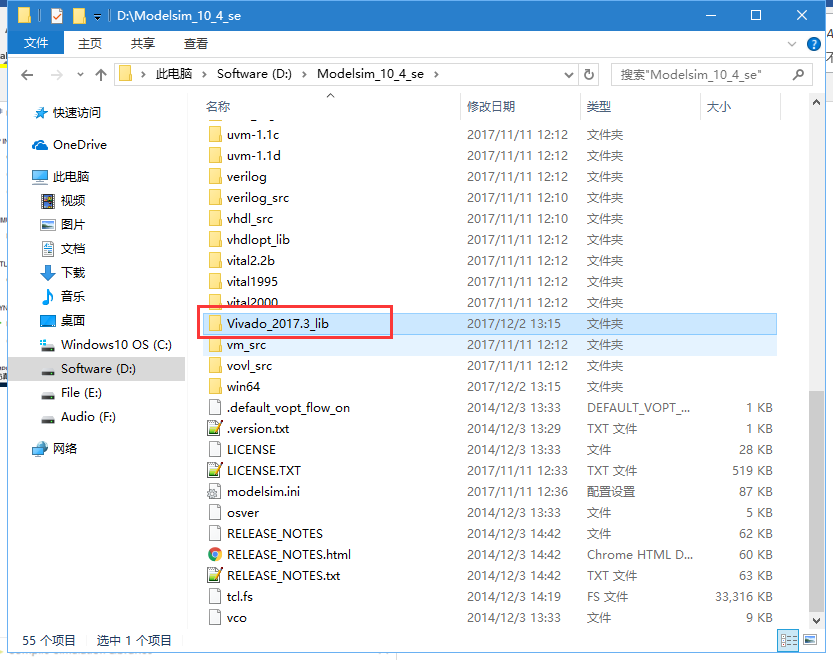

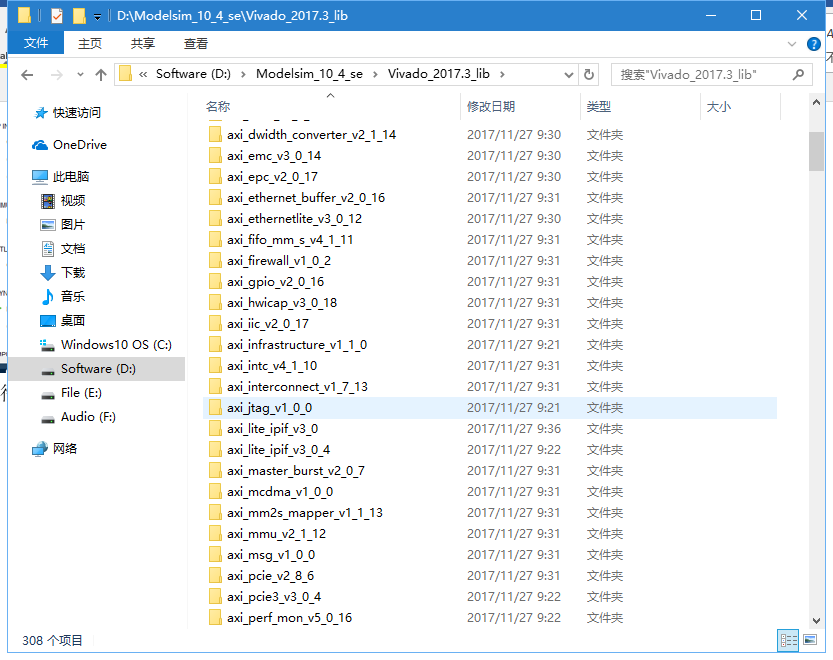

首先,在 Modelsim 的安裝目錄下新建一個文件夾,我這裡是D:\Modelsim_10_4_se\Vivado_2017.3_lib

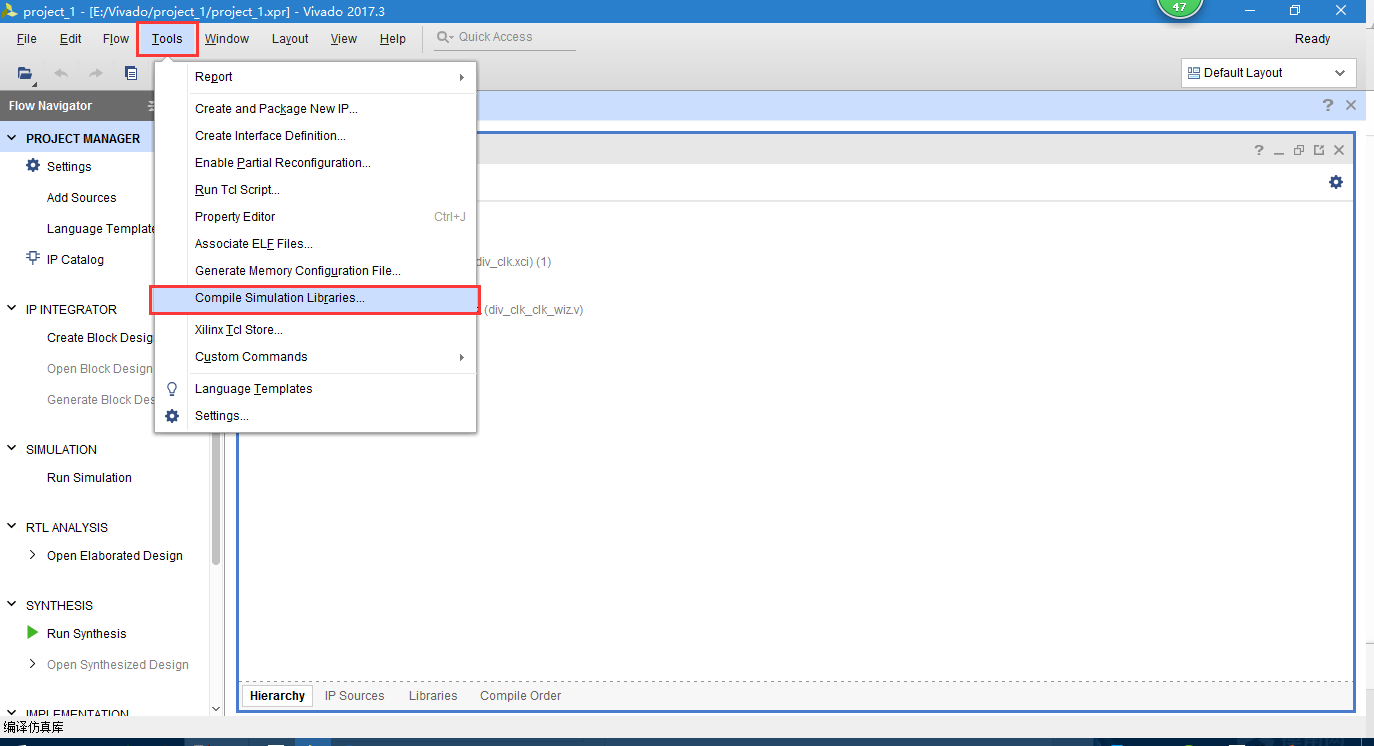

然後,打開Vivado軟體,主界面菜單欄點擊Tools下的Compile Simulation Libraries編譯Vivado模擬庫

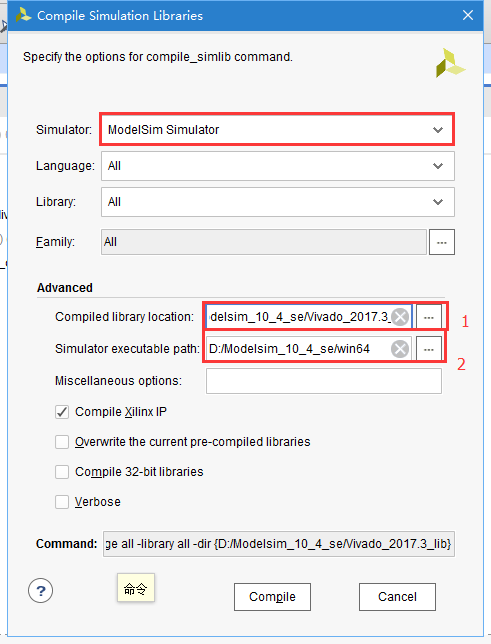

彈出如下視窗然後按如圖所示選擇,1處路徑為剛纔我們新建的文件夾中,2處為Modelsim的運行程式路徑。設置好後點擊compile。

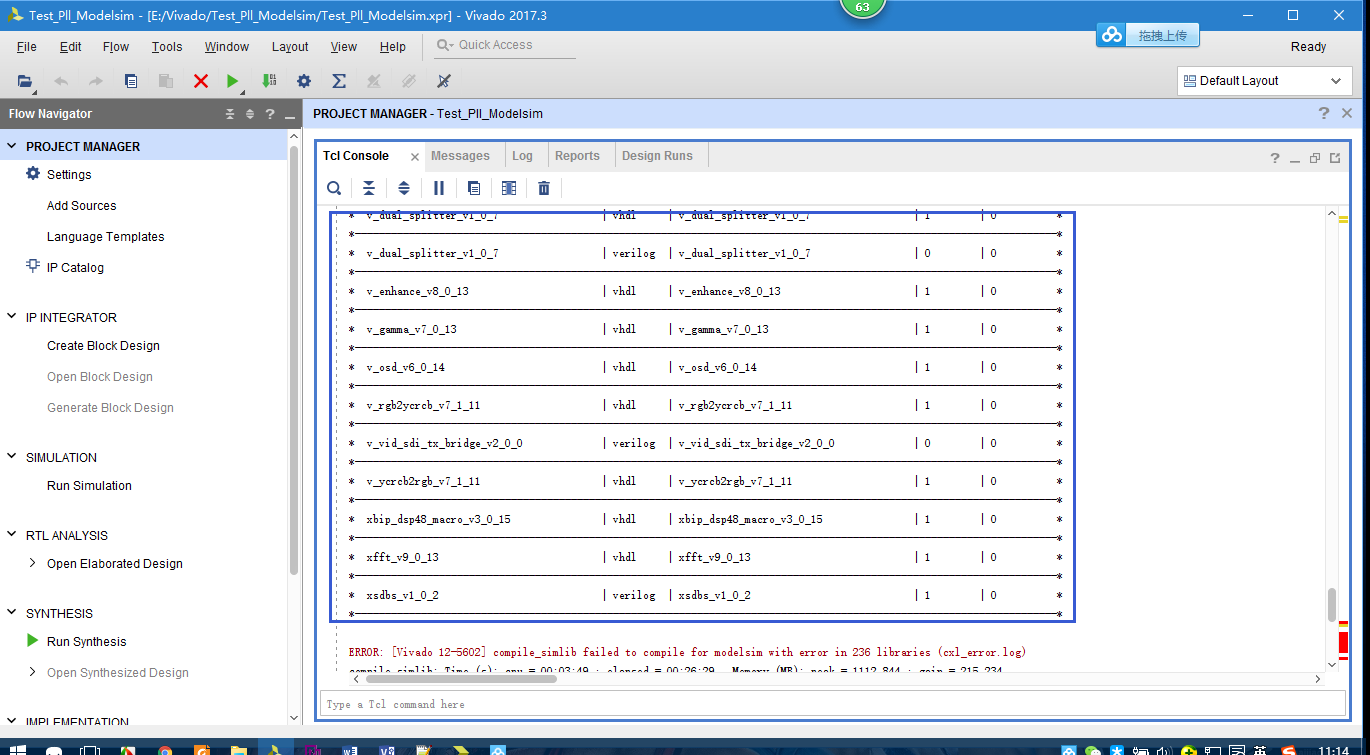

在編譯的過程中視窗會列印出來如下信息。

等待一段時間,Vivado的庫文件編譯完成後我們可以看到文件夾下都是Vivado的庫文件

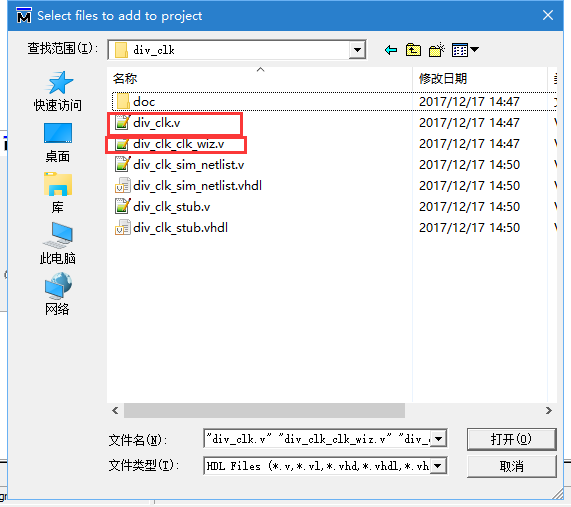

然後使用Vivado新建一個調用的Clocking Wized IP Core的工程,編寫好測試文件,然後再用Modelsim新建一個模擬工程,將測試文件和頂層添加進來。這裡省略掉這些步驟。這裡需要將IP Core中生成的兩個文件添加進來,如下圖所示。

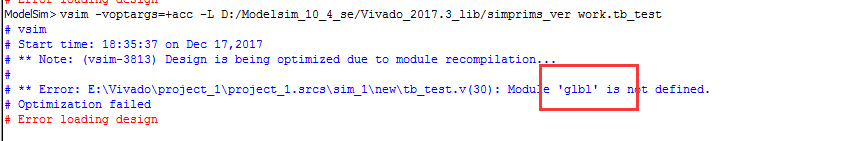

直接在work右鍵點擊test bench文件進行模擬會出現如下錯誤,這是因為沒有添加所仿IP Core的庫文件

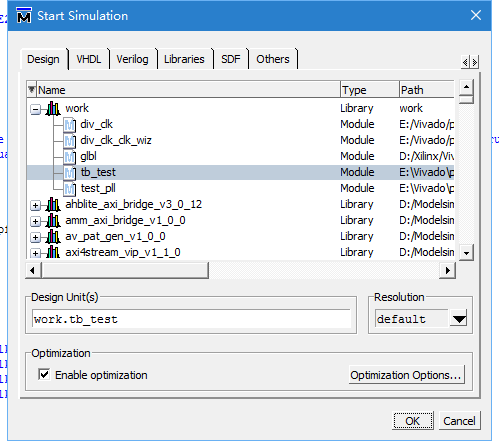

點擊標題欄simulator——start simulator,在work里選中test bench。

點擊libraries,點擊添加所需要的庫,這裡只需要simprims_ver

點擊這裡後還是會出現錯誤,列印出來的信息如下,提示缺少glbl模塊,

這是Xilinx的全局複位模塊,該模塊的路徑在你Vivado的安裝路徑里,比如我的是D:\Xilinx\Vivado2017.3\Vivado\2017.3\data\verilog\src中,把它添加到工程裡面,在test bench中如圖所示例化一下這個模塊,然後重新模擬一次。

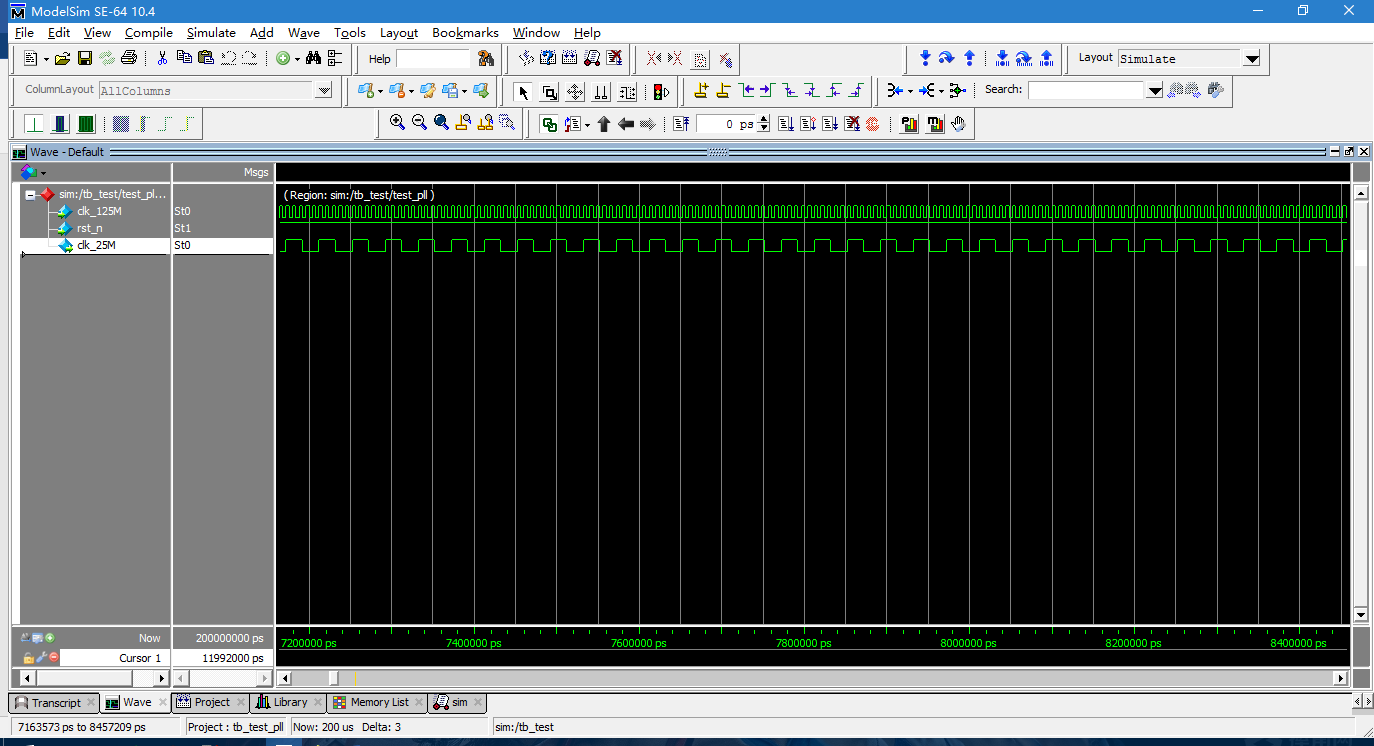

然後就可以看到波形了

我這裡的測試工程師一個125Mhz分25Mhz的五分頻。

接下來本人會繼續嘗試使用Modelsim模擬FIFO、RAM/ROM、Shift_RAM等常用IP Core,如果你有什麼更加高效的方法,歡迎提出,歡迎指點。如果需要Modelsim軟體請關註我的微信訂閱號:開源FPGA,後臺回覆“Modelsim”即可獲得,歡迎加入開源FPGA-交流群-I進行討論,群號碼:677163633。

轉載請註明出處:NingHeChuan(寧河川)

個人微信訂閱號:開源FPGA

如果你想及時收到個人撰寫的博文推送,可以掃描左邊二維碼(或者長按識別二維碼)關註個人微信訂閱號

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/8305925.html