談及此部分,多多少少有一定的難度,筆者寫下這篇文章,差不多是在學習FPGA一年之後的成果,儘管當時也是看過類似的文章,但是都沒有引起筆者註意,筆者現在再對此知識進行梳理,也發現了有很多不少的收穫。筆者根據網上現有的資源,作進一步的總結,希望能夠有所幫助。 一個不錯的網站,類似於一個手冊,隨時可以去查

談及此部分,多多少少有一定的難度,筆者寫下這篇文章,差不多是在學習FPGA一年之後的成果,儘管當時也是看過類似的文章,但是都沒有引起筆者註意,筆者現在再對此知識進行梳理,也發現了有很多不少的收穫。筆者根據網上現有的資源,作進一步的總結,希望能夠有所幫助。

一個不錯的網站,類似於一個手冊,隨時可以去查詢如何去定義各個時序約束指令怎麼用。http://quartushelp.altera.com/current/mergedProjects/tafs/tafs/tcl_pkg_sdc_ver_1.5.htm

靜態時序分析(STA,static timing analysis),對於STA的理解,可以想象在FPGA的內部好比一塊PCB,FPGA的邏輯陣列好比PCB板上的一些分立元器件,PCB通過導線將具有相關電氣特性的信號相連接,FPGA也需要通過內部連線將相關的邏輯節點導通,PCB上的信號通過任何一個元器件都會產生一定的延時,FPGA的信號通過內部邏輯門傳輸也有一定的延時,PCB信號走線也有延時,FPGA信號走線也有延時,這就帶來了一系列的問題,一個信號從FPGA的一端輸入,經過一定的邏輯處理後從FPGA的另一端輸出,這期間會產生多大的延時呢?有多個匯流排信號從FPGA的一端輸入,這條匯流排的各個信號經過邏輯處理之後從FPGA的另一端輸出,這條匯流排的各個信號的延時一致嗎?之所以關心這些問題,是因為過長的延時或者一條匯流排多個信號傳輸延時的不一致,不僅會影響FPGA本身會給FPGA之外的電路或者系統帶來諸多的問題。

所以針對上面的一系列問題,設計者需要提出一些特定的時序要求,針對現有的電路給出時序約束,

分析時序,本質上是節點對節點之間的時序分析,如果沒有節點,時序也就無從談起。在FPGA中,我們可以把節點當作是寄存器與寄存器之間的時序分析,寄存器與寄存器之間可能還有一些組合邏輯充斥著。所以時序路徑通常有四大類:

(1)寄存器到寄存器類型,即reg2reg;

(2)輸入引腳到寄存器類型,即pin2reg;

(3)寄存器到輸出引腳類型,即reg2pin;

(4)輸入引腳到輸出引腳類型,即pin2pin;

針對上述四種基本時序路徑,最關心的就是數據信號和時鐘鎖存沿之間的建立時間和保持時間的關係。

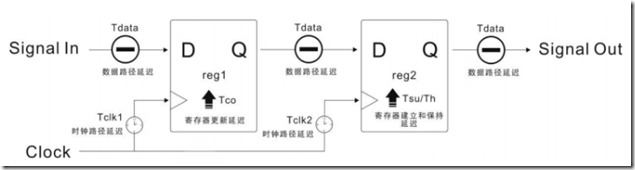

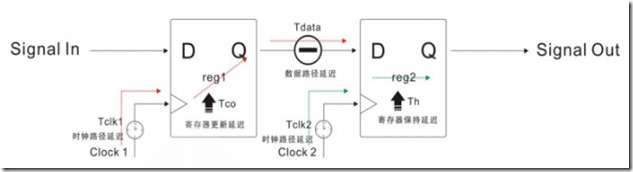

對於四種延時路徑可以用圖1所示,對於signal in,是外部IC到FPGA的輸入信號引腳,一般情況下晶元手冊都會給出各引腳關於時序方面的說明,如Tco、TSU、Th、等信息,這個是在分析時序時會用到。Reg1到reg2之間的時序路徑是相當於在FPGA內部的寄存器到寄存器之間的延時路徑,signal out是相當於FPGA的輸出信號到外部IC之間的引腳信息。

圖1 時序路徑分析

這裡只分析FPGA內部的時序路徑,外部IC的時序路徑需要結合具體的IC數據手冊,然後結合FPGA輸入引腳部分的大概延時進行推測一個值,之後具體再分析。

所以從寄存器1到寄存器2之間的延遲時間的分析。

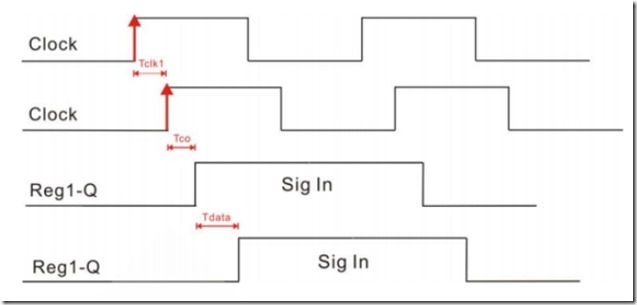

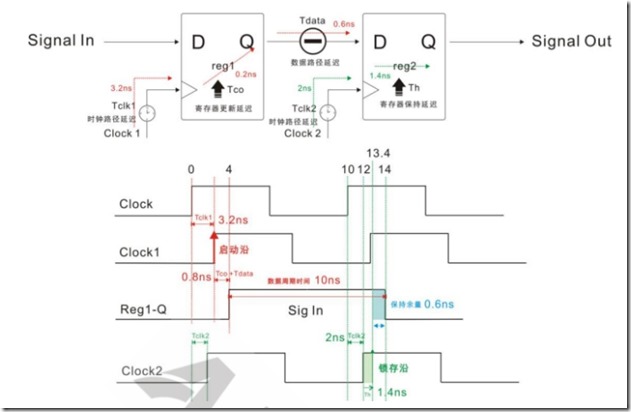

圖16.2 寄存器到寄存器延時

上圖是考慮各種延遲之後的從輸入數據到輸出數據的時間延遲。

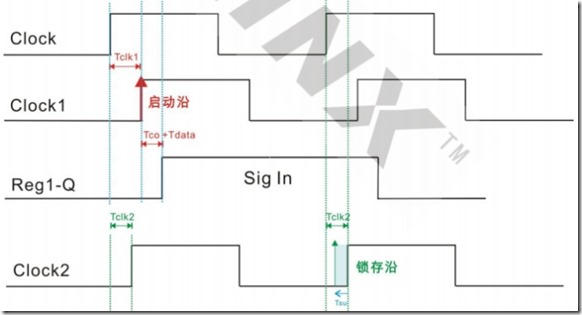

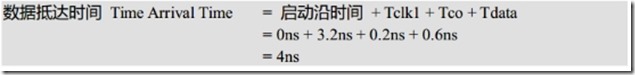

所以我們引入第一個概念:數據抵達時間(官方視頻上面的概念),也就是實際到達時間,

引入第二個概念:數據要求時間

圖16.3 數據要求時間分析

由於有寄存器建立時間的參與,所以會使得數據鎖存時間由下麵的公式決定,但是在應用時Tsu按照負值代入公式,這樣計算的才正確,可能是官方的bug,所以按照負值計算即可。

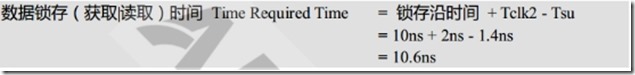

建立餘量

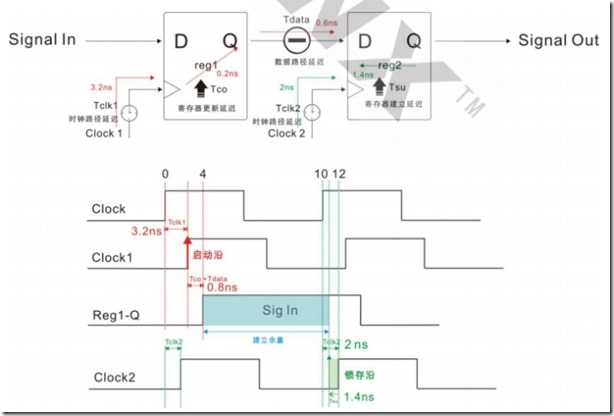

為了說明怎麼計算得到建立餘量,特舉例如下所示。

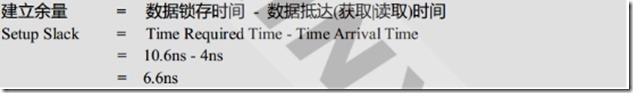

對於公式上面的鎖存沿時間,其實就是啟動沿和鎖存沿之間的差值,也就是建立時間關係,建立時間關係是理想狀態下,啟動沿與鎖存沿之間的距離,如下圖2所示,這個建立時間關係 = 時鐘周期,所以在計算的時候,可以先計算出建立時間關係值,然後也就確定了鎖存沿時間。

圖2 建立時間和時鐘周期的關係

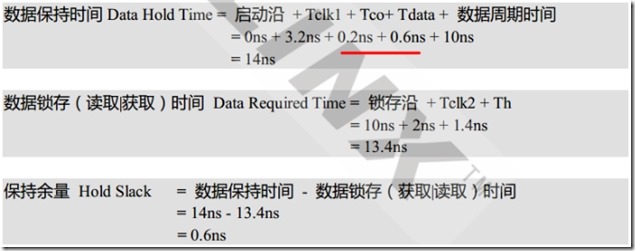

保持餘量

還是用我們的經典的圖來說明保持餘量,那麼數據從寄存器1到寄存器2要經過的時間為

其中數據周期時間,是以時鐘周期為計算值。

根據上圖,用一些數字來計算,如下圖

由此得到了保持餘量值。

//=======================================================================

更多詳細的資料下載可以登錄筆者百度網盤:

網址:http://pan.baidu.com/s/1bnwLaqF

密碼:fgtb

//=======================================================================