時序約束實例詳解 本篇博客結合之前的內容,然後實打實的做一個約束實例,通過本實例讀者應該會實用timequest去分析相關的實例。本實例以VGA實驗為基礎,介紹如何去做時序約束。 首先VGA這種情況屬於供源時鐘情況,不明白供源時鐘的可以參看之前博客講解。首先查看ADV7123的數據手冊,查看其時序圖

時序約束實例詳解

本篇博客結合之前的內容,然後實打實的做一個約束實例,通過本實例讀者應該會實用timequest去分析相關的實例。本實例以VGA實驗為基礎,介紹如何去做時序約束。

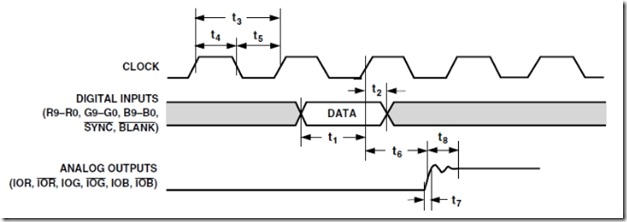

首先VGA這種情況屬於供源時鐘情況,不明白供源時鐘的可以參看之前博客講解。首先查看ADV7123的數據手冊,查看其時序圖。如下圖所示,是建立時間和保持時間要求。

下圖是時序圖,可見t1和t2在時鐘上升沿的位置,數據在時鐘的上升沿進行採集。

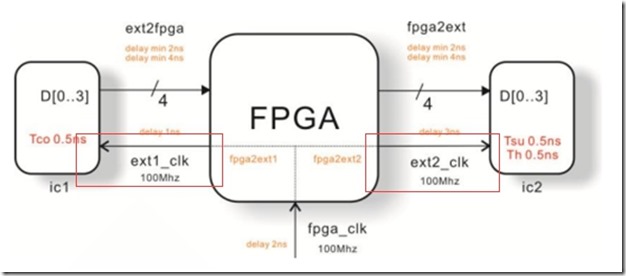

對於VGA實驗來說,FPGA是發送端,ADV7123是接收端,如果傳輸的速率比較高的話,數據和時鐘上升沿的嚴格對齊就要依靠PLL產生可調相位的時鐘信號來保證,不過對於對於25MHz時鐘通過較好的時序約束和分析後,則不必動用PLL。

接下來需要產生虛擬時鐘,對於reg2reg路徑的分析,其時鐘都是FPGA內部,不用產生虛擬時鐘,但是對於pin2reg或者reg2pin這種情況,需要產生一個虛擬時鐘,作為pin端的時鐘來分析時序。如下圖中的標註所示。

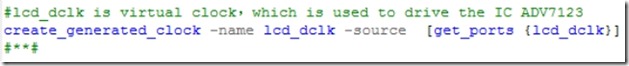

所以ADV7123和FPGA進行時鐘相關的信號就是ADV7123的驅動時鐘,明白這個信號之後,需要設置其虛擬時鐘約束,如下圖所示。

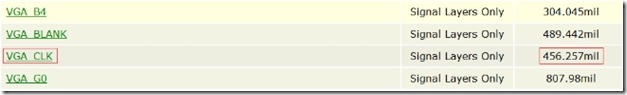

由於FPGA是相對於ADV7123為輸出ADV7123所需要的信號,所以需要設置輸出延遲約束。這一部分結合上一篇博客的分析,首先需要計算FPGA到ADV7123晶元的延遲,這一部分主要是PCB上面的信號走線延時。所以需要結合PCB走線來估計延遲時間。

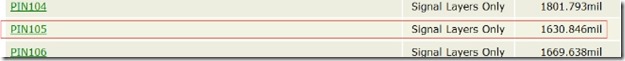

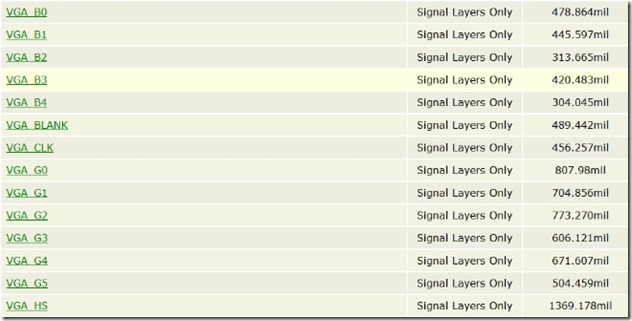

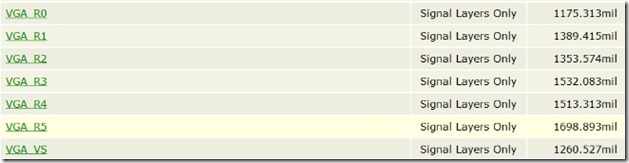

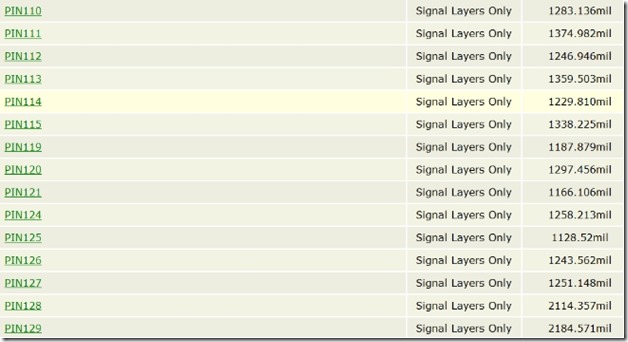

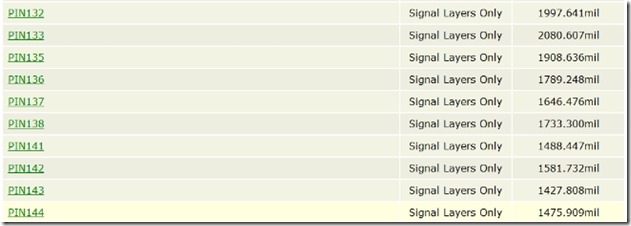

打開altium designer,然後查看VGA模塊的走線長度如下圖1所示,長度大約是11.589mm。

圖1 VGA模塊走線長度

在FPGA核心板(筆者設計的一款學習板)上面的lcd_dclk的走線長度如下圖2所示。長度大約是41.4mm。

圖2 核心板走線長度

根據上述的計算,所以lcd_dclk總得走線長度 = 52.989mm。

同樣的道理,數據走線長度如下圖3所示,此走線長度是VGA模塊上面的長度,長度大約在7.72~43.152mm,那麼對於核心板上面的走線模塊長度如圖4所示,大概長度約為28.65 ~ 53.32mm,總的長度為36.37mm~96.472mm,根據0.17ns/25.4mm,lcd_clk走線延遲0.35ns,數據匯流排延遲0.24ns~0.646ns。

圖3 各信號走線延遲

圖4 核心板各信號走線延遲

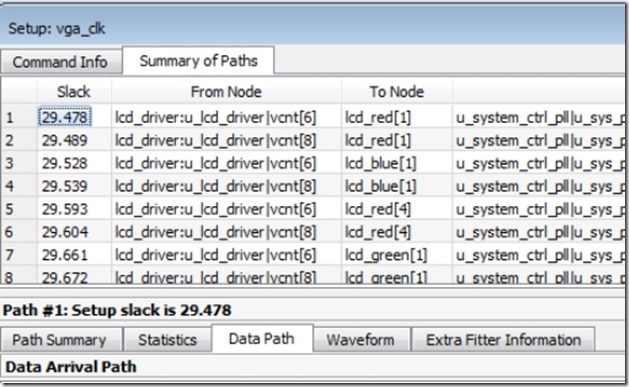

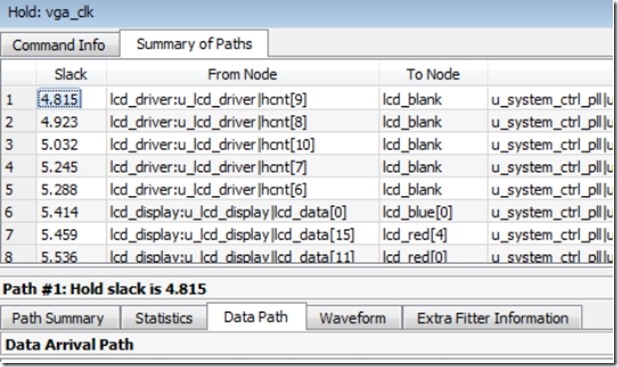

若是不考慮時鐘偏移,那麼進行時序分析得到的餘量如圖5所示。

圖5 建立和保持餘量

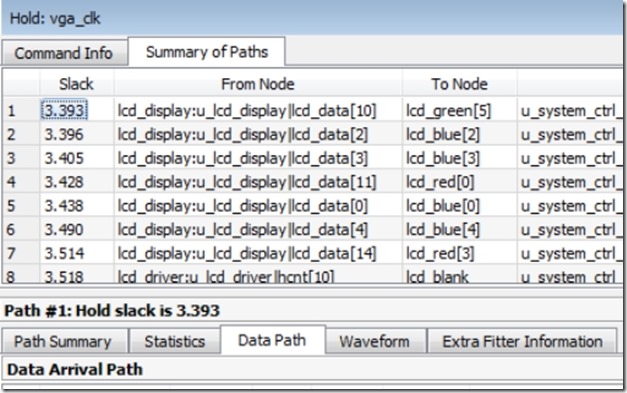

上述是計算完了FPGA到外部IC的延遲,但是還有時鐘偏斜沒有計算,那麼需要用到set max/min delay 命令,對於lcd_dclk先估計一個範圍,如0~5ns即可,這個範圍肯定是滿足要求,但是可能會不能夠留有更多的餘量。然後在將有時鐘偏移的延遲時間代入set output delay的表達式中,此處利用公式將lcd_dclk 最大延遲設為3ns,lcd_dclk最小延遲設為1ns,那麼考慮時鐘偏斜的輸出最大值 = 0.646 + 0.2 -3 = -2.154ns;輸出最小值 = 0.24 - 1.5 - 1 = -2.26ns;

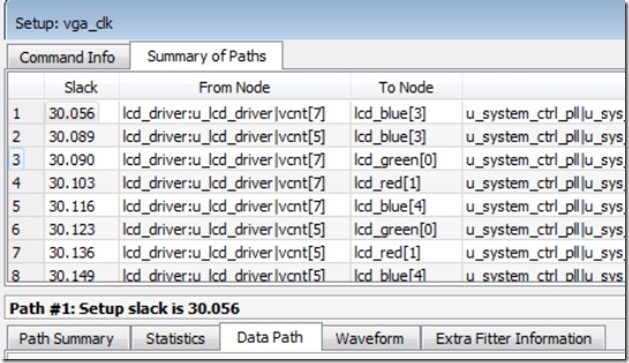

圖6是約束後的建立餘量和保持餘量,可以看到滿足時序要求,並保有很大的時序餘量。

圖6 建立餘量和保持餘量

//=======================================================================

更多詳細的資料下載可以登錄筆者百度網盤:

網址:http://pan.baidu.com/s/1bnwLaqF

密碼:fgtb

//=======================================================================