大家在寫程式的時候,可能會聽聞,什麼獨熱碼,什麼格雷碼,什麼二進位碼等等,本節意在解釋這幾種編碼之間的區別和優勢以及用verilog怎麼去實現,下麵先介紹這幾種編碼的區別。1 基礎理論部分1.1 獨熱碼 獨熱碼,在英文文獻中稱做 one-hot code, 直觀來說就是有多少個狀態就有多少比特,而....

大家在寫程式的時候,可能會聽聞,什麼獨熱碼,什麼格雷碼,什麼二進位碼等等,本節意在解釋這幾種編碼之間的區別和優勢以及用verilog怎麼去實現,下麵先介紹這幾種編碼的區別。

1 基礎理論部分

1.1 獨熱碼

獨熱碼,在英文文獻中稱做 one-hot code, 直觀來說就是有多少個狀態就有多少比特,而且只有一個比特為1,其他全為0的一種碼制。

如,有十六個狀態的獨熱碼狀態編碼應該是:0000000000000001,0000000000000010,0000000000000100,0000000000001000,0000000000010000,0000000000100000 ,……,10000000000000000。但是通常我們為了方便書寫,將二進位簡化為十六進位表示(從右往左每四位二進位位用一位十六進位數表示),那麼,以上十六狀態的獨熱碼可以表示成0x0001, 0x0002, 0x0004, 0x0008, 0x0010, 0x0020, ……, 0x8000。

1.2 格雷碼

在一組數的編碼中,若任意兩個相鄰的代碼只有一位二進位數不同,則稱這種編碼為格雷碼(Gray Code),另外由於最大數與最小數之間也僅一位數不同,即“首尾相連”,因此又稱迴圈碼或反射碼。

1.3 二進位碼

二進位代碼:由兩個基本字元'0'、'1'組成的代碼。其中,碼元:"一位"二進位代碼。碼字:N個碼元可以組成的不同組合,任意一個組合稱一個碼字。

1.4 二進位編和格雷碼利弊

二進位編碼、格雷碼編碼使用最少的觸發器,消耗較多的組合邏輯,而獨熱碼編碼反之。獨熱碼編碼的最大優勢在於狀態比較時僅僅需要比較一個位,從而一定程度上簡化了解碼邏輯。雖然在需要表示同樣的狀態數時,獨熱編碼占用較多的位,也就是消耗較多的觸發器,但這些額外觸發器占用的面積可與解碼電路省下來的面積相抵消。

由於CPLD更多地提供組合邏輯資源,而FPGA更多地提供觸發器資源,所以CPLD多使用gray-code,而FPGA多使用one-hot編碼。另一方面,對於小型設計使用gray-code和binary編碼更有效,而大型狀態機使用one-hot更高效。

關於獨熱碼,我們在使用狀態機的時候,會詳細解釋。為了更進一步說明二進位碼和格雷碼之間的關係,可以查看下圖12.1。

方法一:

圖12.1 二進位碼與獨熱碼

上述的方法可以稱為遞歸法,從0~7的高位都是0,後8~15的高位都是1,那麼由二進位怎麼去實現格雷碼,如下圖12.2所示。

方法二:適合於編程實現

圖12.2 計算格式

也即對原位進行移位,然後和原位進行求抑或操作。

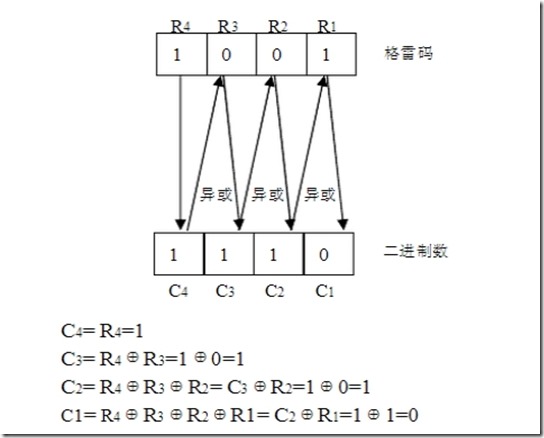

那麼格雷碼怎麼去實現二進位呢?且看下圖12.3解釋:

圖12.3

由上圖可以分析得出,最高位是保持不變的,然後以後每一位都要和前幾位進行求異或操作。下麵我們就用verilog來實現。

2 Verilog代碼實現部分

2.1 二進位轉格雷碼

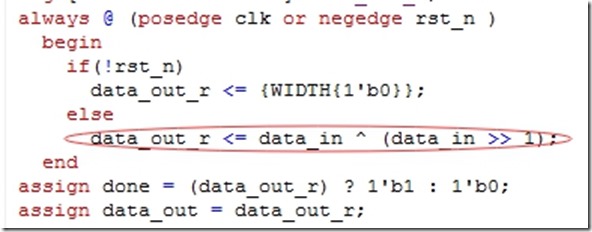

講解最重要的代碼部分,如圖12.4

圖12.4 代碼實現部分

最重要的代碼一行搞定。請大家看懂。

2.2 格雷碼轉二進位

讓大家感受一下FPGA的並行的魅力,重要代碼如圖12.5所示,利用FPGA的並行加速,可以實現其他CPU不能比擬的速度。

圖12.5 轉換實現部分

3 Modelsim模擬部分

部分重要代碼如圖12.6所示

圖12.6 模擬程式

將輸入數據封裝成一個任務,然後在initial中直接調用任務即可,但要註意,data_init為輸入數據的初始化,一定要放在task_reset複位信號的前面,這一點不容忽視。

圖12.7為binary2gray模擬的波形。

圖12.7 模擬波形

關於板級模擬,大家可以去利用四位LED或者數位管去實現,這裡不再贅述。

圖12.8為testbench代碼部分,gray2binary

圖12.8 代碼實現部分

圖12.9為gray2binary模擬的波形

圖12.9 模擬波形