1基礎理論部分 VGA(video graphics array)即視頻圖形陣列,是IBM在1987年隨PS/2一起推出的使用模擬信號的一種視頻傳輸標準。VGA相比與現在的視頻傳輸介面來說已經過時,不過作為最低標準,基本上製造商都會接入此介面,圖11.1是常見的VGA介面。圖11.1 VGA介面 對...

1基礎理論部分

VGA(video graphics array)即視頻圖形陣列,是IBM在1987年隨PS/2一起推出的使用模擬信號的一種視頻傳輸標準。VGA相比與現在的視頻傳輸介面來說已經過時,不過作為最低標準,基本上製造商都會接入此介面,圖11.1是常見的VGA介面。

圖11.1 VGA介面

對於VGA15個引腳的相關說明,如下圖所示。

圖11.2 VGA引腳說明

大家做實驗的時候,可能會有一個誤區,那就是做實驗時直接把實驗板的VGA介面接到筆記本電腦上,還興高采烈的等待著顯示圖像,殊不知筆記本電腦是不能作為普通顯示器顯示的。

現在的顯示器介面已經經過VGA,DVI(數字信號的傳輸),到現在的HDMI介面標準,實現數字高清影音傳輸的技術,因此最新的顯示器基本上都會支持這幾種介面。

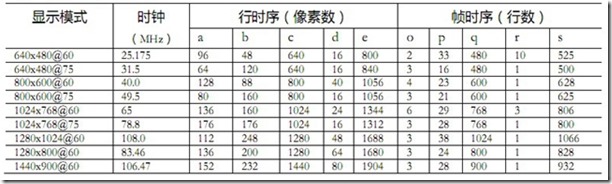

更多的時序標準,請參考http://tinyvga.com/vga-timing

由三原色RGB所組成的顏色種類,由RGB888(24位真彩色),RGB565,RGB444;(本實驗所採用的是RGB565),對於帶寬有限,圖像要求不是特別高,這個RGB565已經可以滿足要求了。對於RGB565模型,位的分配,由高到低,分別為R 15..11,G 10..5, B 4..0;

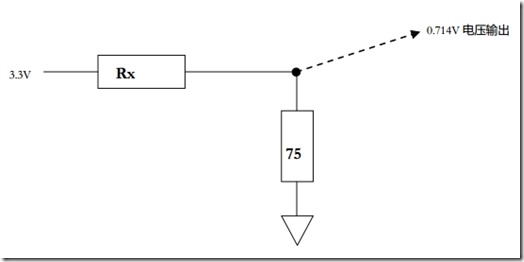

對於VGA的介面模擬電壓,為0~0.714V,0代表無色,0.714代表滿色,FPGA輸出3.3V,所以還必須要經過DAC的轉換。這些部分在做板子的時候,會繼續補充、基本上現在成熟的方案,採用R-2R或者ADV7123。當然專用晶元成像質量很好。

對於顯示器而言,VGA的解析度越高,意味著顯示的圖像越清晰,包含信息也越多,畫質更加好,圖像更加保真。由於人眼的視覺暫留,要想實現顯示器的不閃爍,至少需要實現每秒25幀畫面的更新。通常顯示器的掃描頻率都在60幀及以上。

對於顯示器而言,有的可以相容多個解析度模式,為了實現這種方式,許多顯示器具有scaler功能,能夠實現不同解析度的相容。

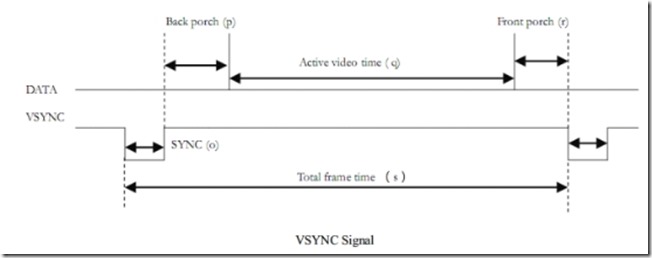

圖11.2 場同步信號

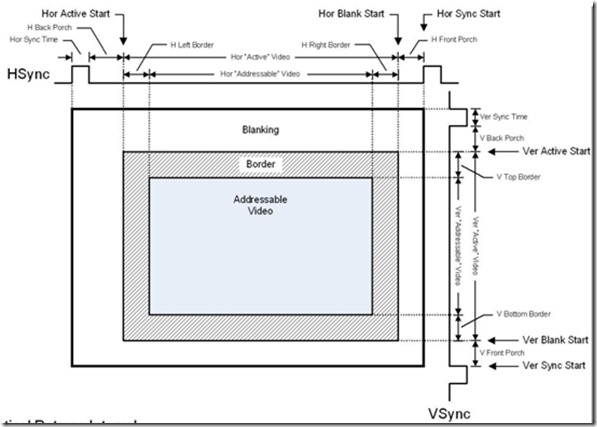

圖11.3 行和場信號工作方式

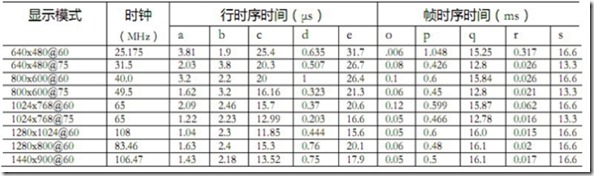

圖11.4 常見的刷新時序表

1.2 VGA驅動電路部分

現在主要的用於VGA驅動電路的方案,一個是採用電阻R-2R的形式,一個是採用專用晶元,這兩者各有優勢。

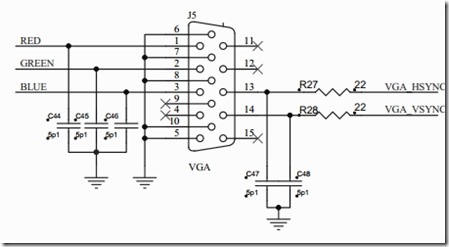

對於VGA來說,有幾路信號比較重要,RED,GREEN, BLUE信號,以及hsync 和vsync信號,其中hsync 和vsync信號可以直接和FPGA的IO口相連,但是rgb信號卻不能,它需要0~0.714V模擬信號。

1.2.1 R-2R結構

圖11.5 拓撲結構

上圖是視頻DAC拓撲結構模式,根據上述模式計算Rx的值。

那麼大概得到Rx = 271.6387Ω;

![]() 解出

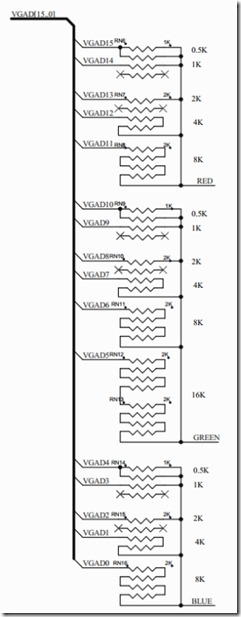

解出![]() ,所以我們採用Ra = 500Ω,可以選中1K和2K的電阻去串並聯實現R-2R模型。這裡是採用2K和1K串並聯的方式實現5—6—5 ,即16位格式。

,所以我們採用Ra = 500Ω,可以選中1K和2K的電阻去串並聯實現R-2R模型。這裡是採用2K和1K串並聯的方式實現5—6—5 ,即16位格式。

圖11.7 VGA介面部分電路

圖11.8 R-2R電路

1.2.2 專用晶元結構

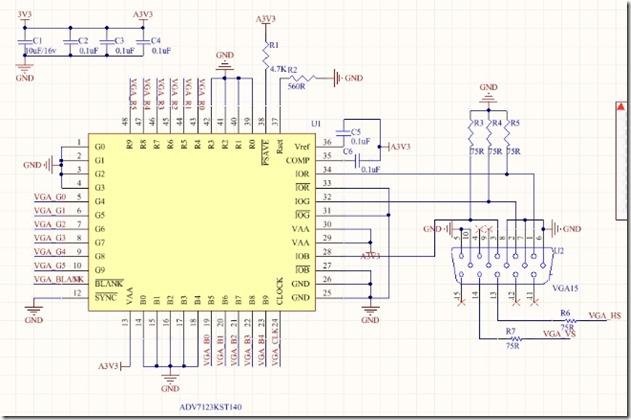

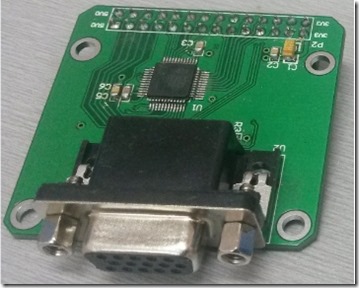

對於專用晶元去用於視頻操作的,我們常用ADV7123。此款晶元最大採樣率為330MHz,低功耗,3路10位DAC視頻轉換器。圖11.9是原理圖部分,圖11.10是實物圖。

圖11.9 ADV7123原理圖

圖11.10 VGA實物圖

2 Verilog代碼實現部分

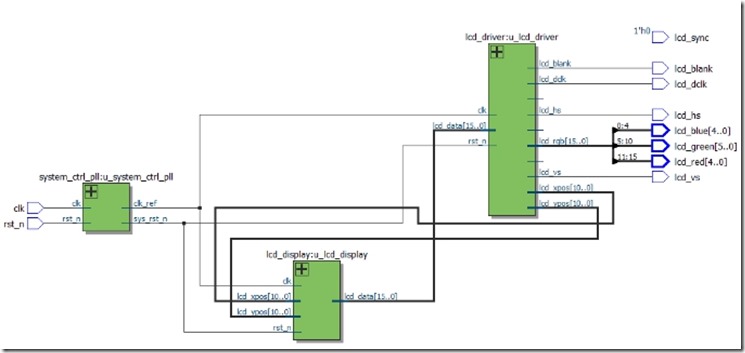

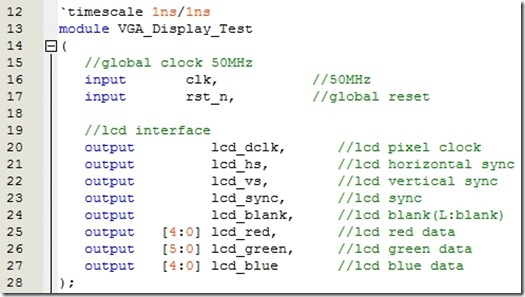

本次實驗實現彩條測試功能,板卡載有一顆ADV7123晶元,FPGA驅動該晶元並產生VGA所需要的行和場信號,圖11.11是RTL視圖。

圖11.11 RTL視圖

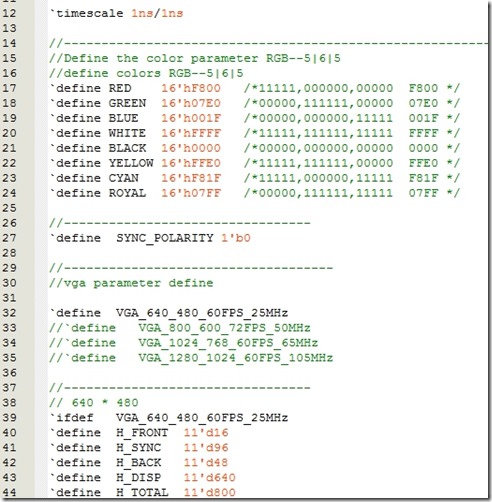

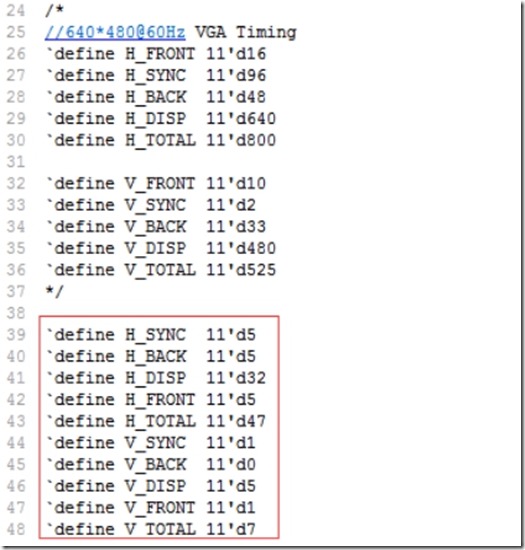

在lcd_para.v文件中定義了彩條各參數和VGA所需要的行和場信號所需要的像素數,這裡利用了define和 ifdef指令,註意其用法。

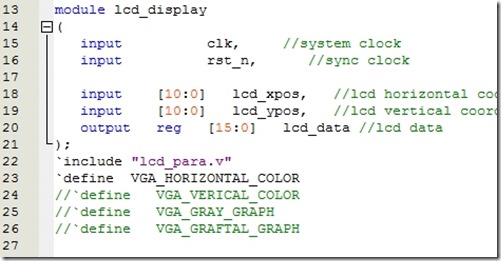

在lcd_display.v中,將lcd_para.v文件進行調用,且在23行到26行有幾種測試實驗,一種是水平彩條,一種是豎直彩條,灰度圖以及紋理圖。

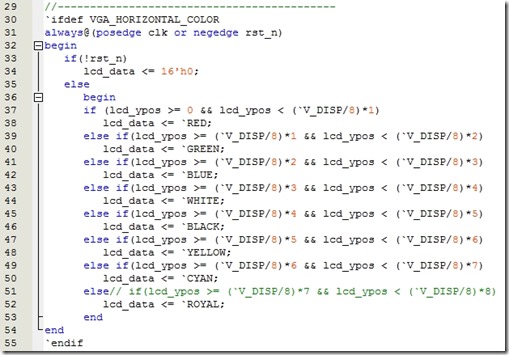

上述就是具體每一種測試實驗所對應的生成程式。

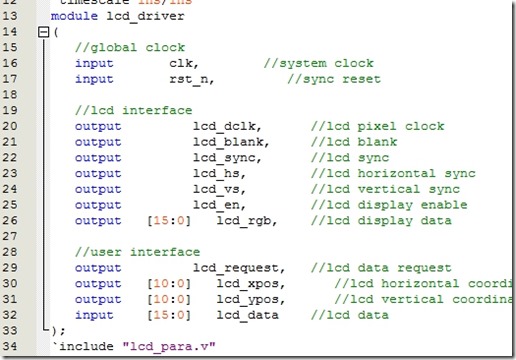

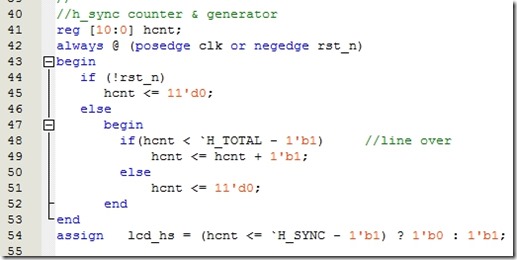

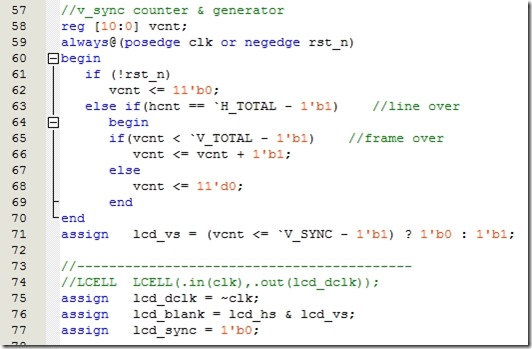

在lcd_driver.v中,生成驅動ADV7123的信號和產生VGA所需要的16位數據,以及在lcd_display.v中所需要的x和y坐標值。

行信號的生成部分。

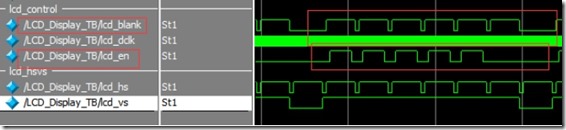

場信號生成部分,75行到77行是AD7123所需要的信號,可以看到驅動是非常簡單的。這裡75行ADV7123的驅動時鐘和主時鐘相反,以此來達到在主時鐘的上升沿對數據進行採樣。

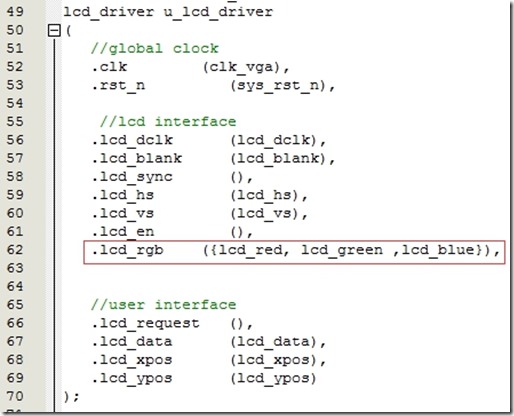

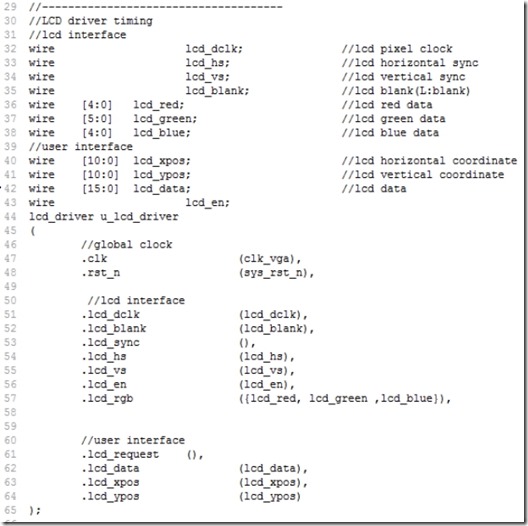

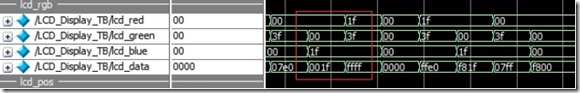

上述是對總的模塊進行例化部分,註意25行到27行,由於ADV7123晶元需要RGB的格式為565,所以定義lcd_red,lcd_green,以及lcd_blue。

註意62行是對剛纔定義的RGB信號的分配,由於lcd_rgb是16位數據,分別將高5位送給lcd_red,將中6位送給lcd_green,將低五位送給lcd_blue。

3 Modelsim模擬部分

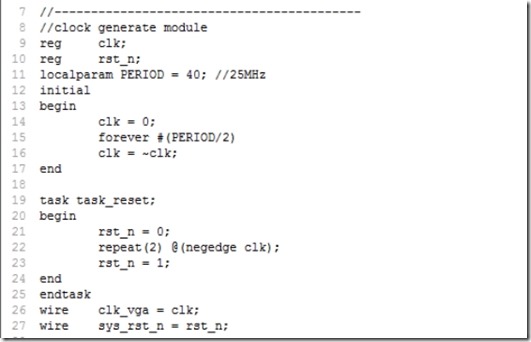

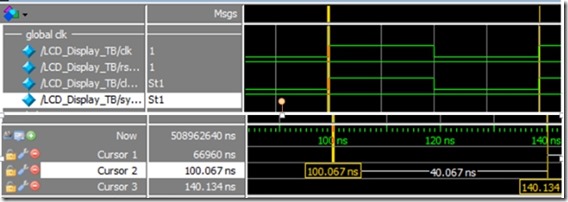

上述是testbench中的時鐘模擬信號和複位模擬信號的產生,其中11行是模擬25MHz時鐘。

註意上述模擬時調用的模塊名,因為我們想觀察到各個信號的輸出情況,所以只調用重要的兩個模塊lcd_driver和lcd_display即可,32行到43行是對調用模塊的各個輸出信號的聲明,這裡也可以看到,需要觀察輸出什麼樣的信號,只需定義為wire類型即可,前提是調用各個模塊時,wire定義的變數必須是相對於輸出的信號。

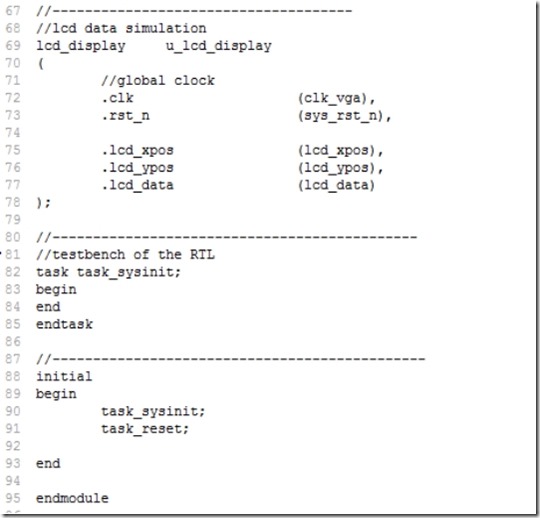

69行到78行是對lcd_display模塊進行的例化。82行到85行是對輸入信號的初始化,外部輸入信號暫時沒有,所有沒有初始化任何信號。

另外為了節省模擬時間在lcd_driver中將各參數適當縮小,以達到縮減模擬時間的目的,如下麵所述。

3.1 模擬波形

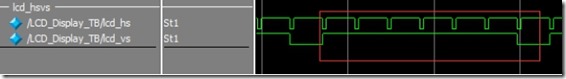

圖11.11是時鐘的模擬波形,時鐘信號周期40ns,滿足25MHz。圖11.12是行和場信號的模擬,可以看到6個行信號,1個場信號。這和之前的VGA時序分析是一致的。圖11.13是lcd_en信號和lcd_blank信號,這兩個信號都和行和場信號有關。圖11.14是RGB數據模擬出的波形

圖11.11 時鐘信號模擬

圖11.12 行和場模擬信號

圖11.13 使能和空白信號

圖11.14 RGB輸出的波形