嵌入式技術基礎與實踐 學習札記(一) KL系列MCU簡介與體繫結構概述 該系列是業內首款基於$ARM\ Cortex M0+$內核的$MCU$,具有超低功耗、應用設計方便、擴展性好、系列品種齊全等特點。$KL$系列$MCU$面向家用電器、攜帶型醫療系統、智能電錶、照明、電源、電機控制及工業控制系 ...

嵌入式技術基礎與實踐-學習札記(一)

KL系列MCU簡介與體繫結構概述

該系列是業內首款基於\(ARM\ Cortex-M0+\)內核的\(MCU\),具有超低功耗、應用設計方便、擴展性好、系列品種齊全等特點。\(KL\)系列\(MCU\)面向家用電器、攜帶型醫療系統、智能電錶、照明、電源、電機控制及工業控制系統等。\(KL\)系列的主要特點如下最高工作頻率\(48MHz\)、支持直接存儲器訪問\(DMA\),位操作引擎\(BME\)、內核單周期訪問記憶體速度可達\(1.77CoreMark/MHz\)、單周期訪問\(I/O\)、關鍵外設速度比標準\(I/O\)最大提高\(50\%\);\(2\)級流水線設計減少了指令周期數\(CPI\),提高跳轉指令和執行\(ISR\)中斷服務常式速度;與\(8\)位,\(16\)位\(MCU\)相比具有更精簡的代碼密度,減少\(Flash\)空間、系統資源及功耗;更精簡的指令系統優化訪問程式存儲空間,完全相容\(ARM\ Cortex-M0\),相容\(Cortex-M3/M4\)指令集子集。

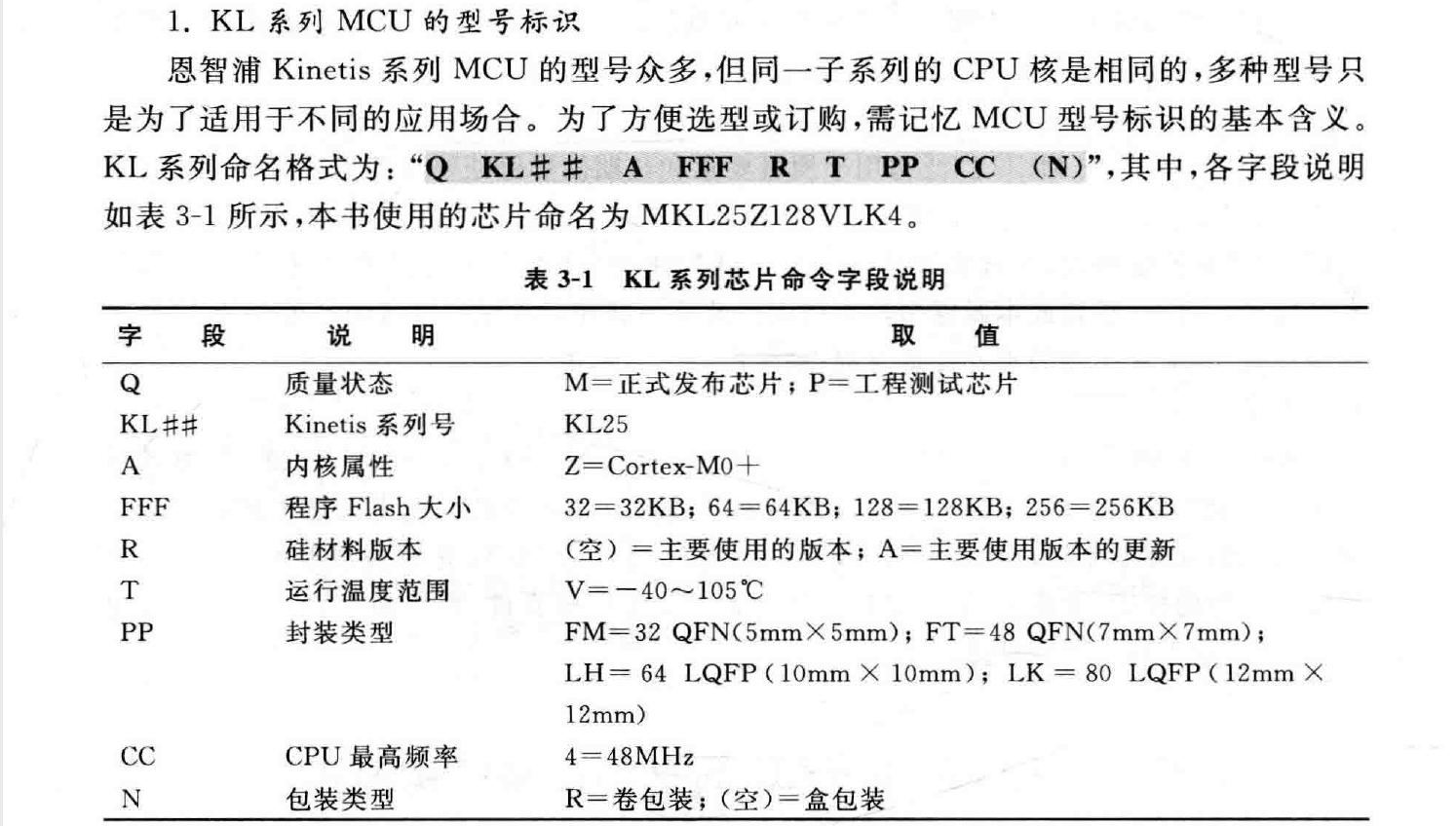

KL系列MCU的型號標識

KL系列MCU體繫結構概述

\(KL\)系列\(MCU\)是以\(AMBA\)匯流排規範為架構的片上系統,如圖所示:

KL25系列存儲映像與中斷源

KL25系列存儲映像

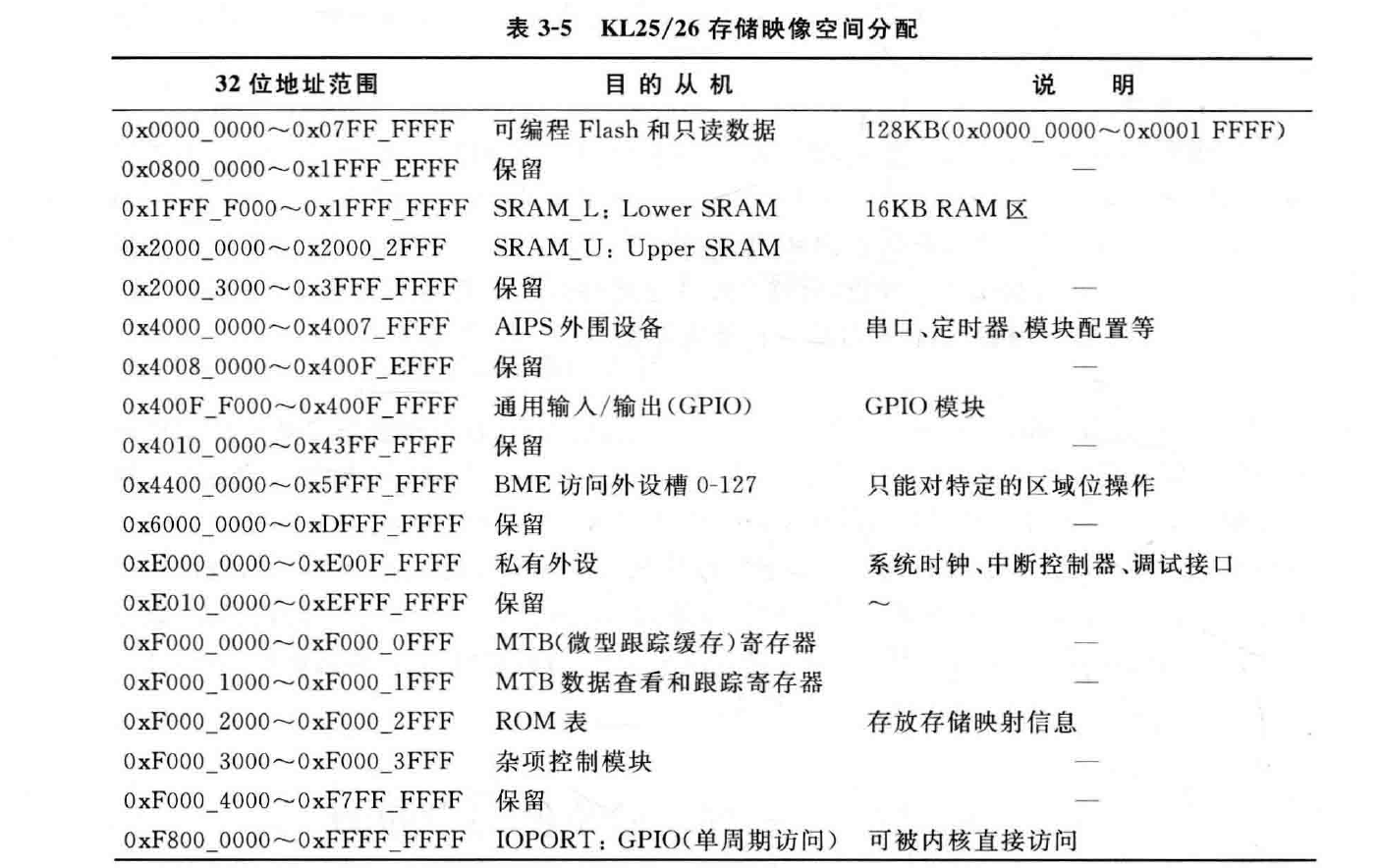

所謂存儲映像在這裡可以直觀地理解為\(M0+\)定址的\(4GB\)地址空間\((0x000\_0000\sim 0xFFFF\_FFFF)\)被如何使用,都對應了哪些實際的物理介質。下麵利用\(GPIO\)模塊來闡述有關的概念。

\(GPIO\)模塊使用了\(0x400F\_F000\sim 0x400F\_FFFF\)地址空間,這些空間內的\(GPIO\)寄存器與\(CPU(即M0+內核)\)內部寄存器(如\(R0,R1\)等)不同,訪問\(GPIO\)寄存器需要使用直接地址進行訪問,也就是說需要使用三匯流排(地址匯流排,數據匯流排,控制匯流排)。而訪問\(CPU\)內部寄存器,不需要經過三匯流排(彙編語言直接使用\(R0,R1\)等名稱即可),沒有地址問題。由於訪問\(CPU\)內部寄存器不經過三匯流排,所以比訪問\(GPIO\)寄存器來的快。為區別\(CPU\)內部寄存器,\(GPIO\)寄存器也被稱為“映像寄存器”\((Mapping\ Register)\),相對應的地址被成為“映像地址”\((Mapping\ Address)\)。整個可直接定址的空間被稱為“映像地址空間”\((Mapping\ Address Space)\)。

對於此表,主要記住片內\(Flash\)區及片內\(RAM\)區存儲映像。因為中斷向量、程式代碼、常數放在片內\(Flash\)中,源程式編譯後的鏈接階段需要使用的鏈接文件中需含有目標晶元\(Flash\)的地址範圍及用途等信息,才能順利生成機器碼。鏈接文件中還需包含\(RAM\)的地址範圍及用途等信息,以便生成機器碼確切定位全局變數、靜態變數的地址及堆棧指針。

\(KL25\)片內\(Flash\)大小為\(128KB\),地址範圍是\(0x0000\_\sim 0x0001\_FFFF\),一般被用來存放中斷向量,程式代碼,常數等,其中前\(192B\)為中斷向量表。

\(KL25\)片內\(RAM\)為靜態隨機存儲器\(SRAM\),大小為\(16KB\),地址範圍\(0x1FFF\_F000\sim 0x2000\_2FFF\),一般被用來存儲全局變數、靜態變數、臨時變數(堆棧空間)等。

KL25中斷源

中斷是電腦發展中一個重要的技術,它的出現很大程度上解放了處理器,提高了處理器的執行效率。所謂中斷,是指\(MCU\)在正常運行程式時,由於\(MCU\)內核異常或者\(MCU\)各模塊發出請求事件,引起\(MCU\)停止正在運行的程式,而轉去處理異常或執行處理外部事件的程式。

內核中斷主要指異常中斷,非內核中斷又稱可屏蔽中斷,這類中斷通過編程式控制制,開啟或關閉該中斷。

中斷向量序號是每一個中斷源的固定編號,由晶元設計產生時決定,編程時不能更改,它代表了中斷服務程式入口地址在中斷向量表的位置。\(IRQ\)中斷號是非內核中斷源的編號,每一個編號代表一個非內核中斷源。

KL25的引腳功能

\(MCU\)的硬體最小系統是指包括電源、晶振、複位、寫入調試器介面等可使內部程式得以運行的、規範的、可復用的核心構件系統。電路中需要大量的電源類引腳用來提供足夠的電流容量同時保持晶元電流平衡,所有的電源引腳必須外接適當的濾波電容抑制高頻雜訊。

硬體最小系統引腳

GPIO及程式框架

通用I/O

所謂通用\(I/O\),也記為\(GPIO(General\ Purpose\ I/O)\),即基本輸入/輸出,有時也稱並行\(I/O\),或普通\(I/O\),它是\(I/O\)的最基本形式。作為通用輸入引腳,\(MCU\)內部程式可以通過埠寄存器獲取該引腳狀態。作為通用輸出引腳,\(MCU\)內部程式通過埠寄存器控制該引腳狀態。

上拉下拉電阻的基本接法

埠控制模塊

\(KL25\)的大部分引腳具有復用功能,可以通過埠控制模塊提供的寄存器編程指定其為某一具體功能。

\(PORT\)模塊內含三類寄存器,分別是引腳控制寄存器\((Pin\ Control\ Register)\),全局引腳控制寄存器\((Global\ Pin\ Control Register)\)、中斷狀態標誌寄存器\((Interrupt\ Status\ Flag\ Register)\)。

\(KL25\)晶元有\(5\)個埠\(A\sim E\),每個埠有\(32\)個引腳控制寄存器\(PORTx\_PCRn\)(其中\(x=A\sim E,n=0\sim 31\)),兩個全局引腳控制寄存器\((PORTx\_GPCLR、PORTx\_GPCHR)\),一個中斷狀態標誌寄存器\(PORTx\_ISFR\)。

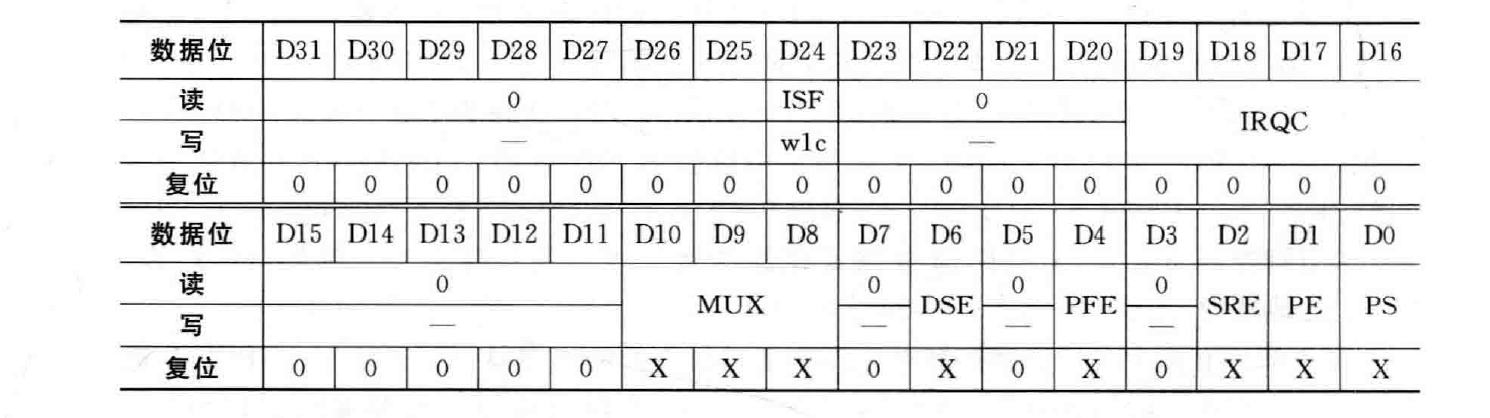

引腳控制寄存器

引腳復用控制欄位,它決定引腳復用何種功能。

每個埠都有\(32\)個引腳控制寄存器\(PORTx\_PCRn\)。埠\(x\)的每個引腳控制寄存器\(PORTx\_PCRn=\) \(=4004\_9000+x\times1000+n\times 4(x=A\sim E,對應0\sim 4,n=0\sim 31)\)。

其中,\(X\)表示覆位後狀態不確定。下麵給出相關功能說明,未說明的位或者欄位為保留(只讀,值為\(0\))。

\(D24(ISF)\)——中斷狀態標誌(只讀)。數字引腳模式下有效。\(ISF=0\),未檢測到引腳中斷;\(ISF=1\),檢測到引腳中斷。向該位寫\(1\),可清楚中斷狀態標誌。若引腳配置為\(DMA\)請求方式,在完成\(DMA\)請求傳輸後,將自動清楚中斷狀態標誌。如果引腳被配置為電平觸發的中斷,引起中斷的電平若一直有效,該標誌將一直保持置位,即使被清楚後也會立即置位。

\(D19\sim D16(IRQC)\)——中斷配置情況(讀/寫)。數字引腳模式下有效。\(IRQC=0000\),關閉引腳中斷\(/DMA\)請求;\(IRQC=0001\sim 0011\)分別對應上升沿、下降沿、沿跳變、觸發\(DMA\)請求;\(0100\)保留;\(1000\sim 1100\)分別對應邏輯低電平(邏輯\(0\))、上升沿,下降沿,沿跳變、高電平(邏輯\(1\)),觸發引腳中斷。其他值保留。特別註意:不是所有\(KL25\)的引腳均可配置為中斷功能,只有\(A,D\)口的引腳具有上述這種中斷功能。

\(D10\sim D8(MUX)\)——引腳復用控制(讀/寫)。不是所有引腳都支持引腳復用槽。\(MUX=000\),引腳不配置(模擬引腳);\(MUX=001\),配置引腳為通用輸入輸出\((GPIO)\)功能;\(MUX=010\sim 111\),分別配置引腳的功能為第\(2\)到第\(7\)功能(具體功能見晶元參考手冊\(10.3\)節)。

\(D6(DSE)\)——驅動能力使能位(讀/寫)。表名引腳被配置為數字輸出時的驅動能力狀況,數字引腳模式下有效。\(DSE=0\),低驅動能力;\(DSE=1\),高驅動能力。由數據手冊可知\(KL25\)低驅動能力是\(5mA\),高驅動能力是\(18mA\)。但並不是所有引腳都可配置為高驅動能力。

\(D4(PFE)\)——無源濾波使能位(讀/寫)。數字引腳模式下有效。\(PFE=0\),相應的引腳禁止無源輸入濾波;\(PFE=1\)。

\(D2(SRE)\)——轉換速率使能位(讀/寫)。數字引腳模式下有效。\(0\)——引腳配置成快轉換速率。\(1\)——引腳配置成慢轉換速率。

\(D1(PE)\)——上拉或下拉使能位(讀/寫)。數字引腳模式下有效。\(0\)——相應的引腳關閉內部上拉或下拉電阻;\(1\)——相應的引腳啟用內部上拉或下拉電阻,引腳最為數字輸入。

\(D0(PS)\)——上拉或下拉選擇(讀/寫)。數字引腳模式下有效。\(PS=0\),如果\(PE=1\),引腳下拉電阻使能;\(PS=1\),如果\(PE=1\),引腳上拉電阻使能。\(KL25\)內部上下拉電阻大小為\(20\sim 50k\Omega\)。

全局引腳控制寄存器

每個埠有兩個全局控制引腳寄存器,為只寫寄存器。全局引腳控制寄存器(低)\(PORTx\_GPCLR\),地址\(=4004\_9080+x\times 1000\);全局引腳控制寄存器(高)\(PORTx\_GPCHR\),地址\(=4004\_9084+x\times 1000\)。

每個寄存器的高\(16\)位被稱為全局引腳寫使能欄位\(GPWE\),低\(16\)位被稱為全局引腳寫數據欄位\(GPWD\)。若\(GPWE=0xFFFF\),則\(GPWD\)欄位的\(16\)位就被寫入到一整組引腳控制寄存器的低\(16\)位中。

中斷狀態標誌寄存器

每個埠都有一個中斷狀態標誌寄存器\(PORTx\_ISFR\),地址\(=4004\_90A0+x\times 1000\)。

數字引腳模式下,每個引腳的中斷模式可以獨立配置,在引腳控制寄存器\(IRQC\)欄位可配置選擇。

每個埠的中斷狀態標誌寄存器,對應該口的\(32\)個引腳,相應為\(1\),表明配置的中斷已經被檢測到,反之沒有。各位具有寫\(1\)清\(0\)特性。

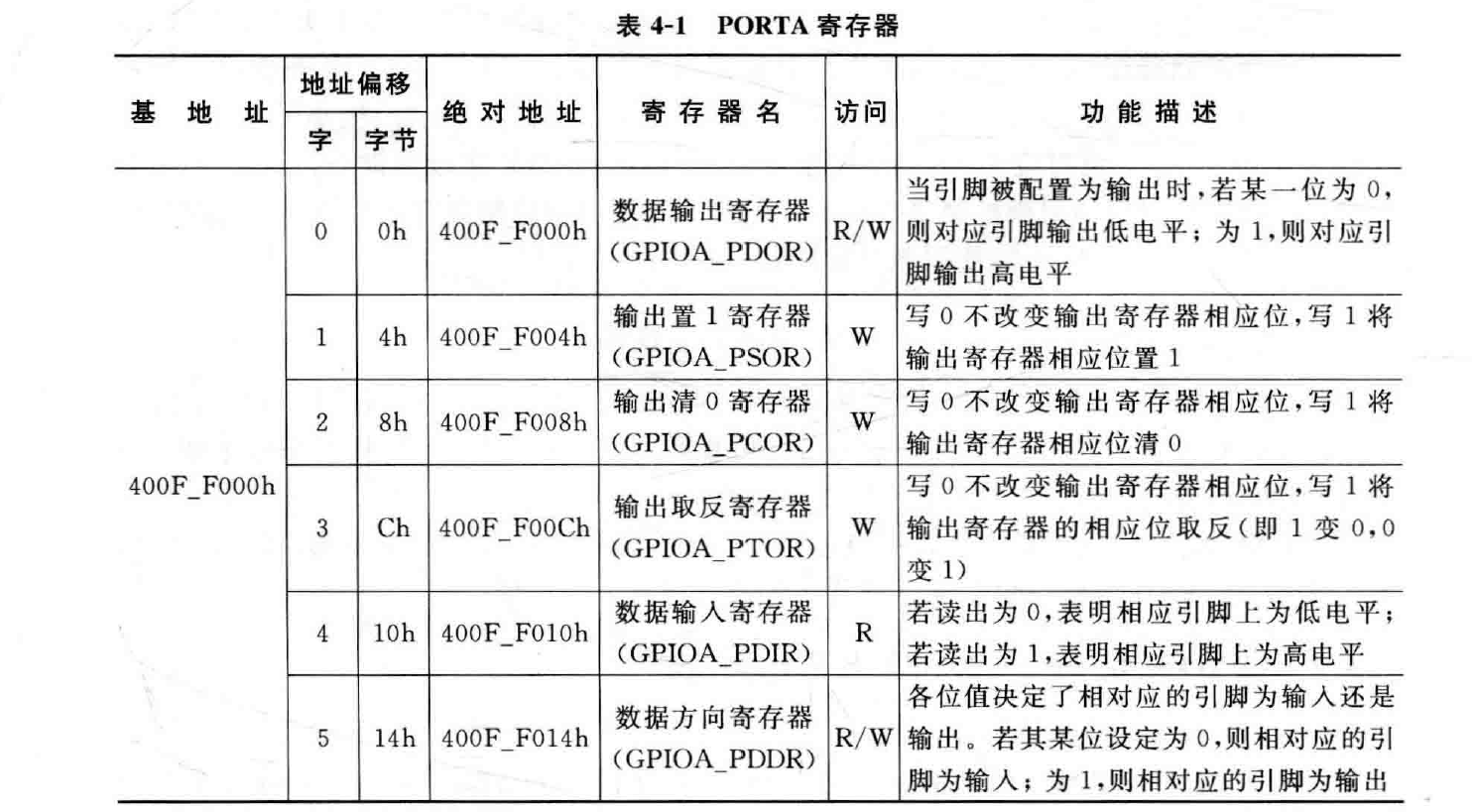

GPIO模塊——對外引腳與內部寄存器

\(80\)引腳封裝的\(KL25\)晶元的\(GPIO\)引腳分為\(5\)個埠,標記為\(A、B、C、D、E\),共含有\(61\)個引腳。

每個\(GPIO\)埠均有\(6\)個寄存器,\(5\)個\(GPIO\)埠共有\(30\)個寄存器。 \(A、B、C、D、E\)各口寄存器基地址分別為\(400F\_F000h、400F\_F040h、400F\_F0080h、400F\_F0C0h、400F\_F100h\),所以各口基地址相差\(40h\)。\(PORTx=400F\_F000+x\times 40\)。每個寄存器有\(32\)位,對應\(32\)個引腳輸入輸出模式。

GPIO基本編程步驟

- 通過埠控制模塊的引腳控制寄存器\(PORTx\_PCRn\)的引腳復用欄位\((MUX)\)設定其為\(GPIO\)功能(即令\(MUX=001\))。

- 通過\(GPIO\)模塊相應埠的“數據方向寄存器”來指定相應引腳為輸入或輸出功能。若指定位為\(0\),則對應引腳為輸入;若指定位為\(1\),則對應引腳輸出。

- 若是輸出引腳,則通過設置“數據輸出寄存器”來指定相應引腳輸出低電平或高電平。也可通過其他寄存器實現。

- 若是出入引腳,則通過“數據輸入寄存器”獲得引腳的狀態。

需要進一步說明的是,這樣編程只是為了理解\(GPIO\)的基本編程方法,實際並不使用,實際要把底層硬體的操作用構件把它們封裝起來,給出函數名與介面參數。