1、概述 i.MX 6ULL系列晶元的MMDC是一個多模式DDR控制器,支持DDR3/DDR3Lx16和LPDDR2x16的存儲類型,MMDC是可配置,高性能,優化的記憶體控制器。 註:DDR3/DDR3Lx16、LPDDR2x16 ,此處的x16表示晶元位寬,每個傳輸周期能夠提供的數據量(bit)。 ...

1、概述

i.MX 6ULL系列晶元的MMDC是一個多模式DDR控制器,支持DDR3/DDR3Lx16和LPDDR2x16的存儲類型,MMDC是可配置,高性能,優化的記憶體控制器。

註:DDR3/DDR3Lx16、LPDDR2x16 ,此處的x16表示晶元位寬,每個傳輸周期能夠提供的數據量(bit)。也就是說明,如果要提供32位的位寬記憶體存儲,需要2顆以上型號的記憶體進行並聯使用。

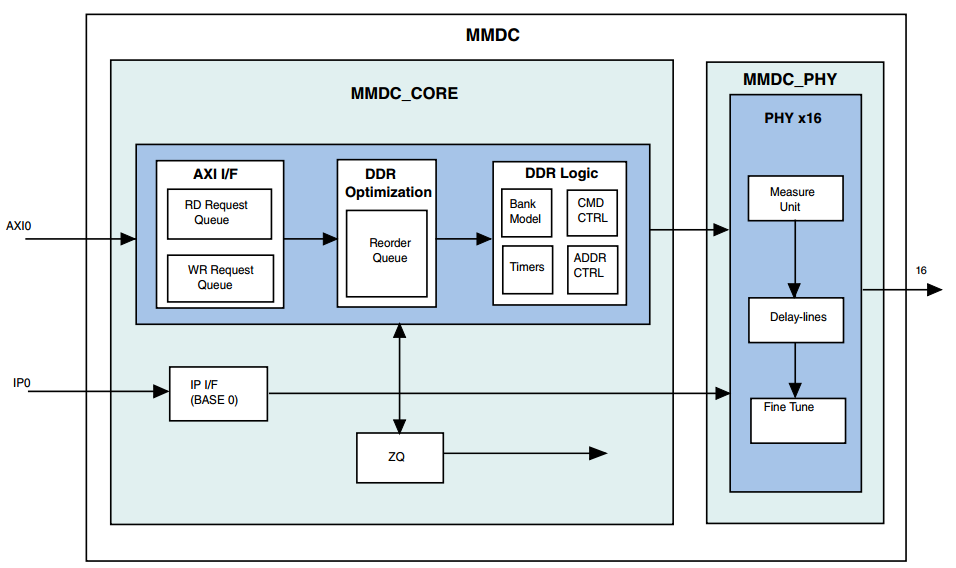

下麵是MMDC邏輯框圖:

- MMDC由內核(MMDC_CORE)和物理層(MMDC_PHYl)兩部分構成。

- 內核負責通過AXI介面,DDR命令發生器,DDR命令優化器,和讀寫數據通道與系統通信,物理層負責定時調整,它使用特殊校準機制確保數據獲取400MHz的時鐘頻率。

- MMDC的內部配置寄存器通過IP通道進行配置。

DDR標準:

- DDR3L,DDR3x16 LPDDR2x16

- 不支持LPDDR1MDDR 和DDR2

DDR介面:

- 16位數據匯流排寬度;

- 器件密度-256Mbits-8Gbits,其中列8-12bit,行11-16bit;

- 通過配置CS0,CS1可以達到4Gbyte地址空間;

- DDR3支持的突髮長度為8;

- LPDDR2支持的突髮長度為4;

DDR性能:

- 400MHz核心頻率,800MHz數據頻率

- 支持實時優先順序,支持不同優先順序的重新排序機制:實時,延時敏感,正常優先順序

- 頁面碰撞錯過優化

- 連續讀寫訪問優化

- 支持深度讀寫請求隊列,支持bank預測

- 支持bank交叉

- ddr3模式下(突髮長度)的非對齊換行訪問情況下的特殊優化

AXI介面:

- 運行在400MHz,支持傳輸8/16/64 bits(單一訪問和突發)

- 支持最大突髮長度為16

- 支持16bits AXI ID

DDR通用設置:

- 可配置時序參數

- 可配置刷新周期

- 支持頁邊界交叉

- 支持LPDDR2 MRW和MRR指令

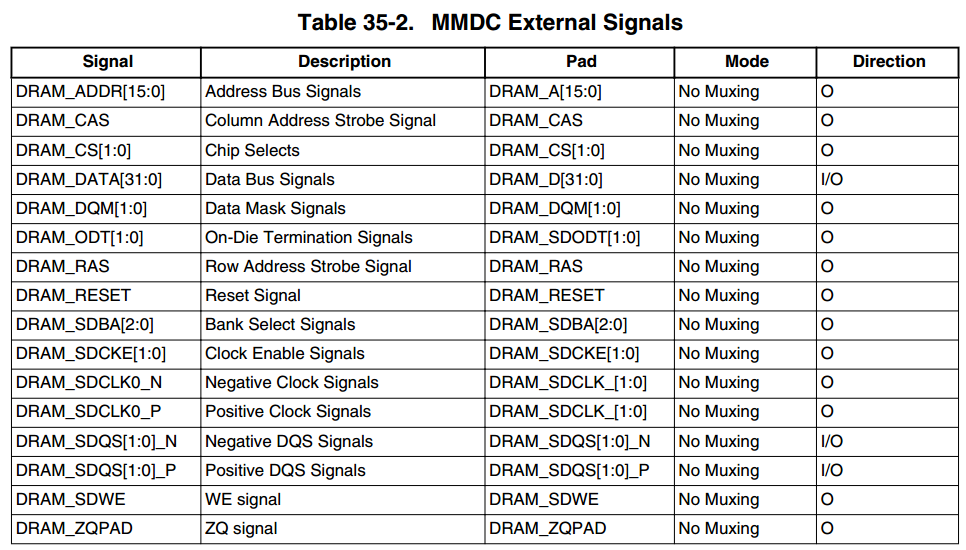

2、外部介面信號

3、時鐘源

時鐘設置參考CCM(clock controller module)模塊

4、功能性說明

4.1 讀/寫數據流

4.2 MMDC初始化

4.3 配置MMDC寄存器

4.4 MMDC地址空間

4.5 LPDDR2與DDR3引腳復用映射

4.6 節能和時鐘切換模式

4.7 複位

4.8 刷新計劃

4.9 用於DDR的突髮長度選項

4.10 獨家訪問處理

4.11 AXI錯誤處理

5、性能

5.1 仲裁和重新排序機制

5.2 預測機制

5.3 針對DDR3訪問的特殊優化

6、MMDC 調試

7、 MMDC 剖析

8、LPDDR2刷新率更新和定時減量

9、DLL切換

10、ODT配置

11、校準過程

12、MMDC 記憶體映射/寄存器定義

參考資料:

https://blog.csdn.net/u011124985/article/details/81140819

IMX6ULLRM.pdf——恩智浦提供下載

https://baike.baidu.com/item/%E5%86%85%E5%AD%98%E6%9D%A1