學習目的: (1) 熟悉Altera FPGA的PLL的四種工作模式,同時掌握鎖相環的工作原理; (2) 掌握PLL IP核的配置過程及使用方法; (3) 掌握ROM IP核的配置過程及初始化方法,學會用MATLAB產生mif文件來初始化ROM。 學習過程: 【PLL的四種模式】 ① PLL的源同步...

學習目的:

(1) 熟悉Altera FPGA的PLL的四種工作模式,同時掌握鎖相環的工作原理;

(2) 掌握PLL IP核的配置過程及使用方法;

(3) 掌握ROM IP核的配置過程及初始化方法,學會用MATLAB產生mif文件來初始化ROM。

學習過程:

【PLL的四種模式】

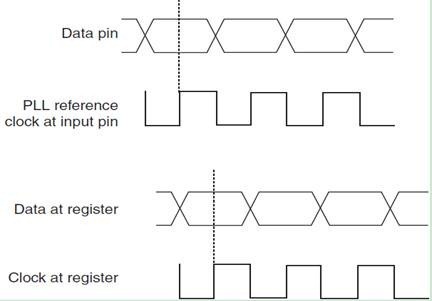

① PLL的源同步模式

特點:在PLL的作用下,從輸入管腳到寄存器,時鐘信號與數據信號的相位差一直保持不變,即:從最開始PLL參考時鐘源從輸入管腳引入,數據源從data管腳引入,它們兩的相位差與時鐘信號和數據信號達到寄存器端時刻的相位差是相同的。因此,這種一般在做埠或介面的時候使用(如:FPGA與其他外部晶元埠對埠通信時需要用到這種模式)。

圖1 源同步模式

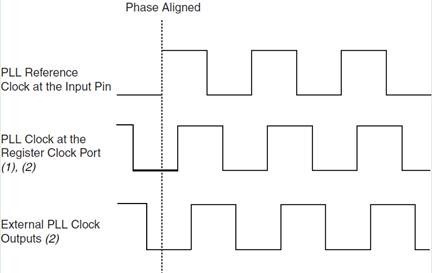

② PLL的零補償模式

特點:因PLL對時鐘信號沒有補償調節,故到達寄存器端的時鐘信號和輸出給FPGA外部使用的時鐘信號都沒能保持相位差的一致性。因此,這種模式一般不被使用。

圖2 零補償模式

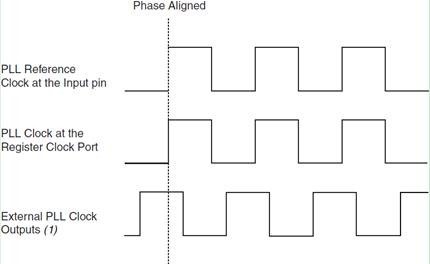

③ 普通模式

特點:在PLL的作用下,PLL時鐘源輸入管腳處的時鐘信號與寄存器端的時鐘信號保持相位一致,而與PLL輸出給FPGA外部用的時鐘信號的相位則不一致,後者與前兩者存在一些相位差。因此,這種模式可用在FPGA內部,但一般不將時鐘輸出給FPGA外部使用。

圖3 普通模式

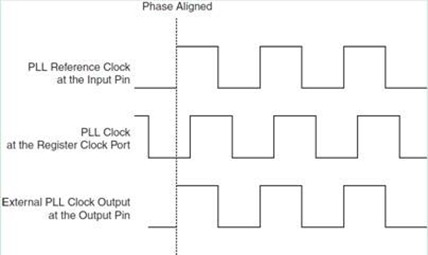

④ 零延時緩衝模式

特點:它與普通模式恰好相反,在PLL的作用下,PLL時鐘源輸入管腳處的時鐘信號與PLL輸出給FPGA外部使用的時鐘信號保持相位一致,而與寄存器端的時鐘信號存在相位差。因此,這種模式一般用作FPGA給外部送時鐘信號用。

圖4 零延時緩衝模式

PLL一般不設置複位(應取消areset和自動複位),複位容易造成失鎖;

PLL一般要設置locked輸出端,用於調試的時候查看PLL是否失鎖。

【PLL的基本原理】

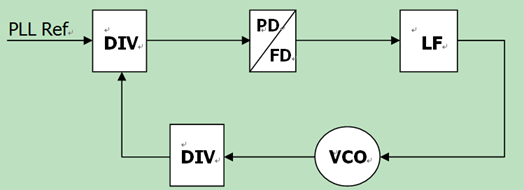

圖5 鎖相環PLL的原理框圖

圖6 鎖相環的工作原理示意圖

如圖5所示,PLL由DIV(分頻器)、PD/FD(鑒相器/鑒頻器)、LF(低通濾波器)以及VCO(壓控振蕩器)等部分組成,PLL Ref是鎖相環的參考輸入時鐘信號,VCO有一個初始的振蕩頻率,通過設置兩個DIV的分頻繫數可以達到PLL分頻或倍頻的效果。FPGA的PLL IP核配置步驟如下:

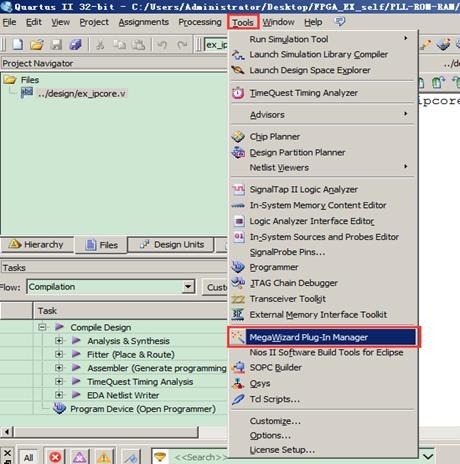

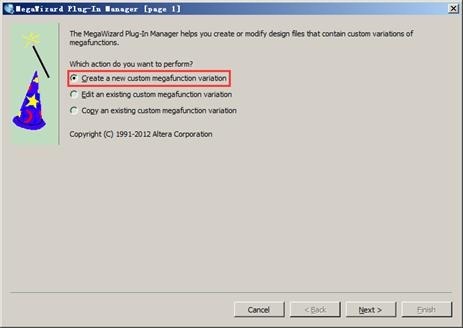

① 建工程,然後創建一個定製型的IP巨集模塊:

圖7 步驟①

圖8步驟①

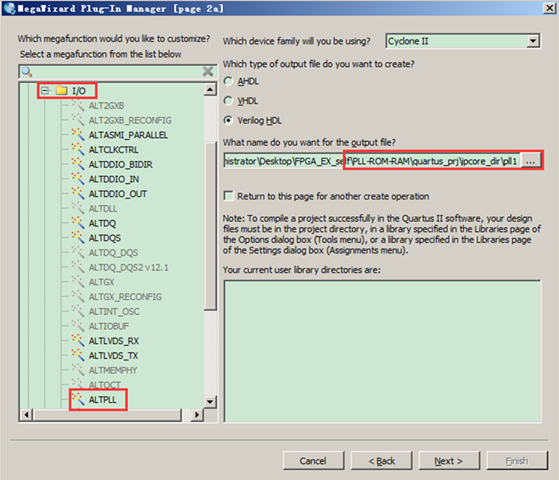

② 在I/O中選擇ALTPLL,指定IP核輸出文件的存放路徑和名稱,同時在quartus_prj目錄下創建ipcore_dir文件夾,用於存放IP核輸出文件(ISE會自動創建這個文件夾,但quartus不會自動創建它)。

圖9步驟②

③ 配置PLL的速度等級、輸入參考時鐘的頻率、工作模式等參數(速度等級的數值越大,則速度越慢;輸入參考時鐘頻率設為50MHz,工作模式設為普通模式):

圖10 步驟③

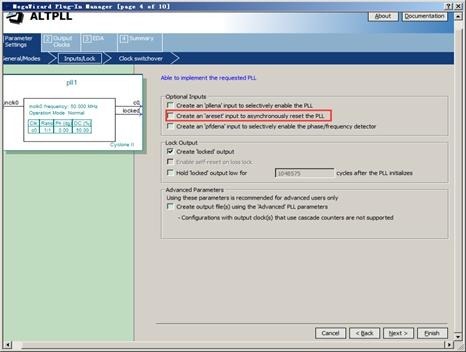

④ 取消非同步複位的配置:

圖11 步驟④

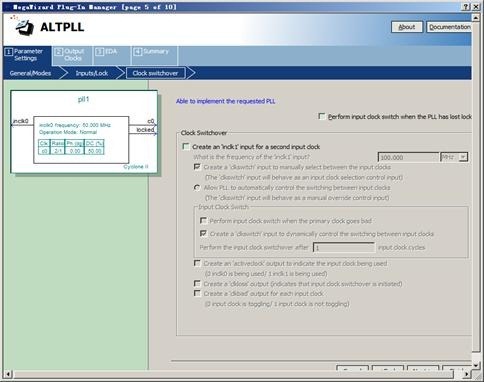

⑤ 預設操作:

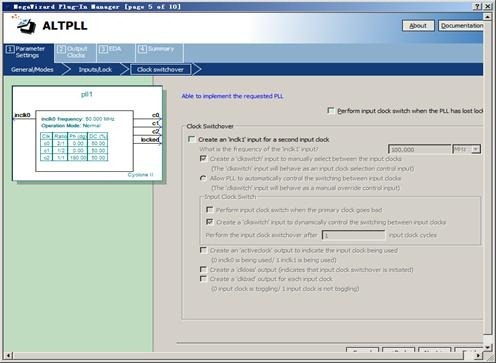

圖12 步驟⑤

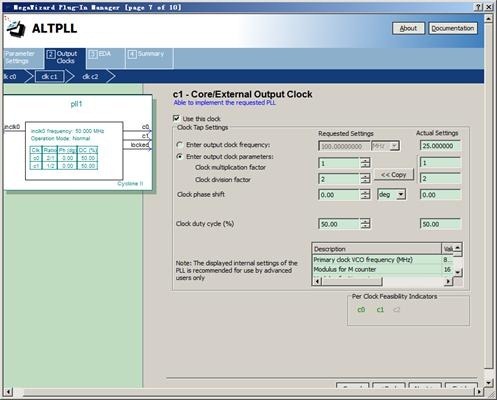

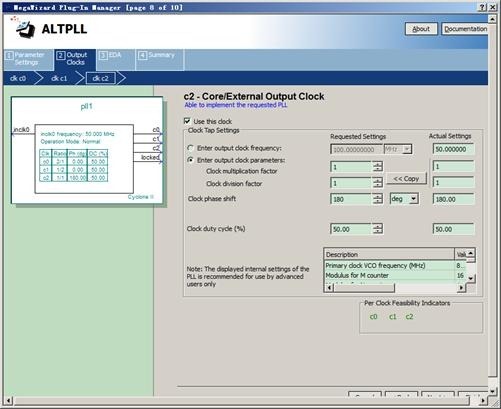

⑥ 設置clk c0、clk c1、clk c2(設置PLL輸出信號的參數):

圖13 clk c0的設置(2倍頻、零相移、50%占空比)

圖14 clk c1的設置(2分頻、零相移、50%占空比)

圖15 clk c2的設置(50MHz、相移180°、50%占空比)

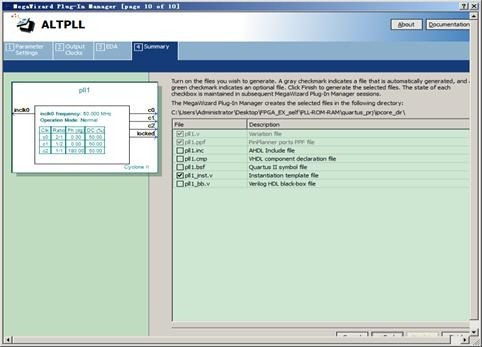

⑦ 預設操作、選擇要生成的.v例化文件(去掉pll1_bb.v選項、勾選pll1_inst.v選項):

圖16

圖17

圖18 設置產生pll1_inst.v例化文件

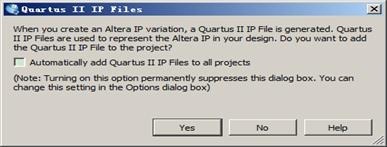

圖19 將IP巨集文件加入到當前工程中

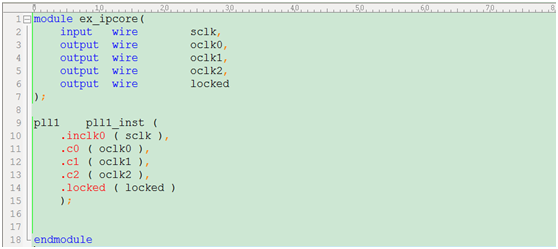

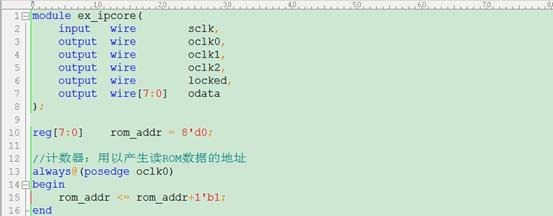

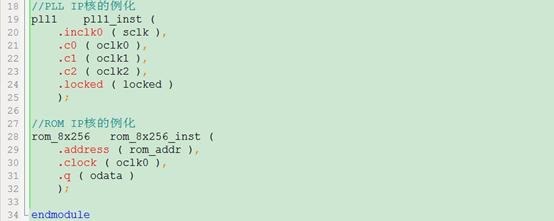

⑧ IP核的例化(將產生的例化文件pll1_inst.v中的內容拷貝到頂層模塊ex_ipcore.v中去,並修改信號名稱)

⑨ 編寫頂層模塊ex_ipcore.v中的代碼(註意IP核模塊的輸出信號只能聲明為wire型,不能聲明為reg型,如:此例中的oclk0、locked等)

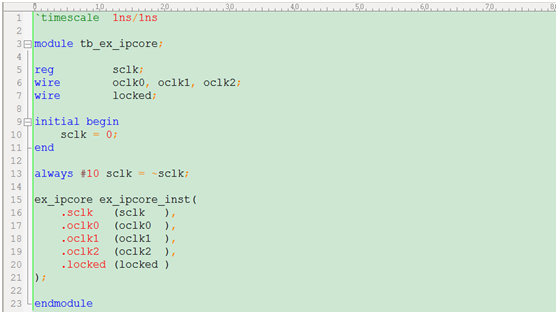

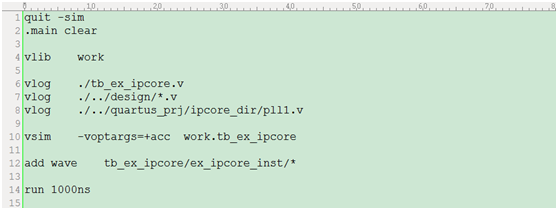

⑩ 編寫測試腳本和run.do文件

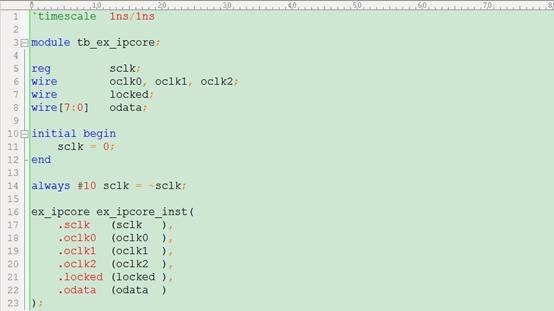

Testbench文件:

run.do文件:

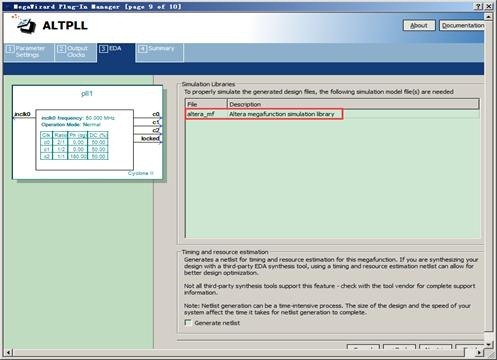

⑪ 添加altera_mf模擬庫文件

在模擬工程目錄下新建文件夾altera_lib,然後從quartus的安裝目錄D:\Quartus II12.1\altera\quartus\eda\sim_lib下拷貝altera_mf.v文件到剛新建的文件夾下(C:\Users\Administrator\Desktop\FPGA_EX_self\PLL-ROM-RAM\sim\altera_lib)。

⑫ 新建Modelsim工程,然後進行模擬

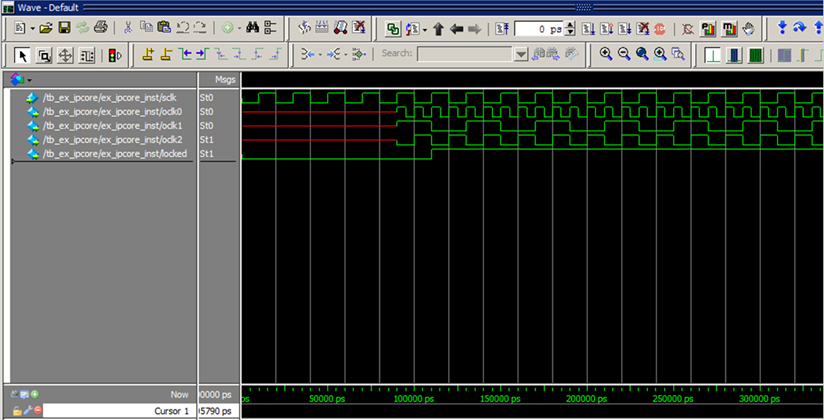

⑬ 模擬結果

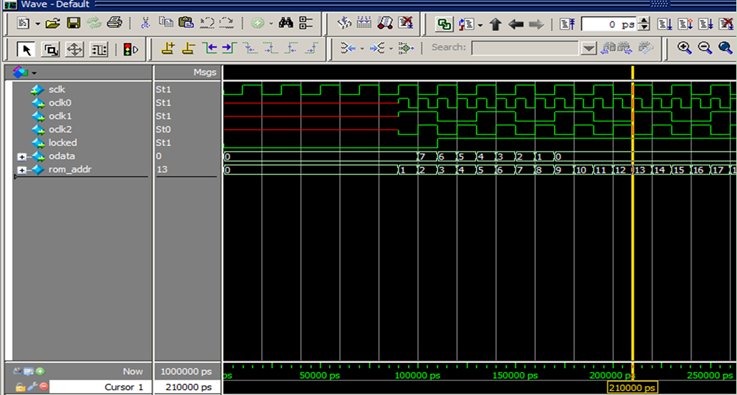

圖20 模擬波形圖

由圖20可知,oclk0的頻率為100 MHz,是sclk的兩倍;oclk1的頻率為25 MHz,是sclk的1/2;oclk2的頻率為50 MHz,與sclk正好反相(相移180°)。有此可見,它們與PLL設置中情況一致,達到了設計的目的。

【註意】因為佈線用線質量的不同(PLL用的是金線),所以不建議使用自己寫的計數器進行分頻,只建議使用PLL分頻倍頻。

【ROM】

ROM的用途:數據緩存(即:跨時鐘域的處理)。

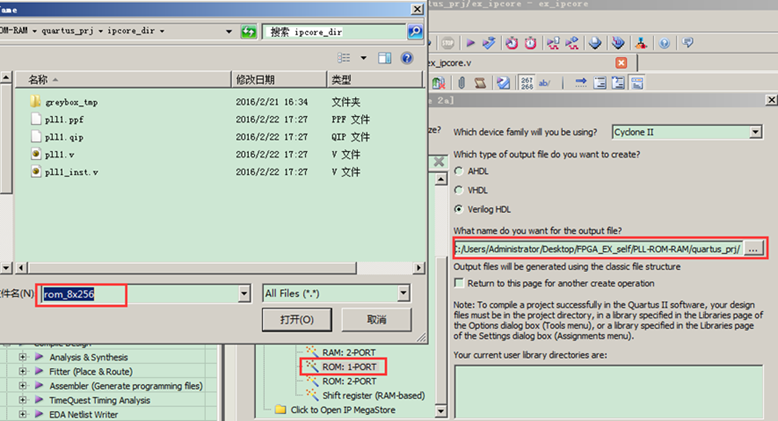

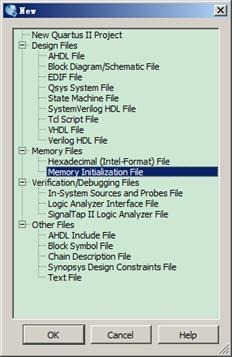

① 新建ROM IP核,輸出文件命名為rom_8x256:

圖21 新建ROM的IP核

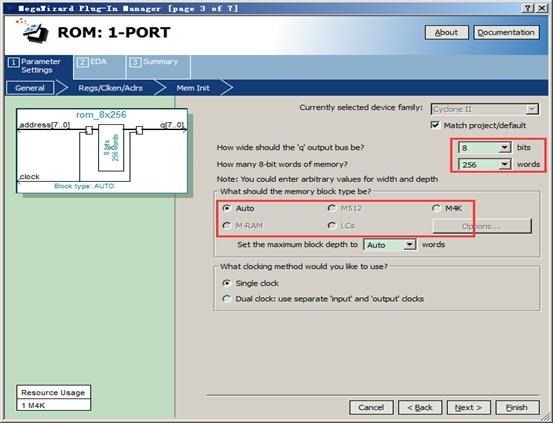

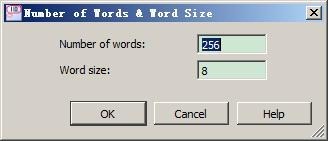

② 配置ROM的IP核模塊的參數:

圖22 配置ROM IP核模塊的參數

如圖22所示,設置輸出位寬為8bit,設置存儲深度為256,M4K是ROM的一個基本存儲單元,可以用FPGA晶元的Embedded Memory數(單位:Kbits)除以4得出該FPGA晶元內部包含多少個M4K的Memory,這裡設置ROM存儲塊的類型為auto。可以設置為雙時鐘的方式(寫入是一個時鐘,輸出是另外一個獨立的時鐘,用於跨時鐘域操作)。

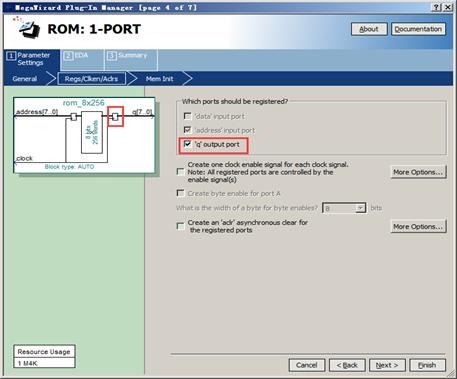

③ 在ROM的q端加寄存器,可提高電路的時序質量和頻率

圖23 在q端加寄存器

圖24 加寄存器的效果

【在q端加寄存器能提高電路的頻率】如圖24所示,在中間加了寄存器之後,截斷兩級電路之間的延遲(10ns)為5ns+5ns,原來的電路延遲為10ns,能跑的最高頻率為100MHz,而延遲截斷後最高頻率能達到200 MHz。

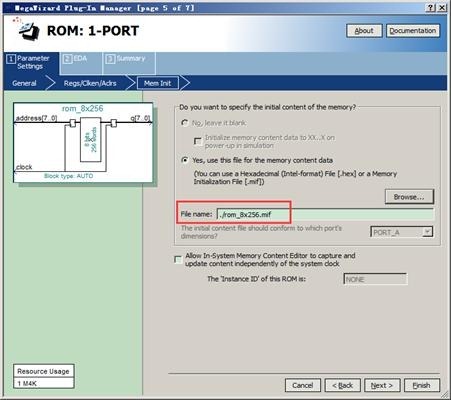

④ 新建一個.hex文件或者.mif文件,將其設置為ROM的初始化文件

圖25 新建mif文件

圖26 填寫mif文件中的數據並保存

圖27 設置mif文件為ROM的初始化文件

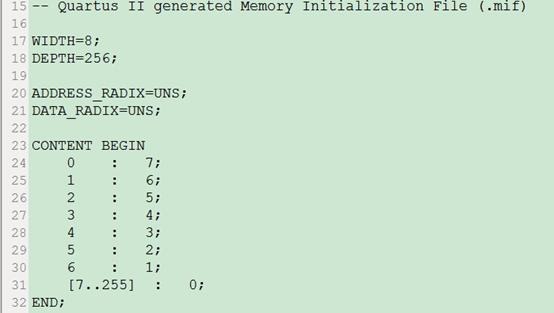

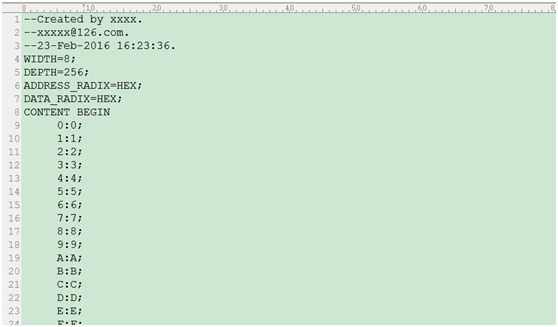

.mif文件中的內容:

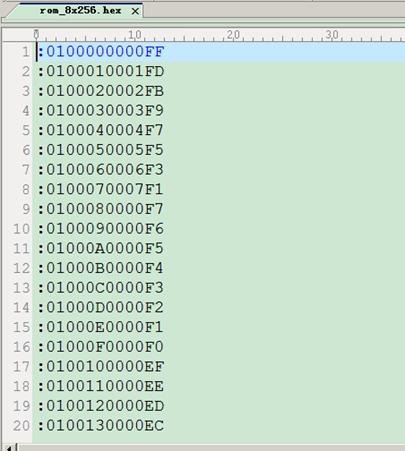

.hex文件中的內容:

對比分析mif文件和hex文件的內部內容可知,mif更加條理清晰、容易用MATLAB產生。故通常採用mif文件來初始化ROM。

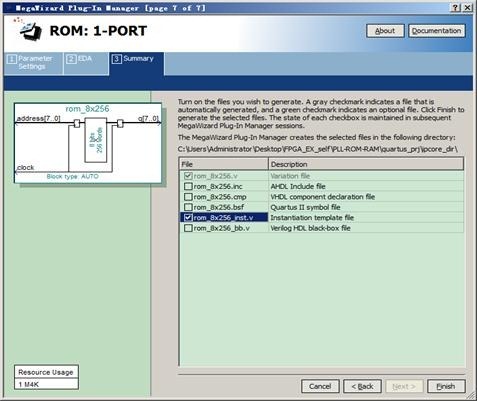

⑤ 設置生成例化文件rom_8x256_inst.v,並添加生成的IP文件到工程中

圖28 設置生成例化文件

⑥ 在頂層模塊ex_ipcore.v文件中添加rom_8x256_inst.v的例化內容,並修改ex_ipcore.v(例化、修改信號埠名稱、添加ROM的地址控制)、tb_ex_ipcore.v(修改例化語句)以及run.do(添加編譯rom_8x256.v文件的語句)中的代碼。

ex_ipcore.v文件:

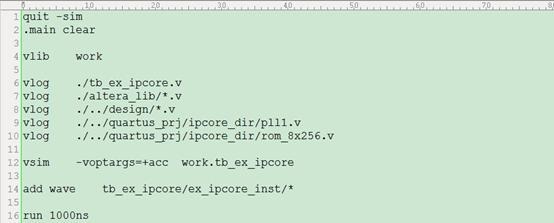

tb_ex_ipcore.v文件:

run.do文件:

⑦ 運行模擬

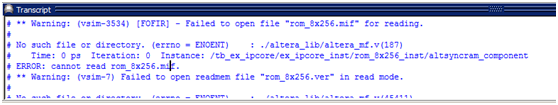

第一次運行模擬時,波形中odata沒有出來數據,一直都是0,查看Modelsim的編譯結果可知,有如下警告提示:

圖29 編譯警告

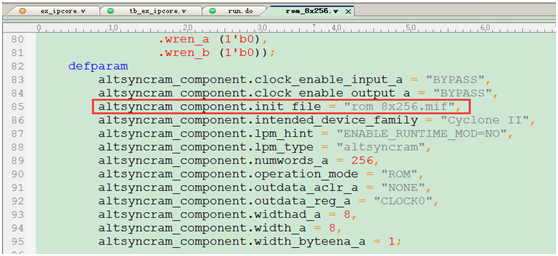

【解釋】因為rom_8x256.v這個文件中有altsyncram_component.init_file = "rom_8x256.mif"這句話,modelsim編譯時會自動地去sim的根目錄下找rom_8x256.mif文件,可是該文件只在PLL-ROM-RAM\quartus_prj\ipcore_dir有,故需要將這個mif文件拷貝到sim的根目錄下去(否則,modelsim無法用mif文件初始化ROM)。

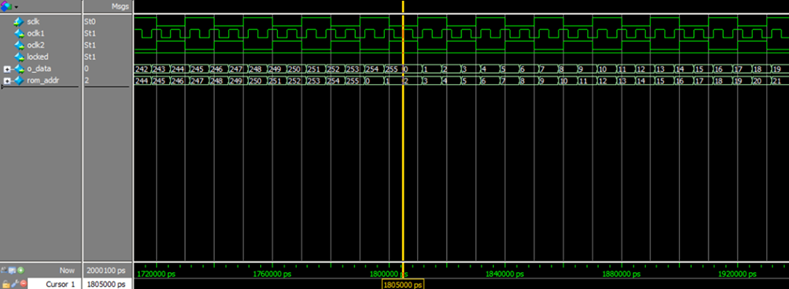

圖30 模擬結果圖

由圖30可知,odata有了數據產生,並且較地址rom_addr有兩個時鐘周期的延遲,是由於在ROM的輸出端加了寄存器造成的,與當初的設想是一致的。

【用MATLAB產生mif文件】

① 在當前工程目錄下新建matlab_sim文件夾,然後將miffile.m文件拷貝到該文件夾中(miffile.m文件的目的是實現miffile(filename,var,width,depth)函數),方便MATLAB程式調用;

② 打開MATLAB,並切換MATLAB的工作目錄到matlab_sim文件夾下;

③ 新建一個MATLAB腳本,命名為gen_mif,並保存到matlab_sim文件夾下;

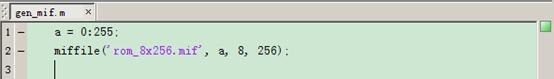

④ 編寫MATLAB的程式代碼:

⑤ 運行gen_mif.m文件後,發現在matlab_sim文件夾下生成了一個rom_8x256.mif文件,其內容如下(與用quartus生成的mif文件基本一致):

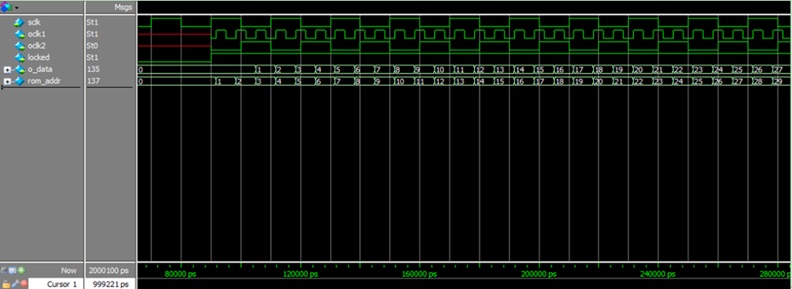

⑥ 將生成的rom_8x256.mif文件拷貝到sim文件夾和ex_6\quartus_prj\ipcore_dir目錄下,替換掉原來的rom_8x256.mif文件,然後重新運行模擬,模擬結果如圖31和圖32所示:

圖31 用MATLAB產生mif文件初始化ROM的模擬圖1

圖32 用MATLAB產生mif文件初始化ROM的模擬圖2

由圖31和圖32可知,ROM的數據範圍為0~255,與mif文件中的數據一致。