[導讀] 前文大致總結了單片機串口的一些值得註意的要點,本文來梳理一下I2C匯流排的一些應用要點。這個題目有點大,對於I2C其實很多地方也沒講清楚,只為了與前文形成系列,如果大家有補充歡迎留言。說了些閑話,進入正題吧。 I2C之前世今生 \(I^2C\)(Inter-Integrated Circui ...

[導讀] 前文大致總結了單片機串口的一些值得註意的要點,本文來梳理一下I2C匯流排的一些應用要點。這個題目有點大,對於I2C其實很多地方也沒講清楚,只為了與前文形成系列,如果大家有補充歡迎留言。說了些閑話,進入正題吧。

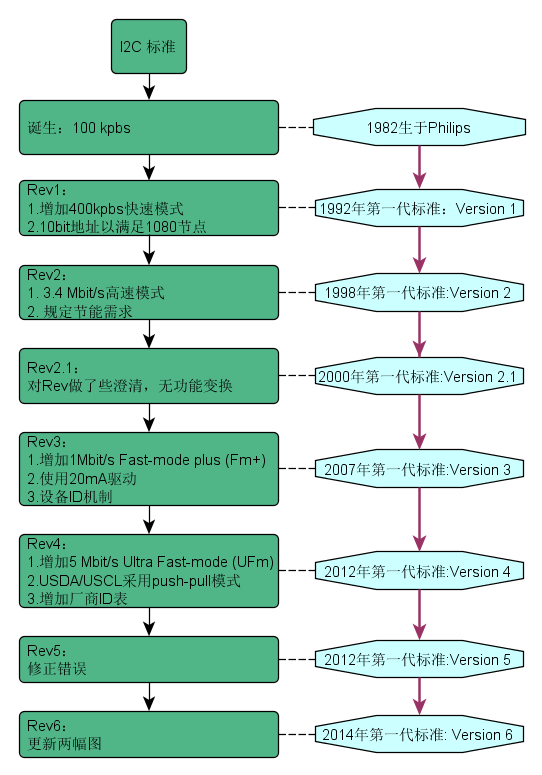

I2C之前世今生

\(I^2C\)(Inter-Integrated Circuit),是一種同步、多主、多從、分組交換、單端、串列電腦匯流排,由飛利浦半導體(現在的NXP半導體)在1982年發明。它廣泛用於在短距離、板內通信中將低速外設集成電路附加到處理器和微控制器上。\(I^2C\)也可以寫成I2C或IIC。

自2006年10月10日起,實施I2C協議不需要任何許可費用。 但是,獲得恩智浦分配的I2C從設備地址需要付費。一些競爭者,如西門子(後來的英飛凌技術,現在的英特爾移動通信)、NEC、德州儀器TI、意法半導體(以前的SGS-Thomson)、摩托羅拉(後來的飛思卡爾,現在與NXP合併)、Nordic半導體和Intersil,自20世紀90年代中期以來已經將發佈了很多相容的I2C標準的晶元。

模式

自Version 4之後 I2C支持下麵幾種模式:

- 雙向匯流排:

- standard-mode(Sm): ≤100 Kbit/S

- Fast-Mode(Fm):≤400 Kbit/S

- Fast-mode Plus(Fm+):≤1Mbit/S

- High-speed mode (Hs-mode): ≤ 3.4 Mbit/s

- 單向匯流排:

- Ultra Fast-mode (UFm): ≤ 5 Mbit/s

好處

I2C標準能帶來些啥好處呢?

- 簡單的2線串列I2C匯流排最小化互連,節省PCB布板走線空間;

- 完全集成的I2C匯流排協議消除了地址解碼器。

- I2C匯流排的多主控能力允許終端用戶設備通過外部連接到裝配線進行快速測試和校準。

- 標準支持廣泛,大量無鉛封裝I2C匯流排相容集成晶元進一步降低了空間需求。

其他子集

系統管理匯流排(SMBus),由Intel在1995年定義,是I2C的一個子集,定義了更嚴格的用法。SMBus的一個目的是促進健壯性和互操作性。因此,現代I2C系統合併了來自SMBus的一些策略和規則,有時同時支持I2C和SMBus,只需要通過命令或輸出引腳使用最小限度的重新配置。

TWI(雙線介面)或TWSI(雙線串列介面)本質上是在Atmel和其他供應商的各種系統晶元處理器上實現的同一匯流排。

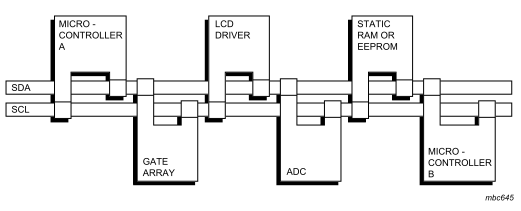

I2C拓撲結構

從概念上,I2C匯流排有兩根線SDA/SCL就可以連一堆晶元,實現很多的應用。連接拓撲極簡!

比如這樣一個系統:

- LCD顯示

- ADC採樣

- EEPROM/FRAM 非易失存儲

- 溫度採集

- .....

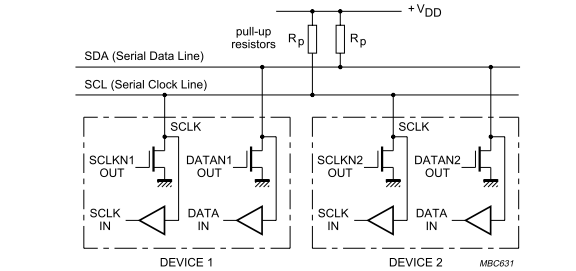

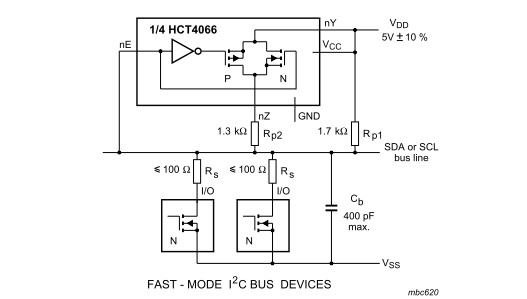

接下來看看各模式下,連接拓撲圖:

標準速度/快速模式:

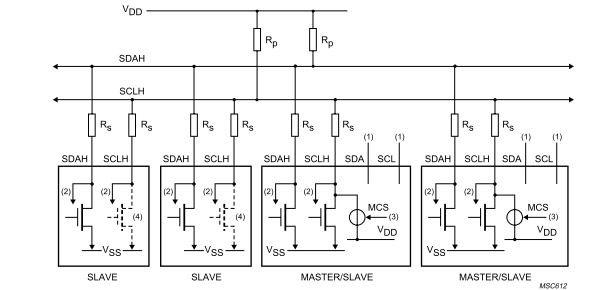

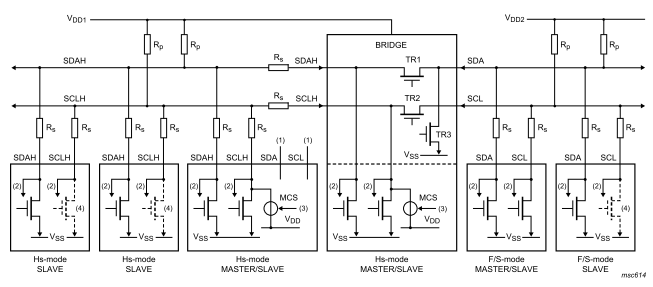

高速模式拓撲:

混速模式拓撲:

工作原理

如果使用IO口模擬I2C匯流排,或者使用FPGA實現I2C介面,深刻理解I2C時序波形無疑是重點中的重點!即使使用內置的I2C控制器外設實現一個I2C匯流排編程,在調試底層時或者踩坑過程中,深入理解時序波形原理,也是非常必要的!

時序圖

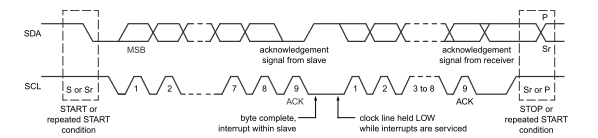

I2C的時序圖如下:

-

START事件:可以聯想一下UART的起始位,這個用於通知I2C通信的發起。用一句話描述就是在SCL常高時,採集到SDA高到低跳變,這就是啟動事件。

-

數據有效性:SDA線上的數據必須在時鐘的高周期保持穩定。數據線的高或低狀態只能在SCL線上的時鐘信號低時改變。每個傳輸的數據位產生一個時鐘脈衝。

-

ACK:確認信號ACK的定義如下:發送器在ACK時鐘脈衝期間釋放SDA線,因此接收器可以將SDA線拉低,併在此時鐘脈衝的高電平期間保持穩定的低電平(見上圖)。須嚴格遵循電氣的建立保持時間,使用時需要用示波器去嚴格測試信號是否能滿足這些參數。

-

NACK:當在第九個時鐘脈衝期間SDA保持高電平時,這被定義為“NACK”信號。 之後主機可以產生停止條件以中止傳輸,或產生重覆的開始條件以開始新的傳輸。 導致NACK產生的條件有五個:

- 匯流排上沒有報文中所包含地址的接收器,因此沒有設備響應應答。

- 接收器無法執行接收或發送操作,比如它正在執行某些實時功能,並且尚未準備好與主機進行通信。

- 在傳輸過程中,接收器收到應用協議不理解的數據或命令。

- 在傳輸期間,接收器無法再接收更多有效數據位元組。比如程式或者晶元內置緩衝區已經滿了

- 主接收器用NACK通知從發送器結束傳輸。這是何意呢?比如主設備已經接受到足夠多的數據,不希望從設備發送更多的數據時,就可以NACK從設備,這樣從設備就會停止發送

時鐘同步與仲裁

-

時鐘同步:兩個主機可以同時開始在空閑匯流排上進行傳輸,並且必須有一種方法來確定控制匯流排並完成其傳輸的方法。 這是通過時鐘同步和仲裁完成的。 在單主機系統中,不需要時鐘同步和仲裁。

時鐘同步是通過I2C介面中SCL線的線與實現的。啥意思呢?

- 當SCL從高到低的過渡時,匯流排上的主機開始計數其低電平時間,且一旦主機時鐘變為低,它就會將SCL保持在該狀態,直到變為高狀態為止。

- 但是,如果另一個主機時鐘仍在其低周期內,則此時鐘從低到高的轉變不會改變SCL線的狀態。 所以,SCL線由主機以最長的低電平周期保持為低電平。 低電平周期較短的主機在此期間進入高電平等待狀態。

- 上面的話不好理解?看看線與的本質是與,啥叫與呢? 比如C=A&B,只要其中一個變數A/B為低,那麼C就必然為0,比如下圖中,即便CLK1(為其中一個主機)為高了,但奈何另一主機的CLK2任然為低啊?所以SCL線上測出來就是低。

- 當所有相關的主機都計數完低電平周期後,時鐘線被釋放並變為高電平。 這樣,主時鐘和SCL線的狀態之間就沒有區別,所有主時鐘都開始計數其高電平周期。 第一個完成其高電平周期的主機將SCL線再次拉低。

這裡的幾句話需要劃重點去理解,這就是I2C匯流排的核心之核心工作原理:線與!

-

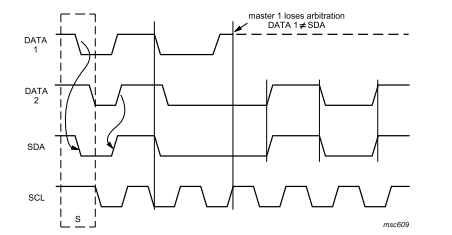

仲裁:仲裁與同步類似,僅在系統中使用多個主機時才會涉及到,從站不參與仲裁過程。首先要理解一下仲裁是幹啥的?所謂仲裁就是在多主機模式下,哪一個主機能獲取介質的訪問許可權,獲得許可權的主機才可以傳輸I2C通信報文。 只有在匯流排空閑時,主機才可以開始傳輸。 兩個主機可以在START的最小保持時間內產生START條件這種情況會導致匯流排上出現有效的START條件。 然後需要仲裁以確定哪個主機將完成其傳輸。

仲裁是一位一位地進行。 節點發送1個位後,回讀比較匯流排上所呈現的數據與自己發送的是否一致。是,繼續發送;否則,退出競爭。SDA線的仲裁可以保證I2C匯流排系統在多個主節點同時企圖控制匯流排時通信正常進行並且數據不丟失。匯流排系統通過仲裁只允許一個主節點可以繼續占據匯流排

上圖顯示了兩個主機的仲裁程式。 實際使用中連接到匯流排的主機數量可能會更多。 當主機產生的DATA1的內部數據電平與SDA線上的實際電平之間存在差異時,DATA1輸出將關閉。 從而主機1退出競爭,沒有獲得匯流排的控制權。

-

時鐘延長:時鐘延長通過將SCL線保持為低電平來暫停事務。 直到再次釋放高電平,事務才能繼續。 時鐘延長是可選的,實際上,大多數從設備不包括SCL驅動能力,因此它們無法延長時鐘。

為啥要設計這樣一個機制呢?個人理解是為了增強系統的健壯性而設計的:

-

在位元組傳輸級別,設備可能能夠以快速速率接收數據位元組,但需要更多時間來存儲接收到的位元組或準備另一個要發送的位元組。此時,從機可以在接收和確認位元組後將SCL線保持為LOW,以強制主機進入等待狀態,直到從機為握手過程中的下一個位元組傳輸做好準備。

-

在位級別上,諸如微控制器之類的設備可以通過延長每個時鐘的LOW周期來減慢匯流排時鐘。 任何主機的速度都將根據該設備的內部工作速率進行調整。

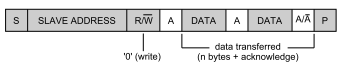

地址及R/W位:

地址及R/W:

- 7位地址:分讀寫兩種情況

-

-

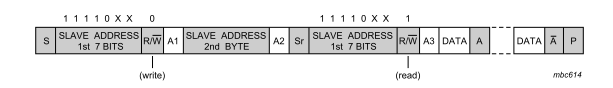

10位地址:分讀寫兩種情況

-

保留地址

| 從設備地址 | 讀寫位 | 描述 |

|---|---|---|

| 0000 000 | 0 | 廣播地址 |

| 0000 000 | 1 | 啟動位元組 |

| 0000 001 | X | CBUS地址 |

| 0000 010 | X | 預留給不同的匯流排格式 |

| 0000 011 | X | 預留未來擴展使用 |

| 0000 1XX | 1 | Hs-mode 主代碼 |

| 1111 1XX | 1 | 設備ID |

| 1111 0XX | X | 10位從地址 |

通用廣播地址

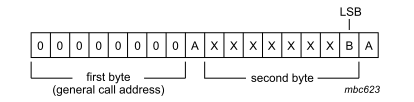

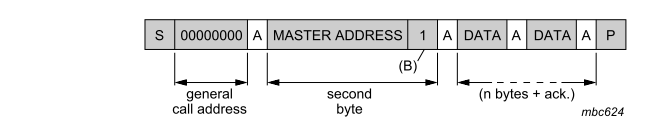

通用廣播地址用於同時定址連接到I2C匯流排的所有設備。 但是,如果設備不需要處理廣播數據,則可以通過不發出ACK來忽略該地址。 如果某設備需要來自通用廣播地址的數據,它將發送ACK給該地址並充當從接收器。 主機實際上不知道有一個或多個設備響應時確認了廣播數據(不確定有多少個ACK)。 每個能夠處理此數據的從機接收器都會確認第二個位元組和隨後的位元組。 無法處理這些位元組的從站將不應答從而忽略。 同樣,如果一個或多個從機應答,則主機不會看到未確認的消息。通用廣播地址的含義總是在第二個位元組中指定,如下圖:

1.當B為0時,第2位元組定義如下:

-

0000 0110(06h):設備將複位以及設置地址的可編程部分。 接收到這個2位元組命令後,所有支持響應通用廣播地址的設備將複位,並將其地址的可編程部分改寫保存。

須採取預防措施以確保設備在施加電源電壓後不會拉低SDA或SCL線,因為這些低電平會阻塞匯流排。 -

0000 0100 (04h):收到該命令後設備將通過硬體設置地址的可編程部分。(Write programmable part of slave address by hardware).

-

0000 0000 (00h): 不允許將此代碼用作第二個位元組.

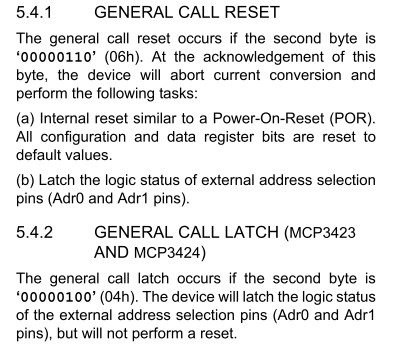

對於06h/04h這兩個命令,有些不太好理解。複位比較好理解。對於設置設備地址的可編程部分可能很多沒有遇到過的朋友則不太好理解。這裡來一個實際晶元的例子,以Microchip的MCP3423/MCP3424為例進行描述一下,MCP3423/MCP3424是一顆多通道ADC晶元,其晶元引腳如下:

當接收到通用廣播訪問且第2位元組為06h命令後,晶元做兩件事情:

- 晶元複位如上電覆位的行為一樣

- 同時鎖住Adr1/Adr0的電平作為地址,這兩位地址為晶元地址的可編程部分。

當然對於不同的晶元,具體如何實現通用廣播地址的處理則各有不同,只需要認真閱讀晶元的手冊就能獲取相應信息。這裡僅僅就通用廣播地址舉個慄子,方便理解。老實說這個功能好像不太常見,具體有什麼用?我反正沒這麼用過,感覺這功能有點蛋疼(直接用電阻配置好不更省事?)。如果有好的應用實例場景,歡迎留言交流。

2.當B為“ 1”時,則該2位元組序列為“硬體通用呼叫”。 該報文由I2C主設備(例如鍵盤掃描器)發送,可以對其進行編程以發送所需的從地址。 由於I2C主設備事先不知道該消息必須傳輸到哪個從設備,故利用通用廣播地址及通用呼叫命令並將自身的地址放在高7位,從而標識匯流排上發送通用硬體呼叫的設備ID。 該地址由連接到匯流排的智能設備識別(比如該智能設備是一個單片機系統),然後該智能設備從硬體主機接收信息。 如果硬體主機也可以充當從機,則從機地址與主機地址相同。

所以標準中定義這個功能,可以做些自適應應用,只需要制定出相應協議就可以完成比較靈活的多主通信應用協議。

軟複位

如上面描述,當通用廣播地址後面跟06h位元組,就可以使從設備軟複位。但這個功能並非所有晶元都支持,具體使用的時候需要仔細閱讀晶元手冊是否支持該功能。

須採取預防措施以確保設備在施加電源電壓後不會拉低SDA或SCL線,因為這些低電平會阻塞匯流排。

起始START位元組

單片機/DSP可以用兩種方法連接到I2C匯流排:

- 有的單片機/DSP具有片上I2C硬體外設,這就可以直接使用。

- 如果沒有或者被其他功能占用,則可以使用GPIO去模擬I2C匯流排時序。用這個方式去實現,則比較消耗CPU時間,

比如在一個多單片機用I2C匯流排連一起的系統,其中一個單片機I2C是用IO口模擬的,則快速的硬體設備與依賴軟體輪詢的相對較慢的單片機之間存在速度差異。這個不難想象,因為依靠輪詢則不是硬實時,同時單片機肯定還有其他事物需要處理,那麼檢測START條件信號就有可能丟失,導致系統不健壯。那麼I2C標準已然考慮這種需求了。

這就是起始位元組需要解決的需求,前面介紹的就是起始位元組設計的背景。那麼起始位元組究竟是怎樣的呢?

- START 事件(英文叫condition,我這樣叫成一個事件有一點軟體原語抽象的意思)

- START位元組0000 0001

- ACK

- 重覆START事件

在需要訪問匯流排的主機發送了START事件之後,發送START位元組(0000 0001)。 另一個單片機/DSP可以以低採樣率對SDA線進行採樣,直到檢測到START位元組中的七個零之一為止。 在SDA線上檢測到此LOW電平後,微控制器可以切換到更高的採樣率,以找到重覆的START事件,然後將其用於同步。

匯流排複位

在異常情況下,如果時鐘SCL被拉為LOW了,則有哪些辦法可以對匯流排複位呢?

- 則優選的做法是如I2C設備具有硬體複位輸入,則使用硬體複位信號來複位匯流排。

- 如果I2C設備沒有硬體複位輸入信號,如果硬體設計可以考慮用MOSFET控制設備電源,重新通電以激活強制性的內部上電覆位(POR)電路。

- 還有一種做法是主機發送9個時鐘SCL脈衝。 使匯流排保持低電平的設備應在這九個時鐘內的某個時間釋放它。這個具體怎麼做呢?主設備初始化I2C匯流排時,可以冗餘加9個SCL脈衝以複位I2C匯流排,或者檢測到SDA長時間被拉低後,可以以控制IO高低翻轉的方式控制SCL產生9個脈衝

//可能需要先關閉I2C控制器,如果是使用I2C控制器外設實現的

//I2C_SCL根據不同硬體進行移植,delay

#define I2C_SCL P10

void soft_rst_i2c(void)

{

I2C_SCL = 1;

for(int i=0;i<9;i++)

{

I2C_SCL = 0;

delay(xx);

I2C_SCL = 1;

delay(xx);

}

}

前面兩種方法是更健壯的方案,如果硬體不支持,可以考慮後一種方法,但後一種方法的前提是拉死SCL的設備需要支持這種功能,如果兩端都是自定義開發的則比較靈活了。

匯流排鎖死,是I2C匯流排系統常踩的坑,有哪些原因會導致鎖死呢?程式不健壯,I2C的波形不滿足I2C規格書要求,或者在外加干擾情況下導致波形被干擾。有經驗的同學可能會遇到設備平時工作的好好的,但是做EMC測試,常常設備會莫名死機,如果你的設備有I2C匯流排,請記得檢查I2C是否被EMC干擾乾死了!

設備ID

設備ID欄位是一個可選的3位元組只讀(24位)字,提供以下信息:

- 12位用於表示製造商名稱,每個製造商唯一(例如,NXP)

- 9位由製造商分配的晶元標識(例如,PCA9698)

- 3位表示晶元版本,由製造商分配(例如RevX)

這個對於設計軟體有什麼可以利用的信息呢?比如一個系統可相容不同廠家的基於I2C協議的感測器,利用這個欄位就可以做設備信息管理。至於怎麼讀取,不同晶元或有不同。

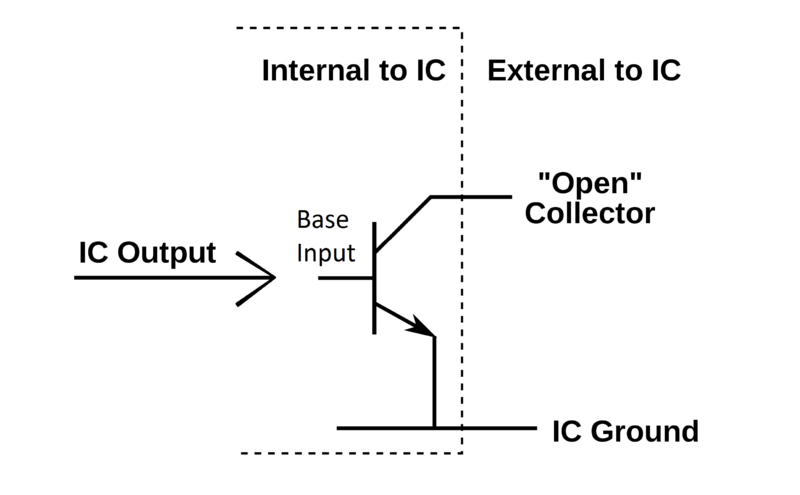

介面電路簡介

前面拓撲圖中採用open-drain 開漏結構。I2C有的還用集電極開路輸出結構,究其原因是內部是三極體的集電極開路。如下

Ultra Fast-mode

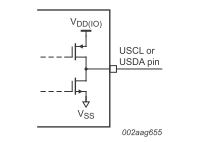

在Rev 4中還出現了Ultra Fast-mode,該模式使用push–pull推輓定義I2C內部硬體介面電路(我把它叫推拉),這個又長什麼樣呢?

這種推輓介面是用在Ultra Fast-mode(UFm)模式,為啥不繼續採用集電極開路門/漏極開路門呢?因為這兩種硬體已然無法滿足如此高速的通訊波形要求了,推輓輸出可以實現更為快速波形前沿特性以驅動匯流排電容負載。

對於Ultra Fast-mode模式其他如時序波形,報文定義基本一致,這裡不做贅述了。需要提醒的是設備ID在該模式下不支持!

容性負載

為什麼要特別討論一下匯流排的容性負載特征呢?想象中的理想通信波形:

由於容性負載以及充放電常數特性,實際中卻可能是這個鳥樣:

如果實際匯流排中電阻選取過大,或者容性負載過大(設備節點過大或者佈線不合理),也即RC常數過大,甚至可能是這個德行:

那麼參數選取合適時,波形則可能是這樣的:

所以就其本質而言,就是由於驅動介面電路的RC參數影響了波形的時序參數:

實際應用中,一方面電阻需要選取足夠大以降低不必要的電流消耗,另一方面電阻又需要選擇足夠小以滿足對應傳輸速度的波形時序要求。故需要在這一對矛盾體中尋求一個折中平衡!實際項目中先用示波器測測I2C波形非常必要,代碼對了匯流排可未必如願工作。做底層開發,儘量先硬後軟~~

I2C匯流排從電氣特性上需要特別註意的是其容性負載特征:

-

Fast-mode:連接到匯流排的外部上拉設備必須經過調整,以適應快速模式I2C匯流排較短的最大允許上升時間。 對於200 pF以內的等效匯流排負載,每條匯流排的上拉設備可以是一個電阻。 對於200 pF至400 pF之間的匯流排負載,上拉設備可以是電流源(最大3 mA)或開關電阻電路。

-

Fast-mode Plus (Fm+):該模式下設備中的驅動介面電路驅動能力比較強大,可以滿足Fast-mode Plus時序規範,並具有與標準模式部件相同的400 pF負載。 為了與標準模式向後相容,它們還可以承受標準模式設備的1μs上升時間。 在僅存在Fast-mode Plus部件的應用中,強驅動介面和對緩慢的上升和下降時間的容忍度允許使用較大的匯流排電容,只要軟體設置好或硬體IC實現好,Fast-mode Plus的最小LOW時間和最小HIGH時間即可滿足所有要求,並且下降時間和上升時間不超過標準模式的300ns上升沿時間和1μs 下降沿時間規格。 可以將匯流排速度與負載電容進行折衷,匯流排電容可增加大約十倍。

-

Hs-mode: 高速模式(Hs-mode)器件在I2C匯流排傳輸速度方面實現了飛躍。 高速模式設備可以實現高達3.4Mbit/s的比特率傳輸速度,但仍然向下相容,與快速模式增強版、快速模式或標準模式(F/S)設備完全相容以進行雙向通信匯流排系統。 除了在Hs模式傳輸期間不執行仲裁和時鐘同步外,與F/S模式系統保持相同的串列匯流排協議和數據格式。那麼如此高速是如何做到的呢?這裡將個人認為與應用相關的要點翻譯總結下:

- Hs模式主設備具有用於SDAH信號的漏極開路輸出緩衝器,以及SCLH輸出上的漏極開路下拉電路和電流源上拉電路的組合。 該電流源電路縮短了SCLH信號的上升時間。 任何時候僅在Hs模式下,僅啟用一個主機的電流源。

- 在多主機系統的Hs模式傳輸期間,不執行仲裁以及時鐘同步以提高位處理能力。 仲裁過程始終在先前的F/S模式下的主代碼傳輸之後完成。

- Hs模式主設備生成串列時鐘信號,其占空比為50%以減輕建立和保持時間的時序要求。這個項目中可利用示波器檢查波形。

-

具體設計時,可參考規格書電氣特性參數規定以及所選晶元的手冊。

編程策略

- 硬體I2C控制器:要實現I2C匯流排,如果使用單片機/DSP/SOC內置了I2C控制器,就其本質就是抽象了I2C匯流排的各種事件以寄存器進行控制,最為常見的方式就是將匯流排事件抽象為非同步中斷事件。以STM32為例:

編程時,比較好的方式就是處理相應的中斷事件。利用內置I2C控制器是優選方案。

- IO模擬,如果系統中不存在I2C控制器,可利用IO口進行模擬,對於實現多設備以及高速模式系統則不推薦這樣做。但在一些PCB尺寸受限或者成本受限、單片機引腳很少的系統中還是比較有實用價值的。其編程只需要對照I2C時序進行操作即可,難度較小。

在實際項目中,需要特別註意I2C的上升沿、下降沿波形時間參數是否滿足設計速率要求,可通過配置寄存器以及調整驅動上拉電阻進行調整。對於高速模式則可能需要用電流源進行驅動。另外需要註意的是,I2C匯流排鎖死情況處理。

總結一下

I2C匯流排是一個比較複雜的晶元間匯流排系統,你或許會用。但是如果不註意標準的很多細節,你可能無法用好!尤其匯流排上掛很多設備時,系統極可能不健壯!本文主要參考I2C version標準,I2C匯流排看似簡單卻極為複雜,本文總結了規格書中一些要點,也並不全面。在複雜應用場景中,還需要多多踩坑、填坑並加以總結。前文談到了對於技術要點儘量總結、概括以及提煉,這裡想提醒的是一些技術要點的標準往往是最為嚴謹、也最為全面的總結。具體使用時,可多多研讀。

I2C VERSION6規格書可至www.i2c-bus.org下載,也可以至公眾號後臺回覆I2C6,可直接領取。

文章出自微信公眾號:嵌入式客棧,版權所有,嚴謹商用,更多內容,請關註本人公眾號